一、关于PCIe TLP排序机制的介绍

与其他协议一样,当同一个通信等级(Traffic Class, TC)的多个事务(Transactions)同时通过同一个通道时,PCIe对这些事务设置了一些排序(Transaction Ordering)规则。

这样做的好处有以下几点:

- 保持与传统总线的兼容性。比如PCI,PCI-X等;

- 保证事务的完成具有准确性,并且按照设计人员的意愿完成;

- 避免死锁的状况发生;

- 最大限度的优化PCIe总线的传输效率。

注释:死锁是指两个以上的设备在访问临界资源时,相互等待对方释放这些资源,而无法访问这些资源的情况。

在PCI总线上,只支持Strong Ordering传送规则,而在PCIe总线中新增了Relaxed Ordering(RO) 和 ID-based Ordering(IDO)传递方式。

Strong Ordering:

何为Strong Ordering? 顾名思义,Strong,就是很强壮,很彪悍的意思。Strong Ordering强制总线上的TLP按照先来后到的方式进行传递,一视同仁,不管是否有特殊情况,均不允许插队和绿色通道。但是事情总有轻重缓急,对于一些紧急的状况,这个强制规则难免会影响到总线的传递效率和用户体验。

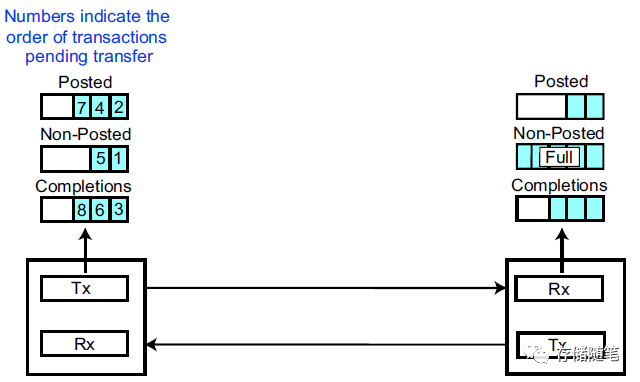

我们看下面一个例子,

- 所有的TLPs类型统一编号;

- 发送端VC buffer有8个待传输的TLPs,依次编号为#1~8,这8个TLPs分为三类:Posted:2, 4, 7;Non-Posted: 1, 5;Completions: 3, 6, 8;

- 接收端对应的VC buffer如上图,其中,Non-Posted buffer已满,而Posted、Completions buffer则仍有可用空间;

此时,接收端Non-Posted buffer已满,TLP 1,5则需要暂停发送。由于这8个TLPs属于同一VC,需要按照Strong-Ordering规则排序。所以TLP 2,3,4对应接收

本文分析了PCIe TLP排序机制,尤其是Relaxed Ordering如何影响系统性能和稳定性。虽然RO可以提高传输效率,但在PCI-to-PCI、共享内存架构等场景下可能导致数据错误和系统故障,如网卡降速、FPGA TLP错误、NVME驱动报错等。正确评估系统需求并谨慎使用Relaxed Ordering至关重要。

本文分析了PCIe TLP排序机制,尤其是Relaxed Ordering如何影响系统性能和稳定性。虽然RO可以提高传输效率,但在PCI-to-PCI、共享内存架构等场景下可能导致数据错误和系统故障,如网卡降速、FPGA TLP错误、NVME驱动报错等。正确评估系统需求并谨慎使用Relaxed Ordering至关重要。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

423

423

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?