此前小编关于QLC SSD有过多篇文章,具体参考如下:

最近看到一篇厦门大学最近发表的关于QLC SSD无效编程的论文,有很多非常有意思的数据对比,这里分享给大家。存储随笔的论文解读,不是直接翻译,是小编先研读一遍后,再结合自己的理解再解读分享,可能讲述顺序与原始论文架构可能会有差异,如果不当之处,还望见谅。想直接阅读原文的朋友也可以后台私信关键词【invalidQLC】获取论文。也欢迎各位朋友给小编推荐更多有趣的论文!

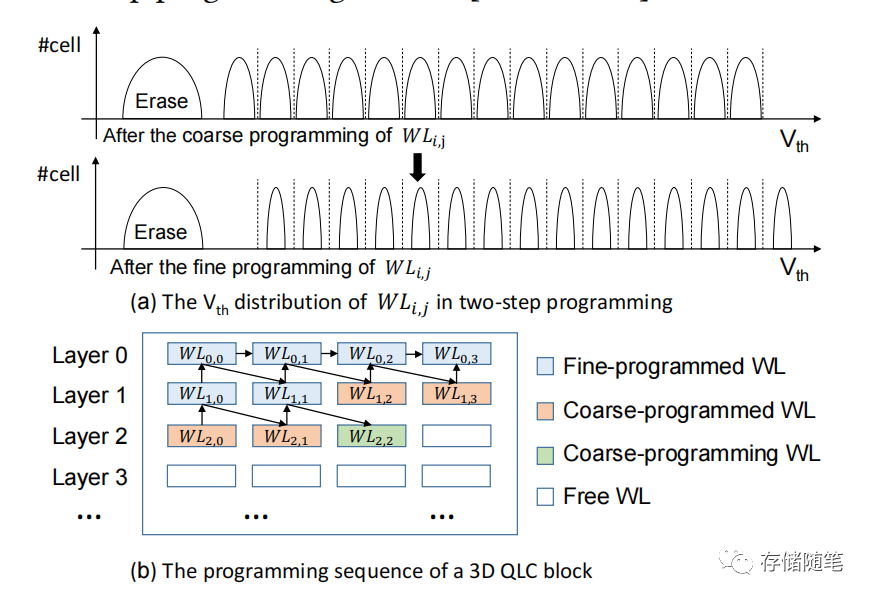

在QLC闪存中采用的两步编程方法是为了应对高密度存储带来的挑战。QLC NAND闪存是一种每单元可存储4比特数据的存储技术,它将阈值电压细分为16个电压状态以实现这一目标。然而,由于每个电压状态分布非常窄且紧凑,相邻单元之间的编程干扰和早期电荷损失会对最终编程电压分布产生显著影响,从而导致高比特错误率。

为了解决这个问题,3D QLC NAND闪存采用了两步编程策略:

-

粗略编程(Coarse Programming):首先对某一层中的一个字线(WL)进行粗略编程,将单元编程到比目标电压稍低的16个电压级别中。这个阶段的主要目的是快速地将数据写入闪存单元,但由于相邻单元间的影响,实际写入的电压可能与目标电压存在一定的偏差。

-

精调编程(Fine Programming):在完成同一层下一个字线或下一层对应字线的粗略编程之后,再返回来对先前粗略编程过的WL进行精调编程,将单元精确地编程到最终的目标电压状态。这种过程能够减少相邻单元间的编程干扰,并允许更准确地控制单元的电压水平,从而提高数据的可靠性。

通过这种方式,虽然牺牲了一定的编程速度和增加了操作复杂性,但有效缓解了QLC NAND闪存中由于电压状态过多而引发的程序干扰问题,提高了整体的数据稳定性和存储系统的寿命。

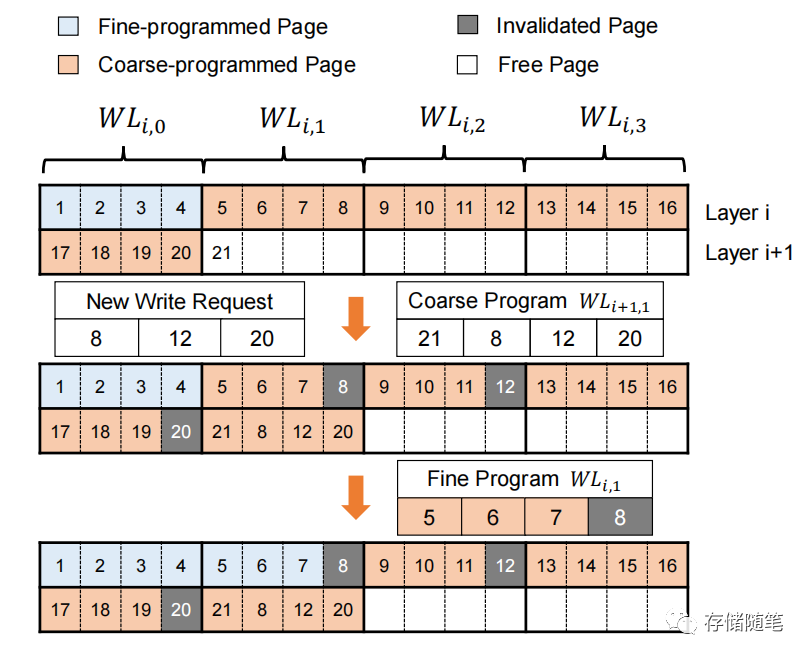

Invalid-Programming Issue无效编程问题在3D QLC NAND闪存中,源于其采用的两步编程机制。具体来说,在该机制中,对某一层的一个字线(WL)进行精调编程之前,必须等待下一层对应位置的字线完成粗略编程。这种顺序要求导致了同一WL两次编程步骤之间存在一段实质性的等待时间。

假设数据被写入WL𝑖,1并存储在缓存中,为了执行WL𝑖+1,1的粗略编程,需要缓存四个页面的数据。假定页面21已被写入缓存,并且有三个已粗略编程的新页面(8, 12, 20)现在又被更新。这会导致这三个页面在其对应的WL上失效,它们将与页面21一起被编程到WL𝑖+1,1。之后,WL𝑖,1可以进行精调编程,并从缓存中移除。但在WL𝑖,1的精调编程过程中,有一个页面已经无效,但所有四个页面都被进行了精调编程。这种情况会发生在其他字线上,第二次编程步骤中的无效页面数量可能不止一个。

这一问题的核心在于,在两次编程步骤之间的时间间隔内,原本在缓存中等待精调编程的数据由于新的写入请求而被更新,即变为无效数据,但是按照原有的编程流程,这些无效数据依然会被进行精调编程,造成了时间和能源的浪费。

文章探讨了厦门大学的研究论文中,QLCNAND闪存采用的两步编程策略如何导致无效编程问题,特别是在3D结构中,编程顺序限制可能导致数据失效和资源浪费。通过分析编程流程,作者揭示了这一问题并强调了优化的重要性以提高数据稳定性和存储效率。

文章探讨了厦门大学的研究论文中,QLCNAND闪存采用的两步编程策略如何导致无效编程问题,特别是在3D结构中,编程顺序限制可能导致数据失效和资源浪费。通过分析编程流程,作者揭示了这一问题并强调了优化的重要性以提高数据稳定性和存储效率。

541

541

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?