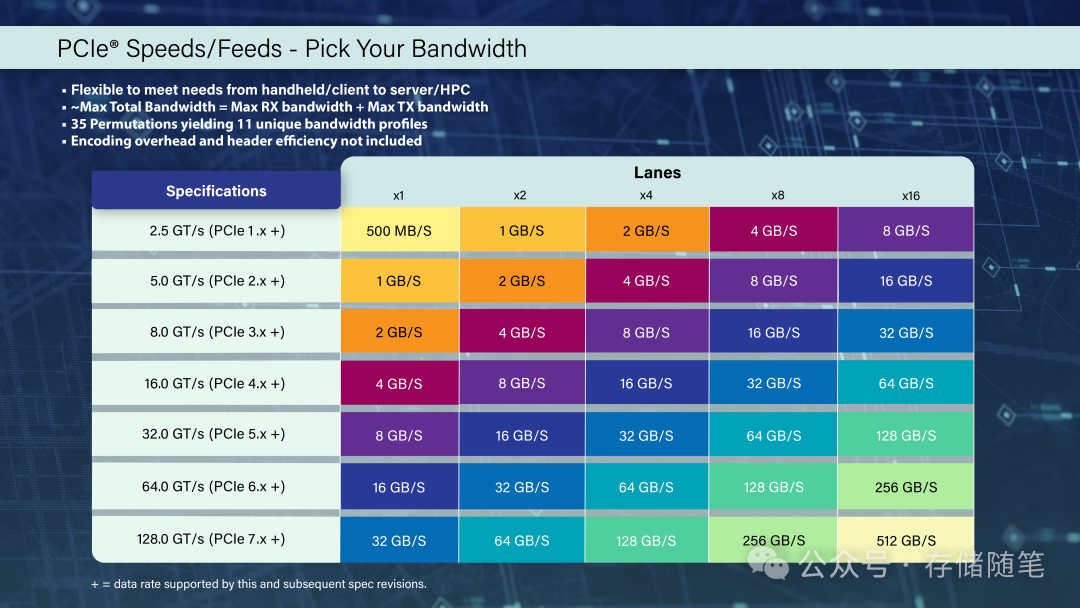

作为业界广泛采用的高速串行点对点互联标准,PCIe自诞生以来历经多次迭代升级,现已成为CPU、GPU、FPGA、SSD等计算设备间不可或缺的互连桥梁。PCIe 7.0标准更是将数据传输速率提升至令人惊叹的32 GB/s(每通道)。

PCI-SIG在2022年6月的美国开发者大会(US DevCon)上宣布了PCI Express 7.0规范的持续进展。2023年6月发布版本0.3,2024年4月份发布0.5版本。最新进展,PCIe 7.0 ver0.9版本已经开放,算是Final Draft了,不出意外,正式版本SPEC规范也将在2025年内部发布。

尽管PCIe 7.0规范的最终版本预期将在2025年内面世,但由于研发、测试及制造过程中遇到的各种障碍,实际产品可能需要更长时间才能广泛普及。

PCIe 7.0 的关键特性目标

-

带宽翻倍:

-

-

PCIe 7.0旨在将PCIe 6.0的传输速率(64 GT/s)提升一倍至128 GT/s的原始比特率,并通过x16配置提供高达512 GB/s的双向传输速度。这代表了数据吞吐量的一次重大飞跃,对于需要处理大量数据的应用至关重要。

-

-

采用PAM4信号技术:

-

-

继续使用并优化自PCIe 6.0引入的Pulse Amplitude Modulation with 4 levels (PAM4)信号技术,该技术允许每个时钟周期编码两个数据位,从而有效地提高了数据传输效率。

-

-

关注通道参数和可达性:

-

-

在设计中注重物理层的通道性能,确保信号在更长距离上的完整性,这对于数据中心内部的互联尤其重要。

-

-

持续提供低延迟和高可靠性:

-

-

确保数据传输不仅速度快,而且延迟极低、可靠性极高,这对实时应用如人工智能/机器学习(AI/ML)和云计算等非常重要。

-

-

提高能效:

-

-

随着设备性能的增强,能效问题变得越来越关键。PCIe 7.0致力于减少能源消耗,使数据中心和其他高性能计算环境更加环保和经济。

-

-

保持向后兼容性:

-

-

尽管引入了许多新技术,但PCIe 7.0仍然支持所有先前版本的PCIe技术,这意味着现有硬件投资可以得到保护,同时也能平滑过渡到新一代标准。

-

扩展阅读:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2496

2496

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?