版权声明:本文为CSDN博主「徐晓康的博客」的原创文章,原文链接:https://blog.csdn.net/weixin_42837669/article/details/107829499

前言

Vivado自带的仿真工具Vivado Simulator使用体验不佳,使用当前最流行的Verilog仿真工具Modelsim更加高效便捷。Vivado支持多种第三方仿真工具,包括Modelsim,Questasim等,本文将介绍如何在Vivado中使用Modelsim进行仿真。

不同版本的Vivado需要搭配对应版本的modelsim,否则在运行仿真时会报错:

WARNING: [Vivado 12-5495] Detected incompatible modelsim simulator installation version ‘2019.4’! The supported simulator version for the current Vivado release is ‘10.6c’.

之前我在Vivado 2018.3中使用Modelsim 2019.4,就会报版本不兼容的错误,提示支持的Modelsim版本是10.6c。实测Vivado 2018.3 + Modelsim 10.6e也完全OK。

具体Vivado版本对应的Modelsim版本可参考xilinx官网:

Vivado Simulation-主要的Vivado Design Suite版本支持的第三方模拟器

Vivado与Modelsim软件下载可参考我的专栏:软件安装

Vivado 2020.2+ Modelsim SE 2020.4 联合仿真,具体步骤如下:

一. 编译Vivado仿真库

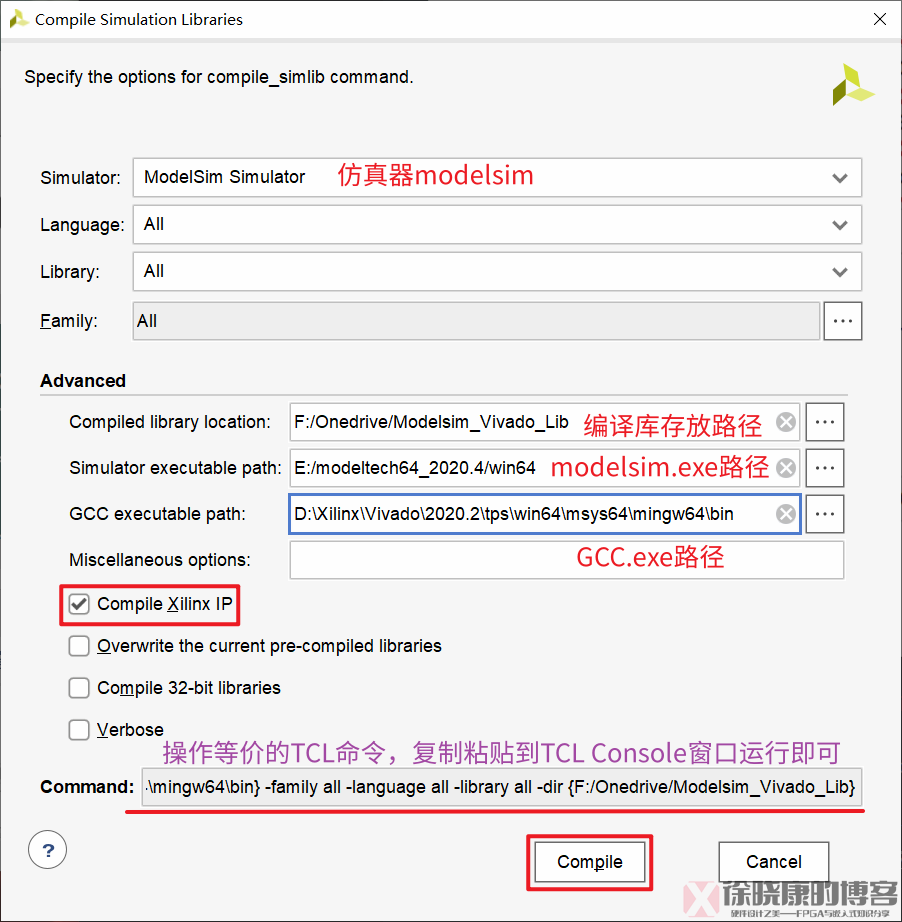

打开Vivado,Tools -> Compile Simulation Libraries

勾选Compile Xilinx IP,此选项表示此次将会编译Vivado中所有的Xilinx IP,以后使用IP时不需要再次编译

注意:

1.这里的指定GCC可执行文件路径是Vivado 2020.2版本新加入的,Vivado 2018.3中没有这部分。此GCC路径不能不填,否则会有如下提示:

2.指定GCC路径是用作编译SystmC IP用的,如果没用到SystemC IP,可随意指定一个路径,例如桌面C:\Users\xu\Desktop,也可以进行编译。

3.推荐的做法是指定GCC路径为D:\Xilinx\Vivado\2020.2\tps\win64\msys64\mingw64\bin,这是Vivado自带的GCC.exe文件,指定此路径没什么问题。

4.Command中会有TCL命令,复制此命令到Tcl Console窗口中运行和设置完点击Compile效果相同。

点击Complie,等待编译完成。在左下角的Tcl Console窗口可以看到编译过程,编译时间和编译结果。编译耗时取决于电脑处理器性能,我的AMD Ryzen 7 3800X用了27分钟才编译完。编译完成后TCL窗口会显示下图所示表格,注意检查是否有Error,有个别error也不要紧,出错的IP可能根本用不上。

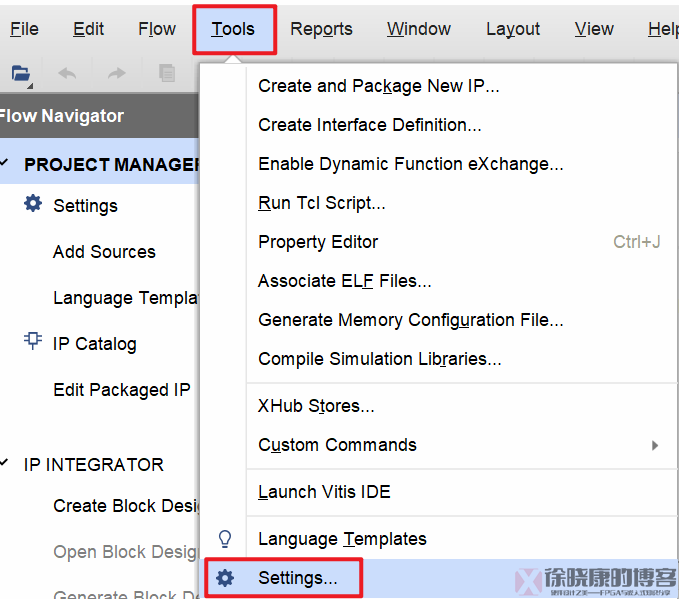

二. 设置仿真工具和库路径

因为新建工程的默认仿真工具是Vivado Simulator,所以要使用Modelsim仿真,每个新工程都要设置一次,方法如下:

三. 启动modelsim仿真

设置完成后,在vivado中点仿真会自动调用modelsim。Run Simulation -> Run Behavioral Simulation

如果仿真一直卡在上图所示界面而不打开modelsim窗口,可能是仿真出错了,注意检查Tcl Console窗口看是否有error。

如果没有Error,将会打开ModelSim窗口,如下图所示。

三. 另外需要注意的点

3.1 不需要新增环境变量

网上说要配置这个环境变量, 实测是不需要的(win10系统), 而且设置了这个变量后, Modelsim原本安装路径中的modelsim.ini文件被代替了, 这不是我们要的. 故这一步不需要做。

变量名:MODELSIM

值(编译库所在位置下的modelsim.ini文件):F:\Modelsim_Vivado_Lib\modelsim.ini

3.2 编译库路径更改后需要修改modelsim.ini

如果你不想编译库而把别人编译好的库拷贝过来,需要注意不仅要在Vivado中指定库路径,还需要更改库文件夹中的modelsim.ini文件,这个文件是编译库时生成的,它指定了特定的库文件路径,注意改成现在库文件的路径。

之前的库放在E盘,现在换到了F盘,需要修改此modelsim.ini文件中的路径才能让Vivado正确调用Modelsim。

徐晓康的博客持续分享高质量硬件、FPGA与嵌入式知识,软件,工具等内容,欢迎大家关注。

6558

6558

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?