#学习记录#

1 38译码器概述

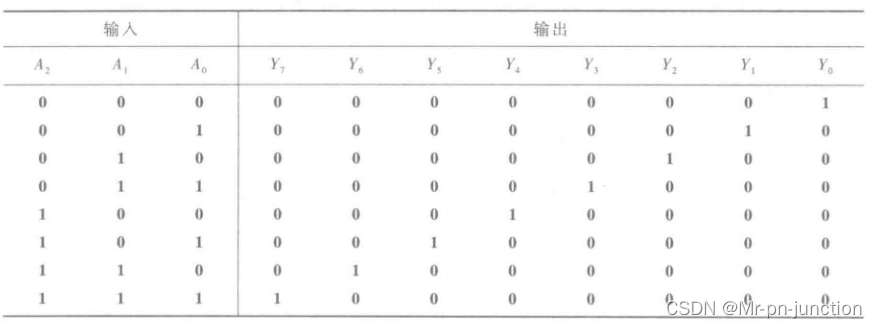

38译码器:输入的3位二进制代码共有8种状态,译码器将每个输入代码翻译成对应的一根输出线上的高低电平信号。38译码器的框图如图1所示,真值表如图2所示。

图1 38译码器框图

图2 38译码器真值表

2 Verilog 描述38译码器

2.1 代码示例

`timescale 1ns / 1ps

//

// Company:

// Engineer: Mr-pn-junction

//

// Create Date: 2023/09/22 08:07:42

// Design Name:

// Module Name: decoder_38

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module decoder_38(

input wire [2:0] data_in,

input wire [2:0] en,

output reg [7:0] data_out

);

always @(*) begin

if(en[0]||en[1]||!en[2])

data_out = 8'b11111111;

else

case(data_in)

3'b000 : data_out=8'b11111110;

3'b001 : data_out=8'b11111101;

3'b010 : data_out=8'b11111011;

3'b011 : data_out=8'b11110111;

3'b100 : data_out=8'b11101111;

3'b101 : data_out=8'b11011111;

3'b110 : data_out=8'b10111111;

3'b111 : data_out=8'b01111111;

endcase

end

endmodule

2.2 testbench

`timescale 1ns / 1ps

//

// Company:

// Engineer: Mr-pn-junction

//

// Create Date: 2023/09/22 10:31:12

// Design Name:

// Module Name: de_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module de_tb();

reg [2:0] data_in;

reg [2:0] en;

wire [7:0] data_out;

decoder_38 tb(

.data_in(data_in),

.en (en),

.data_out (data_out)

);

initial begin

en = 3'b100; data_in = 000;

#5

en = 3'b100; data_in = 001;

#5

en = 3'b100; data_in = 010;

#5

en = 3'b100; data_in = 011;

#5

en = 3'b100; data_in = 100;

#5

en = 3'b100; data_in = 101;

#5

en = 3'b100; data_in = 110;

#5

en = 3'b100; data_in = 111;

#5

en = 3'b101; data_in = 000;

end

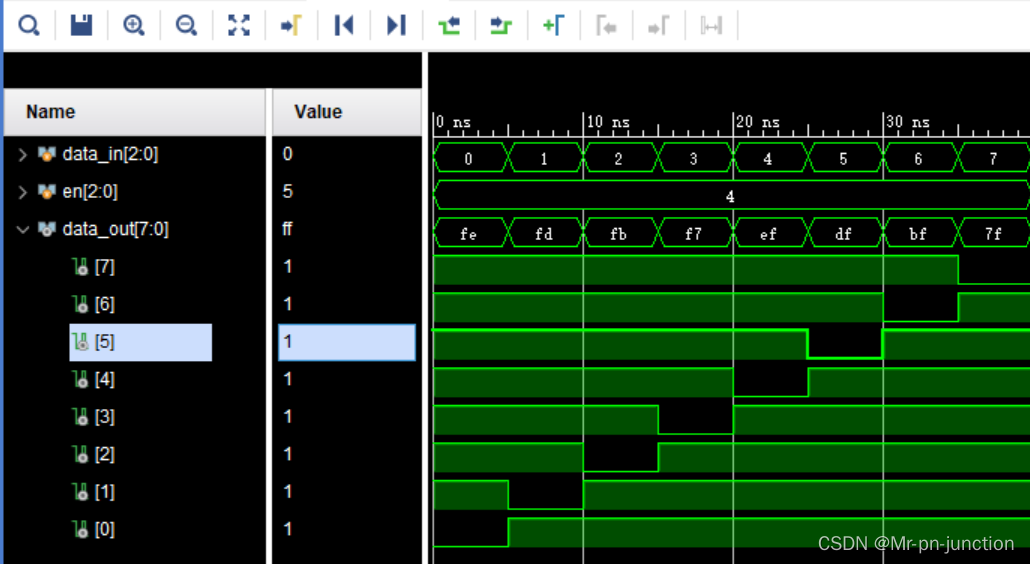

endmodule3 仿真结果

图3 仿真结果

参考文献

[1] 数字电子技术第六版. 清华大学电子学教研组.高等教育出版社. 2016-04.

1081

1081

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?