1 通用D触发器

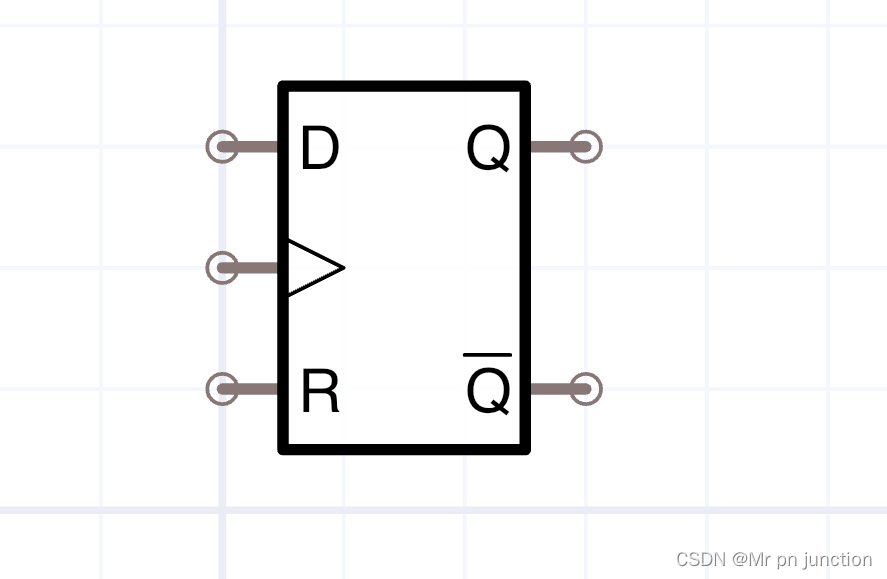

D触发器有数据、时钟和RST输入端以及Q和!Q两个输出端。在每一个时钟的上升沿,输出Q将与输入的D锁存,直到下一个时钟上升沿到来才继续锁存当前的D端数值!Q与Q的输出结果 相反。图1给出了D触发器的符号,图二给出了D触发器的电路,图三给出了D触发器的输入/输出时序。

图一 D触发器符号

图二 D触发器电路

图三 D触发器的时序图

2 Verilog 描述D触发器

2.1 代码描述

`timescale 1ns / 1ps

// Create Date: 2023/09/20 16:51:54

// Design Name: Mr-pn-junction

// Module Name: D_tragger

module D_tragger(

input wire d,

input wire clk,

input wire rst_n,

output reg q,

output wire q_n

);

always @(posedge clk or negedge rst_n) begin

if(rst_n == 1'b0) begin

q<=0;

end

else begin

q<=d;

end

end

assign q_n = ~q;

endmodule2.2 testbench

`timescale 1ns / 1ps

// Create Date: 2023/09/21 08:15:04

// Design Name: Mr-pn-junction

// Module Name: tb_D_tragger

module tb_D_tragger();

reg clk;

reg rst_n;

reg d;

wire q;

wire q_n;

initial begin

clk = 1'b0;

rst_n = 1'b0;

d = 1'b0;

#20

rst_n = 1'b1;

end

always #10 clk = ~clk;

always #24 d = ~d;

D_tragger tb(

.clk(clk),

.rst_n(rst_n),

.d(d),

.q(q),

.q_n(q_n)

);

endmodule3 时序仿真图

图4 Verilog时序仿真

参考文献

[1] Verilog高级数字系统设计技术与实例分析. Kishore Mishra. 电子工业出版社.

3816

3816

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?