#学习记录#

1 创建文件

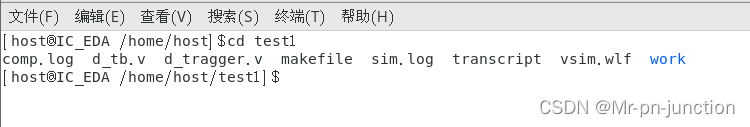

首先我们新建一个目录mkdir test1用来存放设计文件,打开test1如图1所示。创建d_tragger.v d_tb.v以及makefile。  图1

图1

2 编写代码

d_tragger.v与d_tb.v复制这篇文章:Verilog D触发器-CSDN博客。makefile脚本的编写方式如图2所示。vlib work前面必须是Tab键。

图2

3 仿真

输入make all命令执行makefile中的命令,执行完之后产生vsim.wlf文件如图3所示。用命令vsim vsim.wlf&打开vsim.wlf。

图3

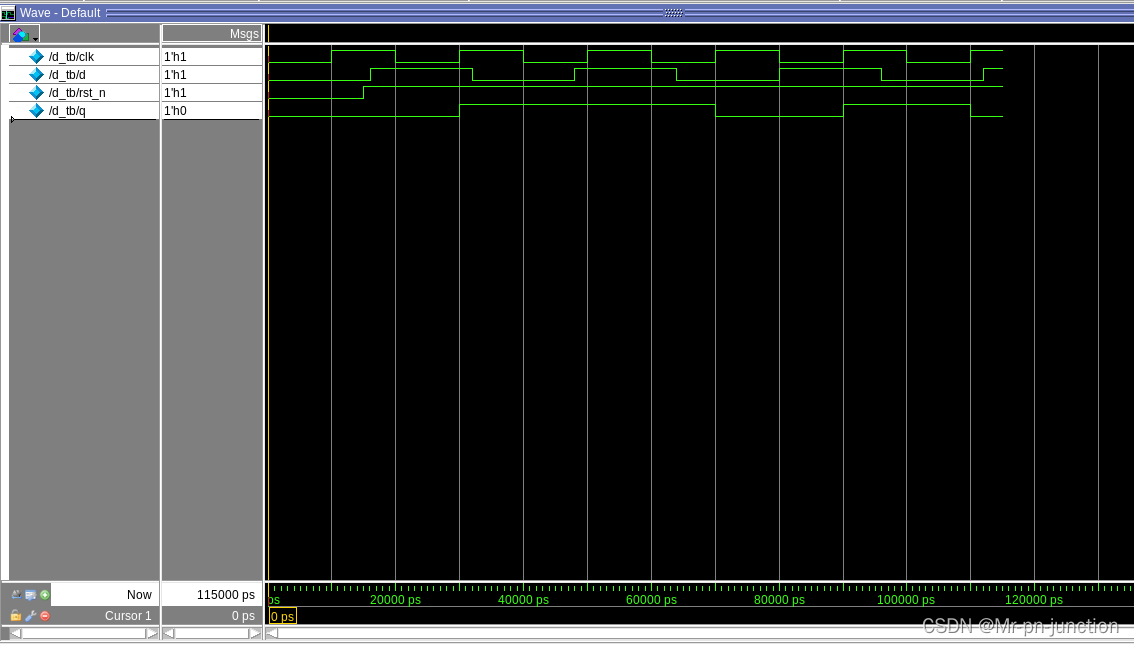

打开Questasim,将信号添加至wave中产生如图4所示波形。验证d触发器

图4

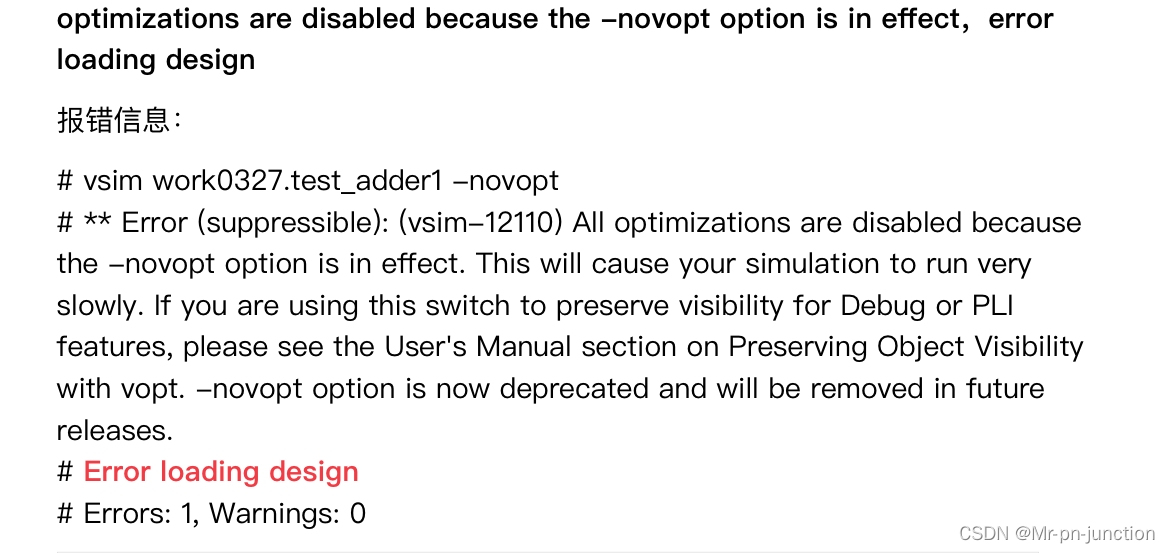

Questasim仿真优化加速问题

原因:modelsim10.7版本之后都不再使用-novopt

设置仿真优化的方法:

1、vsim选项:采用-voptargs="+acc"替换-novopt,避免“vlog-12110”报错,如图2所示。

2、modelsim.ini修改:找到所有的modelsim.ini,将voptFlow = 1。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?