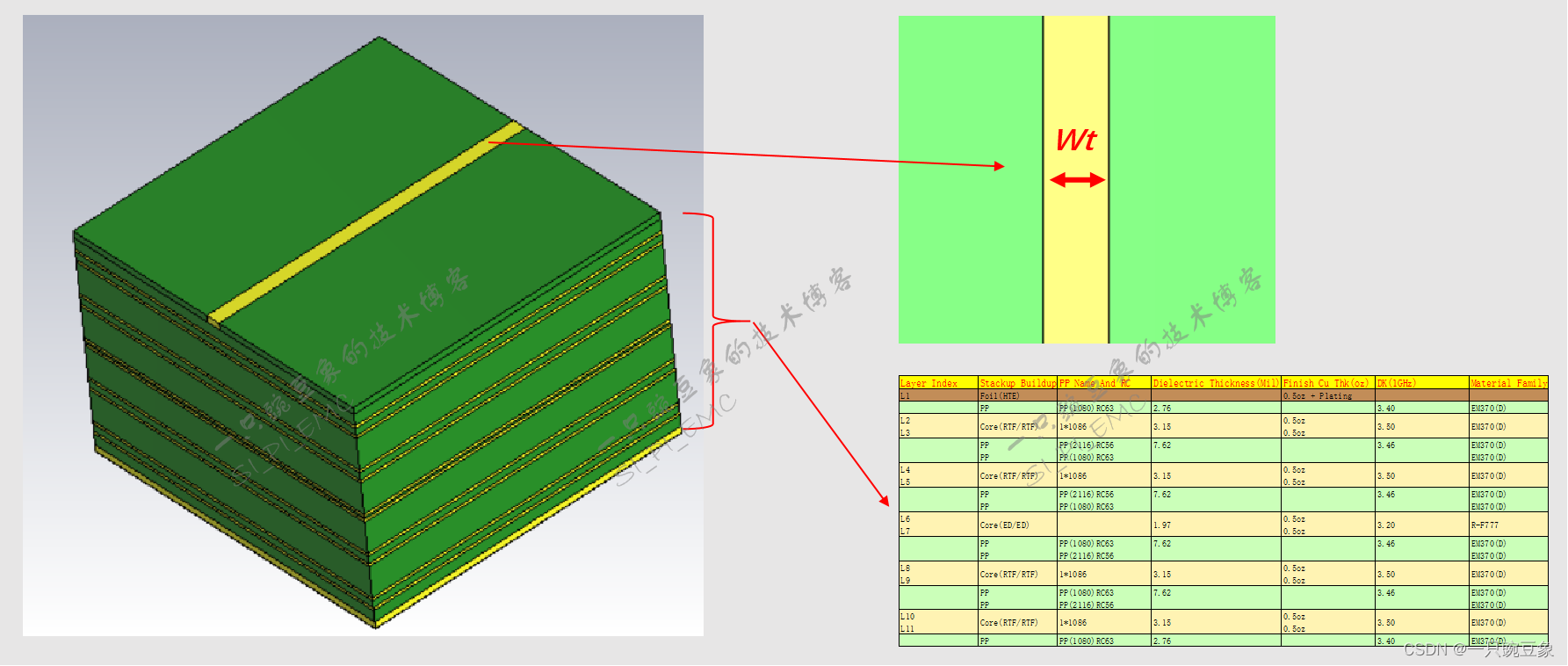

高速信号走线的特性阻抗,需要按照实际要求进行精度控制,所以,任何因设计因素带来的阻抗波动都应该进行优化,如下图所示,为一个12层板设计中的50Ω微带走线,需要在走线之上放置电感。

但是,电感焊盘的使用,导致在原有叠构中,不能保证信号线50Ω阻抗设计要求,因此,需要进行PCB设计优化。

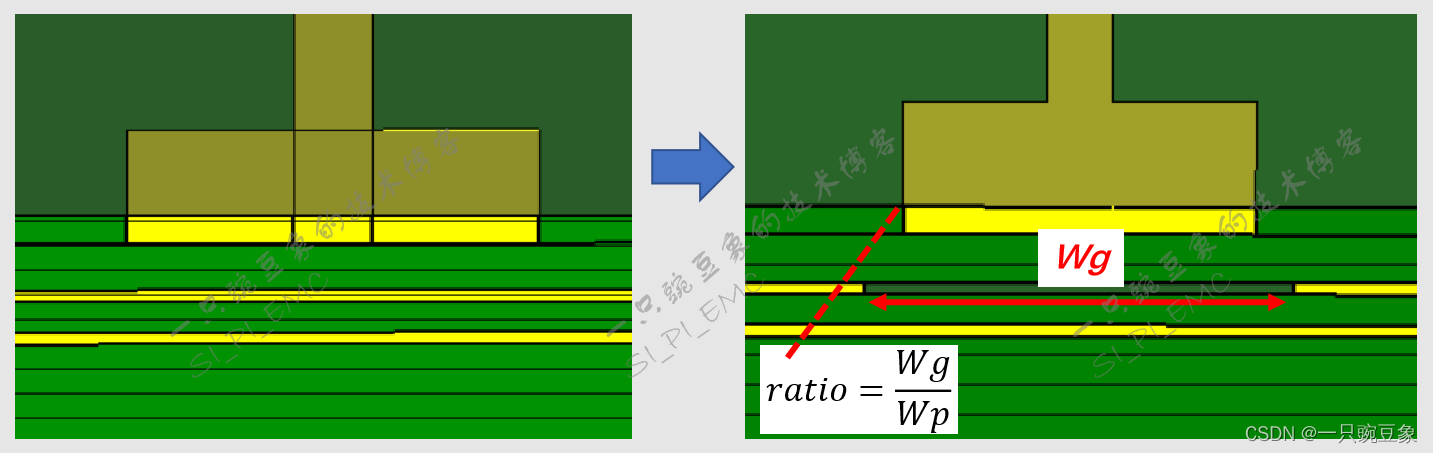

控制焊盘阻抗的有效办法,是挖空其正下方的金属参考面,如下图所示,通过控制挖空区域的宽度以及层数,达到有效控制阻抗的目的,结合上一张图中的Wp与下图中的Wg,定义了比例值ratio,用于设计优化的尺寸控制。

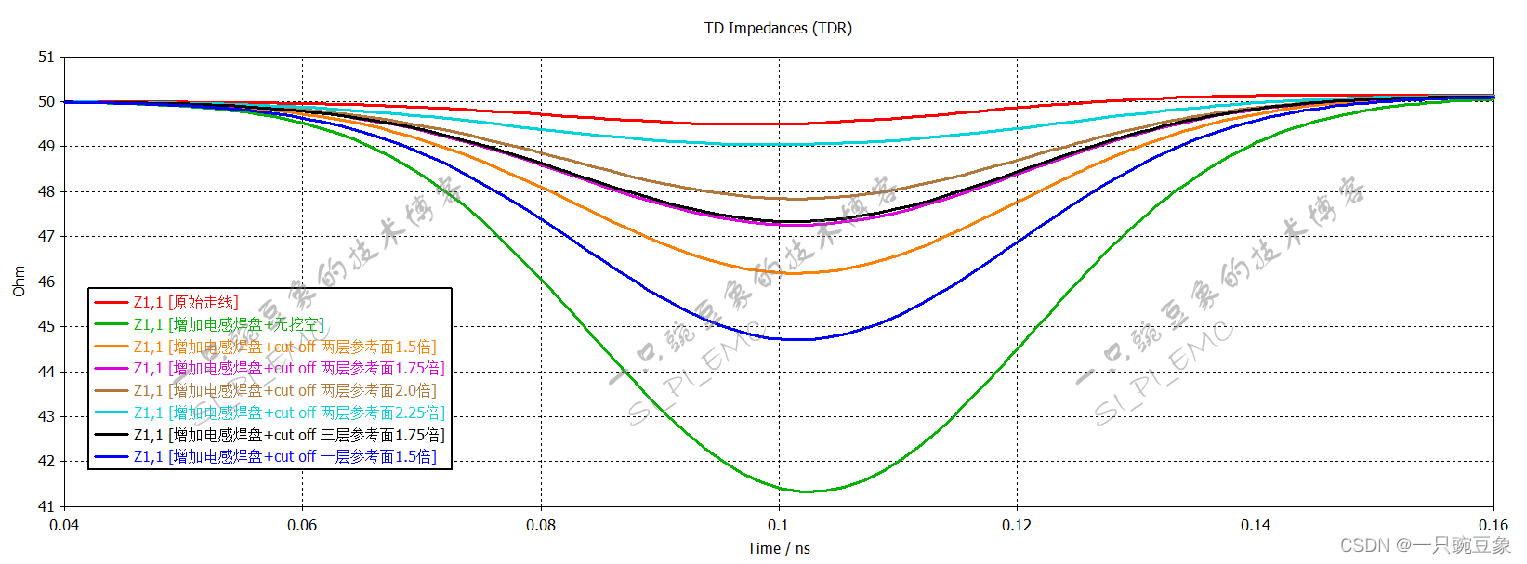

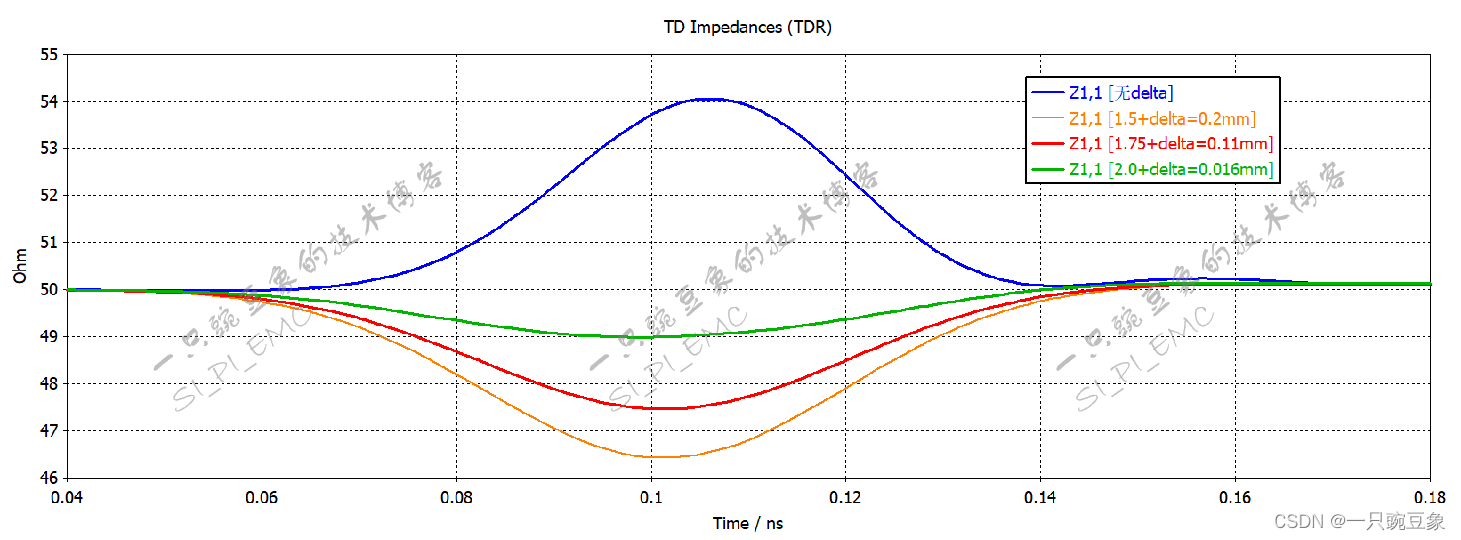

通过下图的阻抗结果对比,可以得到控制焊盘阻抗的一般规律:

1. 挖空区域的宽度以Wg≥1.75*Wp为宜;

2. 调整挖空参考面的层数是另一个有效的方式,但是,需要注意参考面间的介质厚度,如果介质厚度很薄,同时挖空相邻两层参考面会效果显著,反之,则没有必要,需要视具体设计而定。

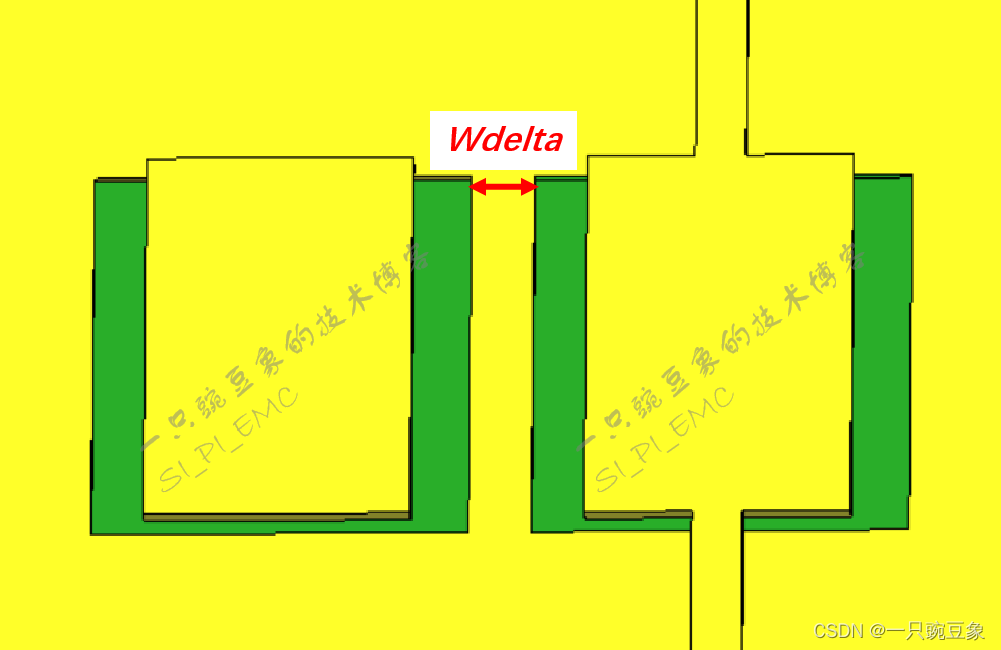

虽然主要关注的是信号线上焊盘的阻抗控制效果,但对于电感相邻焊盘之间敷铜的处理,同样会影响到阻抗控制结果,如下图所示,需要控制电感封装焊盘之间预留参考层的宽度-Wdelta;

仿真结果显示,相邻焊盘之间的参考面会直接影响阻抗:

1. 如蓝色线所示,直接整体挖空参考面是不可取的;

2. 需要配合前述仿真得到的挖空区域宽度进行设计考虑-ratio越大,Wdelta就会越小。

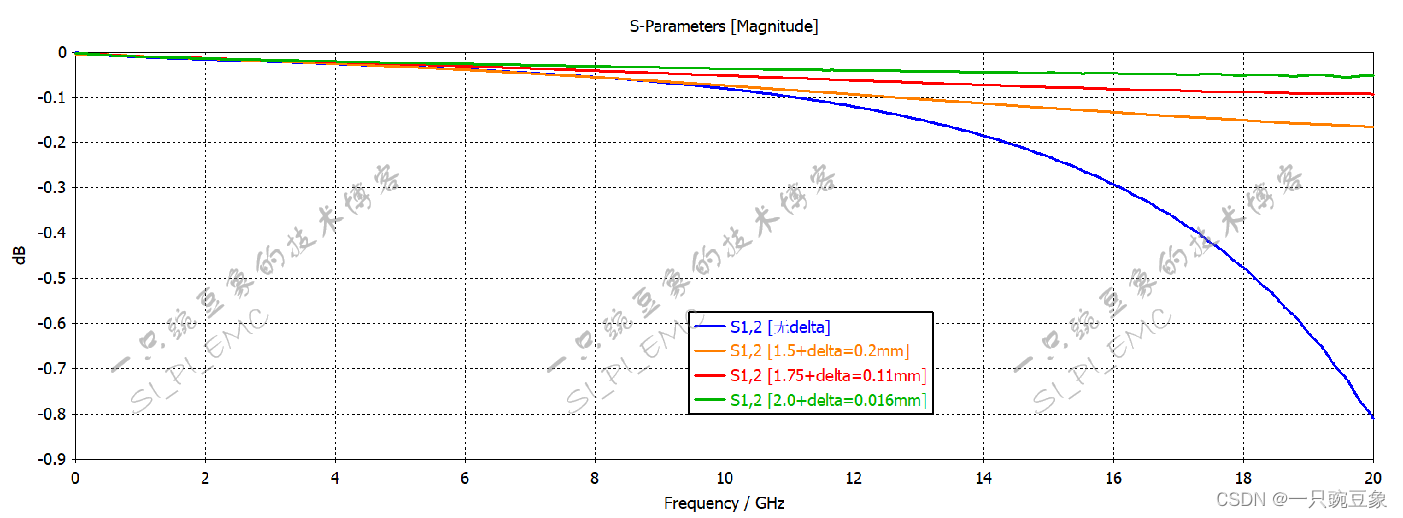

与ratio配合控制Wdelta的宽度,S12可以达到很好的效果:

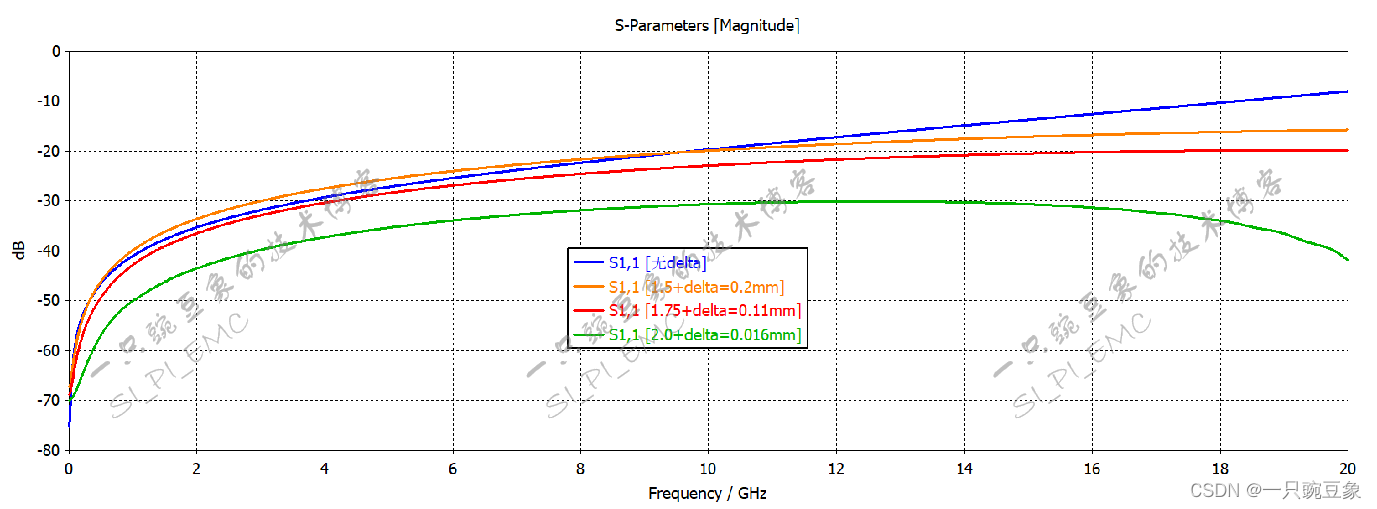

与ratio配合控制Wdelta的宽度,S11也可以达到很好的效果:

上述仿真结果,再结合加工工艺的能力,Wdelta=0.2mm是较为合适的选择。

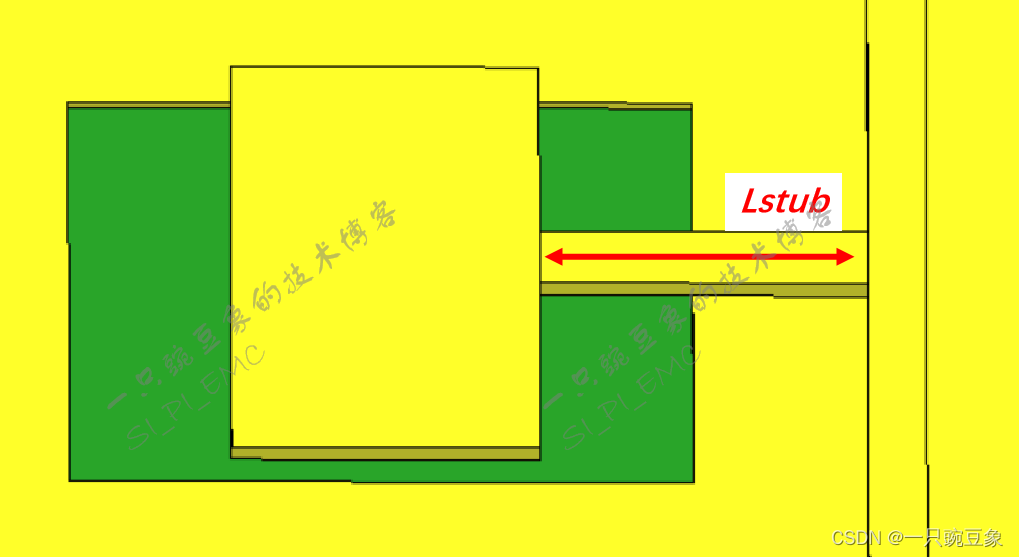

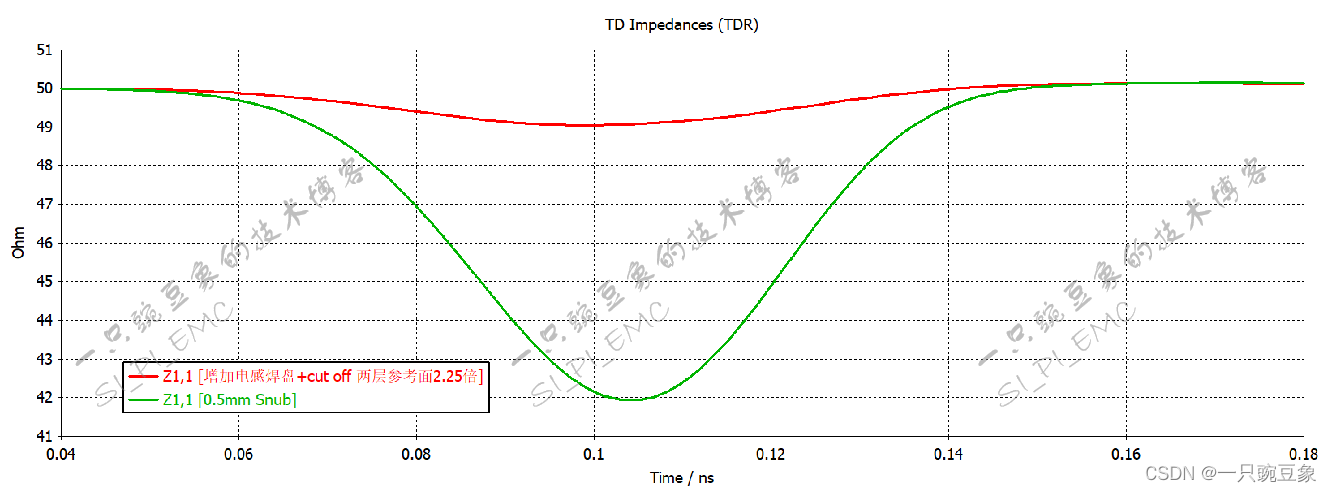

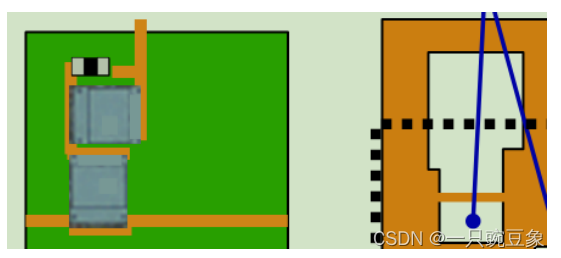

另一个在实际中经常出现的设计因素,就是如下图所示的stub:

如上图所示,假设Lstub=0.5mm,可以发现对阻抗的影响显著:

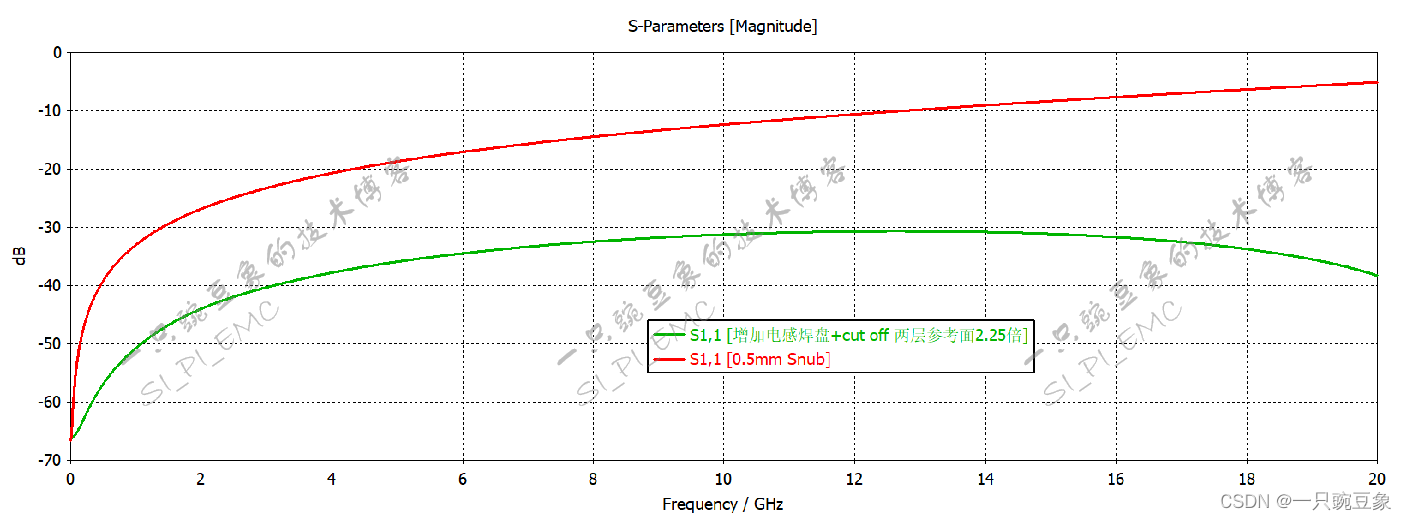

假设Lstub=0.5mm,可以发现对S11的影响显著:

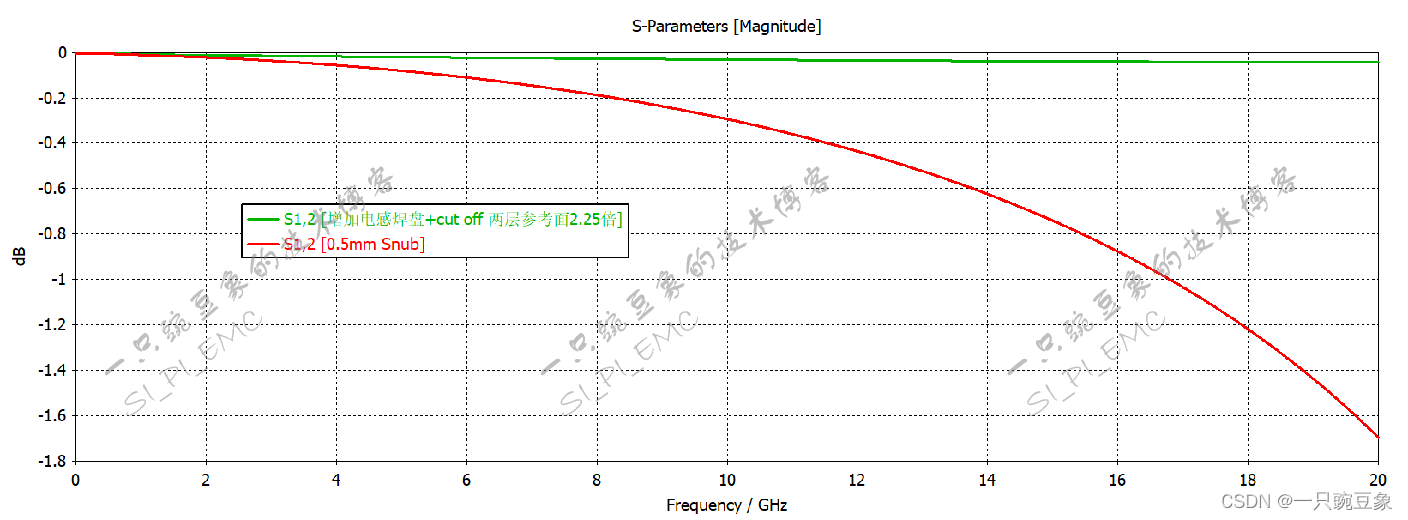

假设Lstub=0.5mm,可以发现对S12的影响显著:

通过上述的仿真分析,将控制焊盘阻抗的方法总结如下:

1. 避免在信号线上使用stub;

2. 控制大尺寸焊盘阻抗的有效方法是:挖空参考面,如果pad宽度大于走线宽度,从挖空相邻层参考面开始进行优化,但需要通过仿真确定ratio值,本例中可取值1.75;

3. 避免整体挖空封装的参考面,尤其是大尺寸的封装,对于Wdelta值的选取,需要按照实际设计情况单独仿真得到,本例中可取值0.2;

除此之外,还需要避免使用过孔。

以上都是基于一级器件(直接与信号线相连)的设计考虑,对于后级的器件,没有这些要求,但是,建议紧凑布局,整体挖空,如下图所示:

以上分析结果,在Murata的PoC电感网络的应用中均得到实践,并且,仿真及测试结果显示均较为一致。

参考文献:

[1] Proposal of a board design on PoC circuit;

[2] Board design and Inductor’s layout about Bias-T circuit for PoC。

本文讨论了高速信号PCB设计中如何通过精确控制焊盘阻抗和电感布局来满足50Ω特性阻抗需求,包括挖空参考面、避免stub和整体挖空参考面等策略。仿真结果和MurataPoC电路应用案例提供了实用设计指导。

本文讨论了高速信号PCB设计中如何通过精确控制焊盘阻抗和电感布局来满足50Ω特性阻抗需求,包括挖空参考面、避免stub和整体挖空参考面等策略。仿真结果和MurataPoC电路应用案例提供了实用设计指导。

3867

3867

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?