目录

0 引言

Intel Delta-L方法已被公认为一种常规方法,通过对测试线进行2端口测量来提取层压板材料的Dk和插入损耗。它需要具有不同长度的两对传输线,以及4端口或2端口VNA。本文对这种方法进行了简化,只需要对两条不同长度的测试线进行单端口的测量,这可以在VNA的单端口中实现,并且,这种简化的方法同样可以测量层压板层的Dk和总损耗,通过本文的描述,这种单端口Delta-L方法可以成为常规PCB层压板验证和表征的一种简单、低成本的方法,同时,文章也陈述了该方法的局限性。

1 单端口Delta-L技术

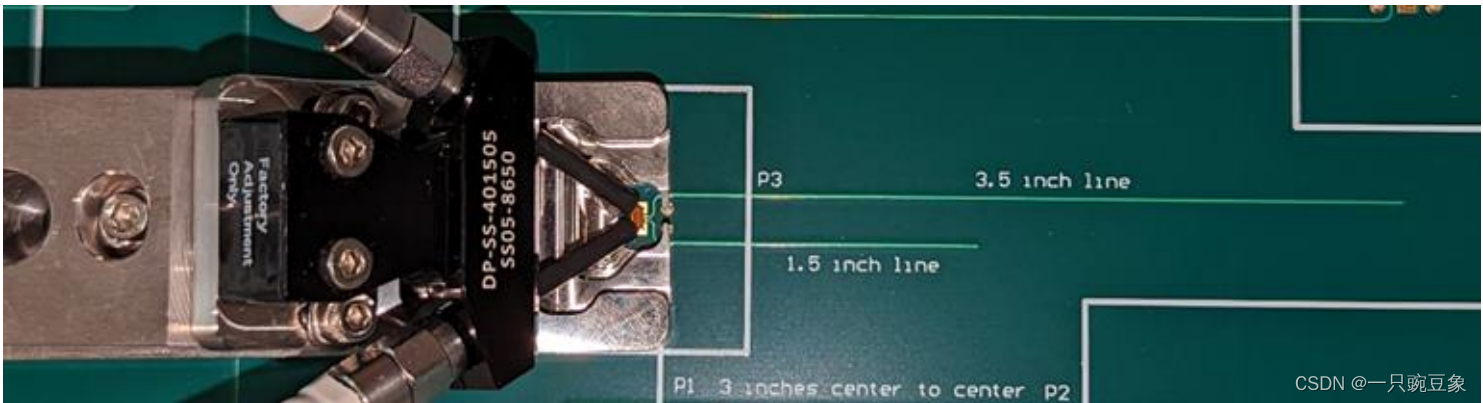

在单端口Delta-L方法中,仅从一端测量两条不同长度的单端走线,另一端保持开路,如图1所示,为这种测量方法的一个示例。

原则上,对于具有匹配端口阻抗的理想、均匀的传输线,回波损耗相当于通过线路的插入损耗的两倍,那么,使用单端口技术应该可以获得与使用2端口测量完全相同的有效插入损耗。

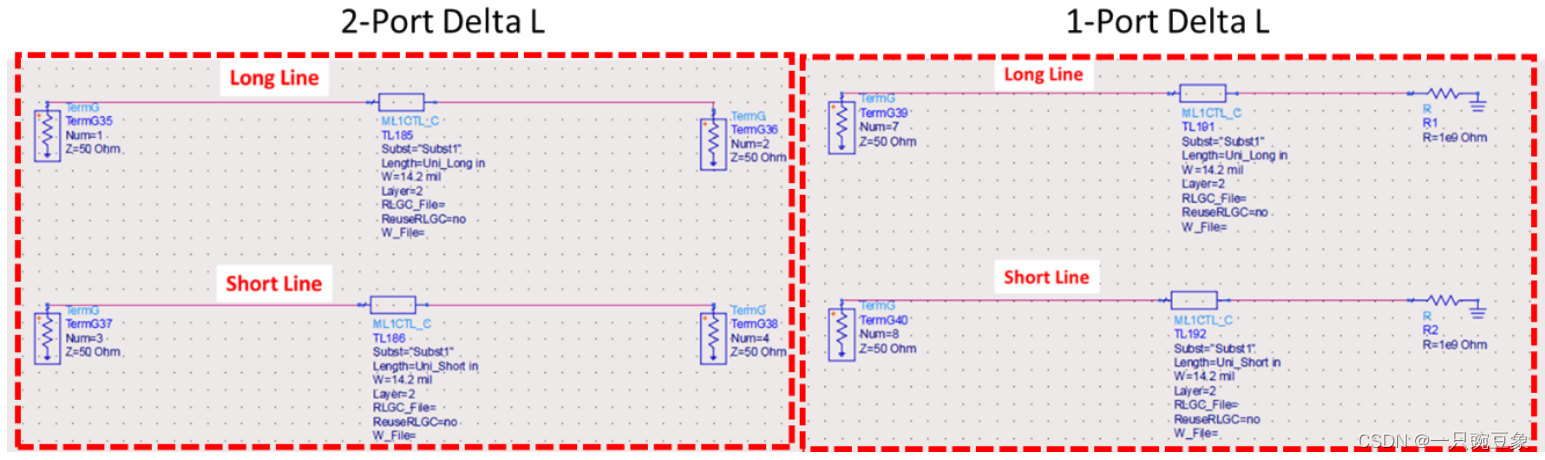

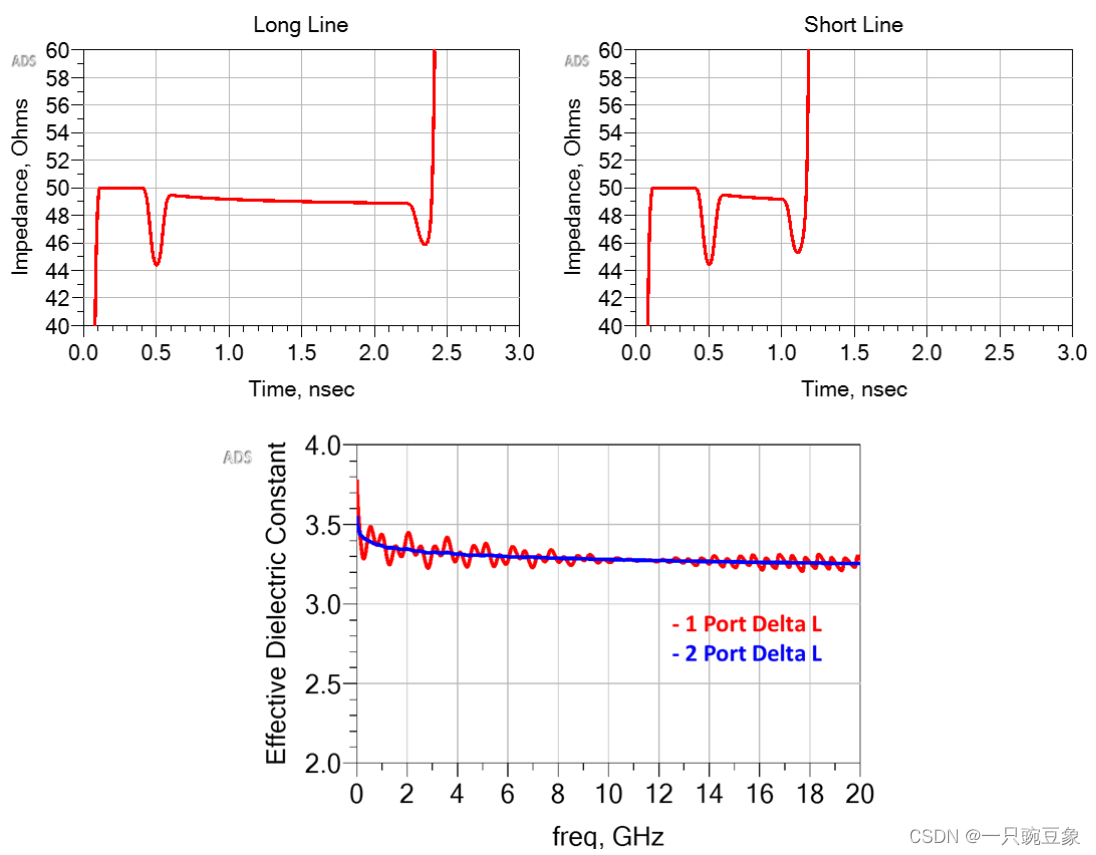

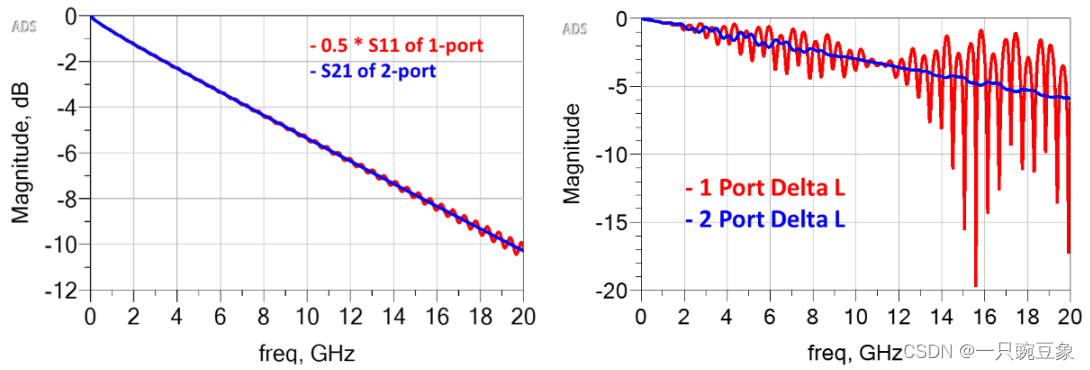

如图2所示,在Keysight的ADS中模拟了两条相同、不同长度的均匀无损传输线。在一种情况下使用2端口模拟,而在第二种情况下,仅使用单端口模拟。

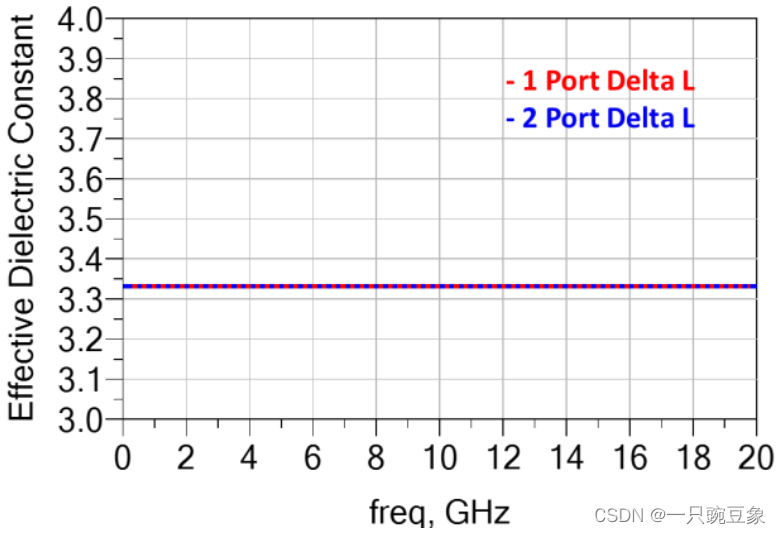

分别将2端口模拟的插入损耗的相位、单端口模拟的1/2返回损耗的相位展开,除以频率,并与线路长度的差值一起使用,以提取每个频率下的相位的时间延迟。根据时间延迟和长度计算每个频率下的相位速度,再被转换成基于光在空气中的速度的有效Dk,模拟对比结果如图3所示,可以发现,理想传输线状态下,单端口和2端口Delta-L方法所获取的Dk 参数完全一致。

如图4所示,进而在实测中,同样发现,使用相同的简易测试结构提取的2端口和单端口有效Dk也极为相似,从而验证了上述单端口Dclta-L方法的技术可行性。

2 基于单端口Delta-L方法的反射灵敏度分析

在2端口技术中,插入损耗的相位用于提取有效Dk。当来自VNA端口1的信号传播到端口2时,可能会出现阻抗不连续的反射。然而,这些返回端口1的反射只会进入端口2,如果再次反射,就会影响插入损耗的相位。这意味着2端口方法中阻抗不连续性反射的影响是二阶的,在实践中影响很小。

然而,在1端口方法中,阻抗不连续的每次反射都会反射回端口1,在端口1处,它会干扰线路末端的反射信号并使其相位发生偏移。这意味着1端口方法中的反射是一阶反射,会显著影响回波损耗的相位。在均匀线的情况下,用于提取有效Dk的相位是入射信号和开路远端反射之间的总相位变化。Dk中的任何频率相关性都将被提取并显示在结果种。这是对材料分散性的直接测量。

如果沿途存在来自阻抗不连续的多次反射,这些额外的反射波会在端口1与远端反射波结合,并根据反射波的具体位置略微改变总相位。这导致相移与传输线的长度无关,而是阻抗不连续的幅度和位置的结果。相移将随频率变化,导致提取的有效Dk具有与材料特性无关的特征。这种人为现象被称为异常色散。有三种常见的反射源导致异常色散:

1. 两端的发射;

2. 端口与线路阻抗的不匹配;

3. 轻微阻抗变化引起的线路长度的变化。

前两个来源的影响很容易被模拟。 端口阻抗失配对线路阻抗的影响导致的异常色散在低频时占主导地位。这是因为阻抗不匹配产生的相移具有恒定的相位幅度,但时间延迟为频率的倒数,随着频率的增加,相移的相对影响会减小。图5显示了端口阻抗和线路阻抗相差1欧姆时2端口和单端口测量的有效Dk值,注意,2端口Delta-L方法的提取结果表现出很好的鲁棒性,而单端口Delta-L方法的提取过程种产生的波动会随着频率的增加而减小。

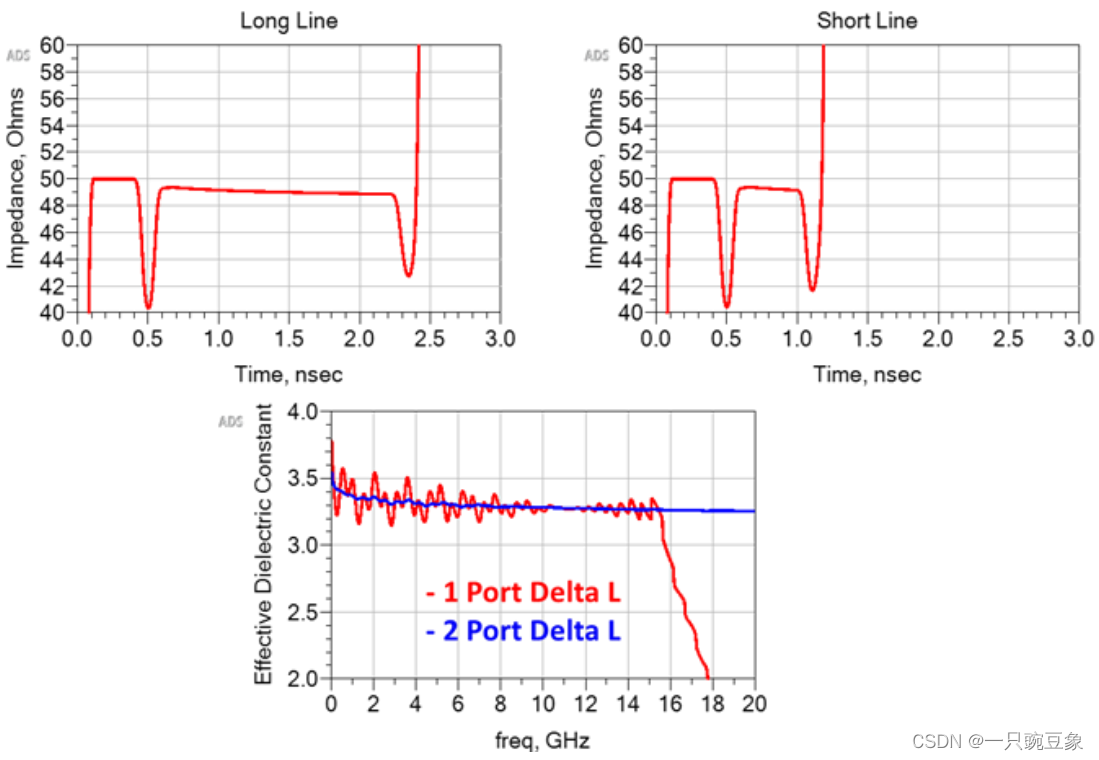

异常散射的第二个来源是发射时的不连续性。这会引起反射,反射通常随频率而变化。通过在发射端添加一条短的低阻抗传输线,可以很容易地模拟发射时不连续性的影响。图6显示了仿真模拟的TDR响应,这些仿真模型是均匀的,但在发射时不连续(如图中时间轴上的第一个阻抗跌落点所示)。

在此示例中,模拟了有损耗的材料,以将材料色散添加到模拟中。正如预期的那样,发射的影响遍及整个频率范围。在2端口测量中没有这些发射的影响,但是在单端口方法中有显著的异常色散影响。这清楚地显示了2端口方法对测试结构中的阻抗不连续性的鲁棒性有多强。

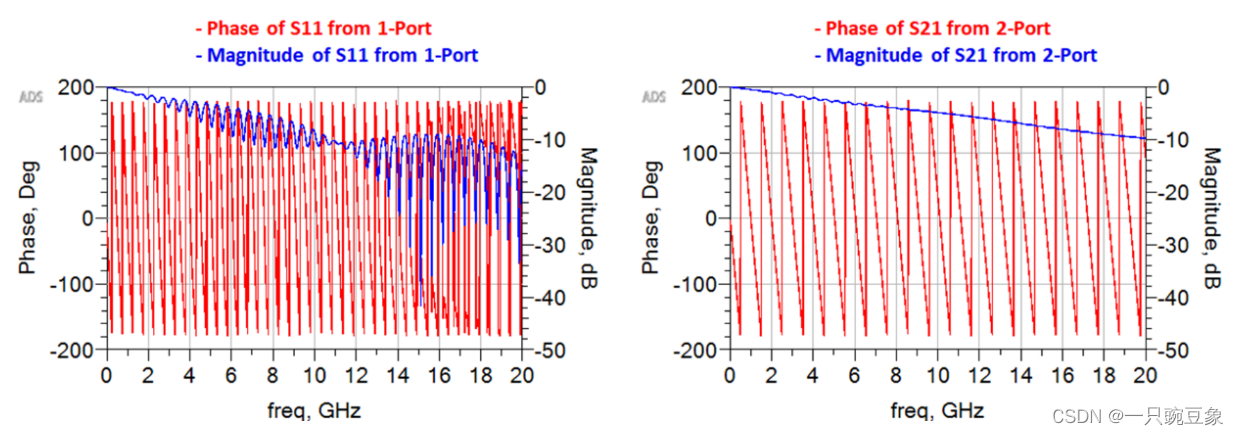

提取时间延迟的第一步是解开插入损耗或回波损耗的相位。这需要明确区分-180度和+180度之间的相位转换,以便计算周期。当因为反射引起的相位失真足够大时,会干扰相位的周期变化,表现为时间延迟和有效 Dk的阶跃变化。 通过加大发射不连续性来模拟这种效果。图7显示了这种具有较大发射不连续性的行为,并比较了对2端口方法和单端口方法的影响。

反射对单端口方法相位的影响比2端口方法大得多,因为它们在单端口方法中是一阶反射。这种对相位失真的影响如图8所示。

通过对发射端进行去嵌入,然后对端口阻抗进行归一化处理,可以显著减少这些异常色散的影响。图9显示了在启动去嵌入和端口归一化前后测得的有效Dk的示例。

经过上述校正之后,测得的有效Dk可以用作目标值来优化场求解器参数以提取体介电常数。图10显示了单端口测量值和仿真提取的有效Dk的比较,从测量的有效Dk和使用均匀传输线进行模拟得到的有效Dk之间的匹配结果中,发现两者已经非常接近,残余异常色散对模拟有效Dk的影响已经并不明显。

3 用充分表征的材料系统验证该方法

评估这种方法的最后一步是将仿真提取的Dk与已知具有一定准确度的材料进行比较。使用聚四氟乙烯基材料ZYSTZYF300CA-C制作了一个简单的双层电路板。报告的Dk为2.94±0.05。图11显示了电路板,其中一些线路配置用于2端口测量,一些线路配置用于单端口测量。

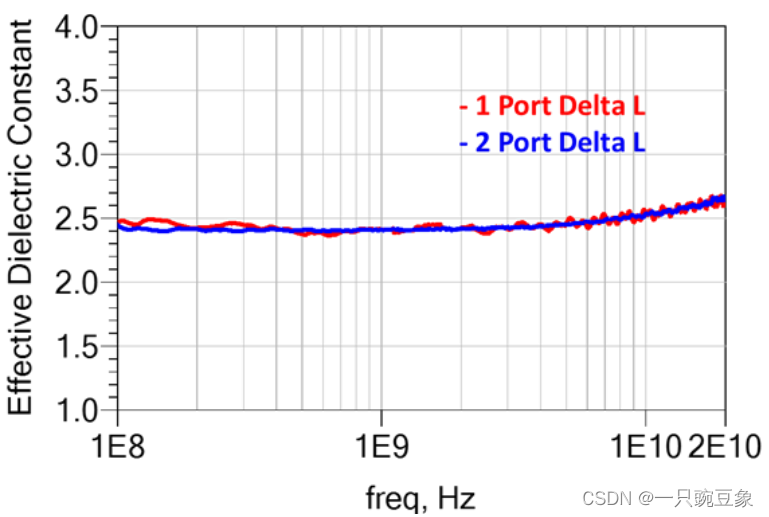

使用2端口和单端口测量方法提取的Dk如图12所示。

在该测量中,有效Dk随着频率升高而上升(约1GHz)。这不是测量的色散影响,而是由于微带的非 TEM行为造成的色散。

这种效应使用全波模拟器很容易模拟,然而,通常不能在2D场求解器中复现,图13显示了使用2D场解算器和全波场解算器时该结构的模拟有效Dk和测量有效Dk的数据对比。

根据该有效Dk的测量值并使用制造商的层压板厚度,调整场解算器中的体积Dk,以使模拟的有效Dk与测量的有效Dk相匹配。模拟中使用的体积值为Dk=2.94,这在该材料的公布范围(2.94±0.05)内,因此,这为该方法提供了一个重要的一致性测试。

4 在单端口法中提取总损耗

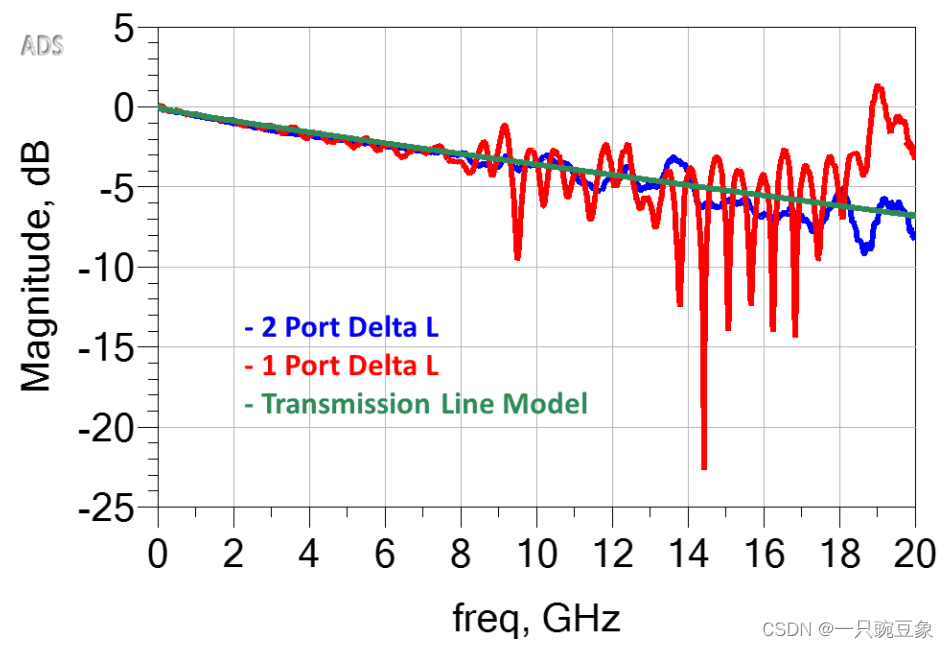

原则上,利用单端口和2端口delta-L方法,从两种不同线路长度的插入损耗差异中提取总损耗的结果应该是相同的。图14显示了在均匀传输线和发射不连续的情况下,两条线路的插入损耗或回波损耗的仿真模拟总损耗示例。

请注意,即使在没有阻抗不连续的均匀线路的情况下(图14左),单端口方法在较高频率下仍会受到反射的影响而产生轻微的振荡。这是由于有损线路的复阻抗和端口阻抗之间的阻抗失配仅为实数。有损线路的特征阻抗是复杂的,由下式给出:

在非常低的频率下,特性阻抗大多为实数,并且与端口阻抗实部匹配良好。随着频率增加,特性阻抗的虚部增加,并表现为前反射和开路远端反射的回波损耗中的干扰波纹。

发射不连续性的反射对单端口方法提取的回波损耗有巨大影响,但对2端口方法提取的插入损耗几乎没有任何影响。这凸显了使用单端口方法时减少反射的重要性。

单端口delta-L方法在提取总损耗时的有效频率范围受到发射端去嵌质量的限制。图15显示了采用2端口法和单端口法提取FR4测试结构的总体损耗测量结果。

在这个例子中,发射充分去嵌处理,最高可达约8GHz,以便与单端口方法一起使用。这突出了具有低反射发射的测试夹具以及使用精确的去嵌入技术的重要性。

5 总结

单端口Delta-L方法提取层压板的Dk和总损耗的目的是降低测量的复杂性,同时,也指出该方法的有效实施过程中存在的局限性,减少发射不连续性以及端口阻抗归一化来匹配线路阻抗是采用这一方法的重要前提条件,另外,通过使用场解算器提取的仿真数据也显示出单端口和双端口Delta-L方法的良好一致性。

本文翻译整理自DesignCon 2024中发表的“In-Situ Multilayer Printed Circuit Board Characterization Using One-Port Measurements”。

6547

6547

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?