芯片特点

-

准谐振操作:采用了准谐振(Quasi-Resonant, QR)技术,利用变压器磁芯的自然谐振来降低开关损耗,并提高效率。这种模式下,开关动作发生在电压过零点附近,从而减少了开关过程中的能量损失。

-

谷值锁定电路:拥有专有的谷值锁定(valley-lockout)机制,确保了稳定可靠的谷值切换。当系统检测到第6个谷值时,它会进入频率回折(frequency foldback)模式以进一步减少开关损耗。

-

轻载性能优化:为了在轻负载条件下保持高效率,引入了快速频率回折与最小峰值电流调制相结合的技术,迅速降低开关频率。此外,在非常低负载或空载状态下,控制器采用静音跳过(quiet-skip)模式,通过暂停开关操作来管理功率传输同时最小化声学噪声。

-

多种保护功能:

- 欠压检测:内置了欠压保护功能,能够监测交流输入电压,一旦发现电压低于设定阈值,则停止开关活动。

- 过功率保护(OPP):提供非耗散型过功率保护,保证输出功率恒定不受输入电压变化影响。

- 过温及过压保护:包括锁存式过压保护和NTC就绪的过温保护,后者可通过专用引脚实现温度监控。

- 异常过流故障保护:针对绕组短路或饱和情况下的额外保护措施。

- X2电容放电能力:集成了主动X2电容放电特性,确保在断开AC电源后X2电容可以安全地放电,满足IEC60950标准要求(EMC电磁兼容)

-

宽VCC范围:支持从9V至28V的工作电压范围,并具有28V VCC过压保护。

-

启动电路:内含高压启动电路,能够在启动阶段提供必需的电流,之后于正常运行期间关闭,有助于实现极低的待机功耗。

-

频率抖动:通过频率抖动技术减小电磁干扰(EMI)特征,改善整体系统兼容性。

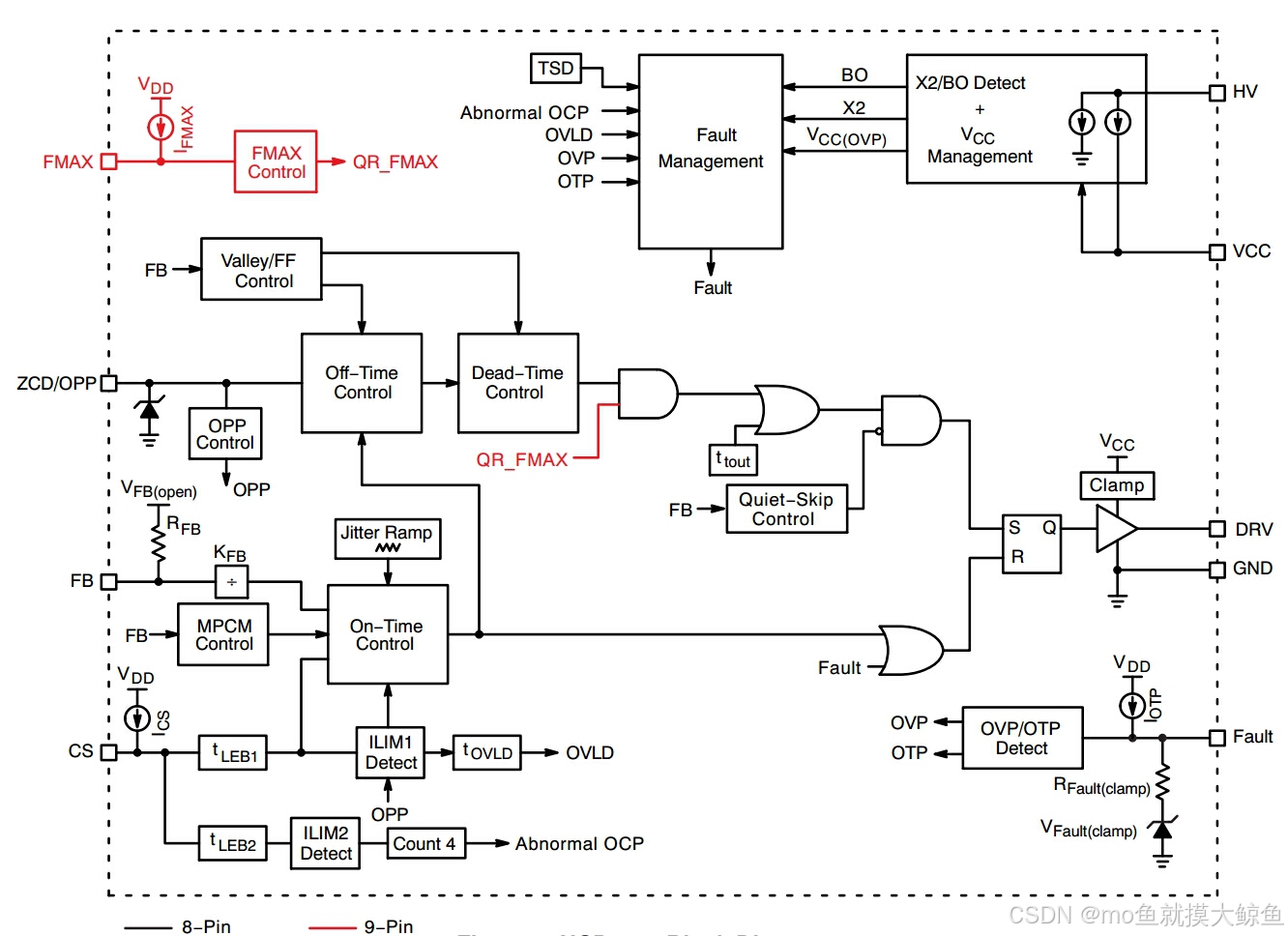

内部结构及引脚

| 引脚名 | 引脚作用 |

|---|---|

| Fault | 故障检测引脚,当该引脚上的电压超过或低于特定阈值时,控制器会进入故障模式。此引脚还具有精确的上拉电流源,可以直接与NTC热敏电阻接口,通常接一个热敏电阻和电容用作故障监测,如无需使用也可以直接接一个正常电阻并电容。 |

| FMAX | 设置芯片最大工作频率 |

| FB | QR反激控制器的反馈输入端口,可直接连接到光电耦合器以进行反馈控制 |

| ZCD/OPP | 用于零电流检测和功率补偿,通过辅助绕组与这个引脚之间的电阻分压网络提供输入信号给去磁检测比较器,并设置过功率保护(OPP)补偿 |

| CS | 电流检测,输入至逐周期电流限制比较器,用于监控电源转换过程中的电流情况 |

| GND | 接地 |

| DRV | 具有较高驱动能力的驱动输出引脚,适合于驱动高栅极电荷的功率MOSFET |

| VCC | 芯片供电引脚,正常供电范围为9V~28V,超出17V时芯片开始工作,低于9V时芯片停止工作 |

| HV | 用于高压启动和欠压锁定电路的输入。它还包含线路移除检测电路,以便在断开交流线时安全地释放X2电容中的电荷 |

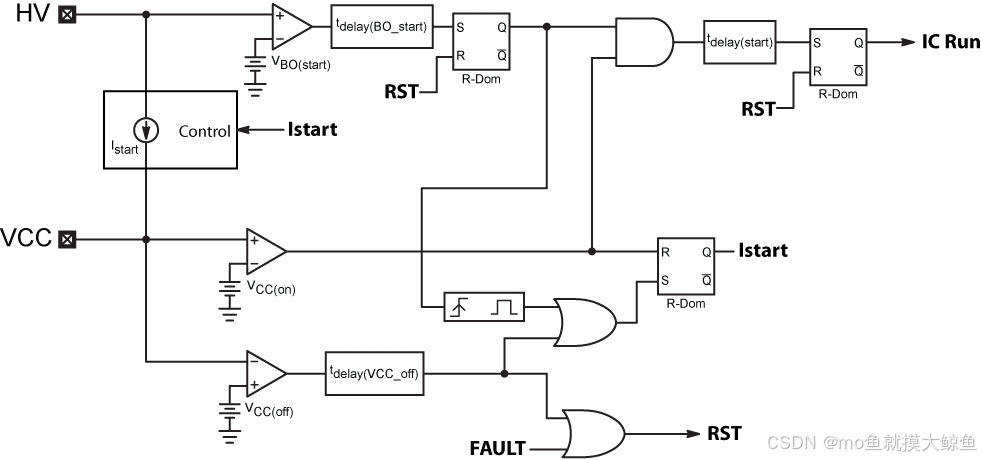

启动电路框图

工作流程:

VHV>VBO(start)时:

VCC引脚处需要接一个电容。起初Q输出为1,Istart(6mA)给电容充电,电容大小的选择影响开关速度,VCC>VCC(on)时,比较器输出高电平,Istart断开,经过tdelay(start)后IC启动;

VCC下降,当电压低于VCC(on),高于VCC(off)时,VCC(on)所接比较器输出低电平,VCC(off)所接比较器输出高电平,此时IC Run维持输出1不变,Istart再次开始充电;

当VCC低于VCC(off)时,Istart不输出,此时经tdelay(VCC_off)后RST输出高电平,所接SR锁存器R-Dom输出低电平。

VHV<VBO(start)时:

VCC>VCC(on)时Istart不输出,此时VCC通过偏置电流放电降压;当VCC低于VCC(off)时,Istart开启,给VCC充电,如此往复。

注:IC Run驱动的应该是DRV引脚前接的放大器,总框图中,Clamp钳位表示了上述的这一整个过程。成功驱动时,DRV为高电平。

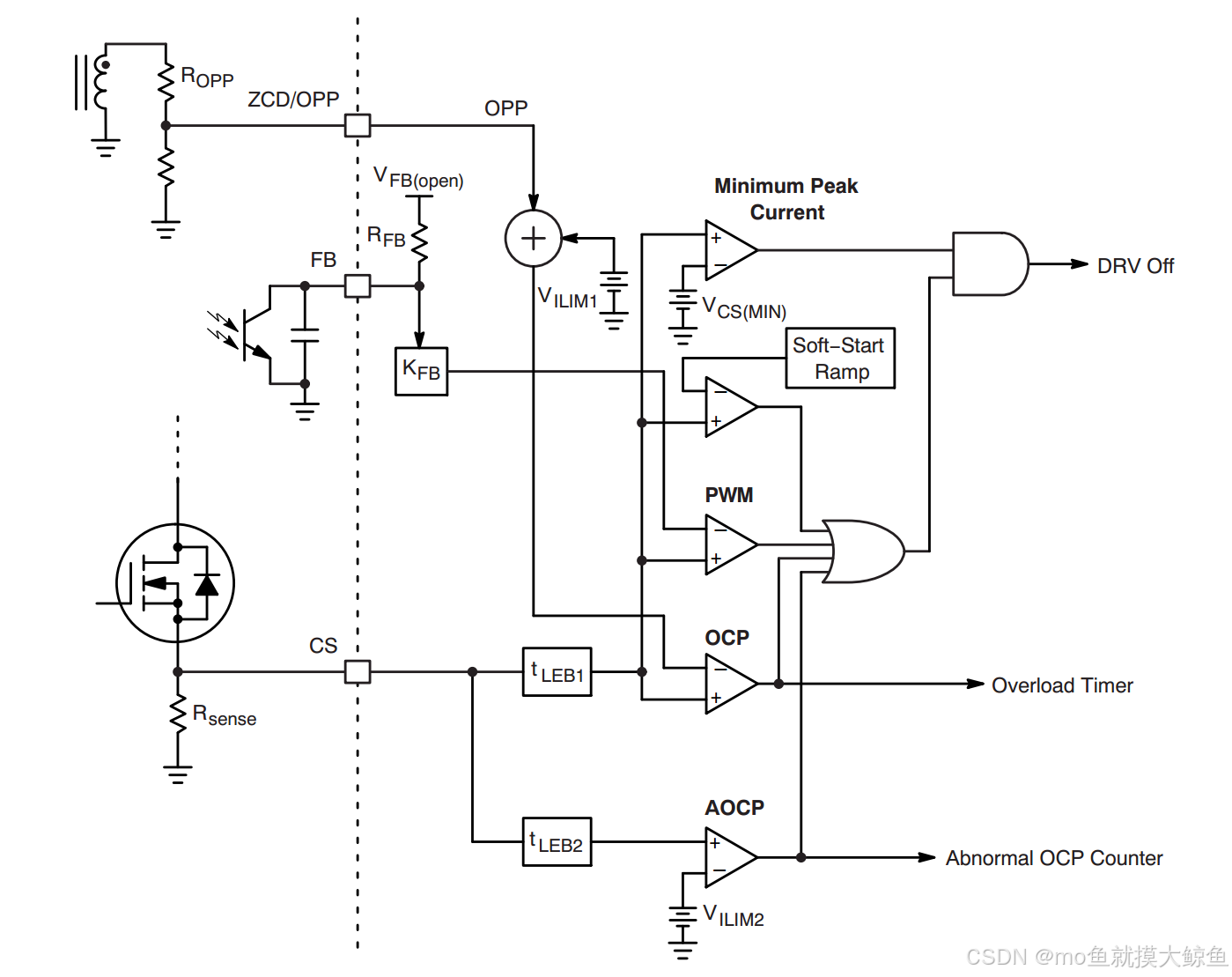

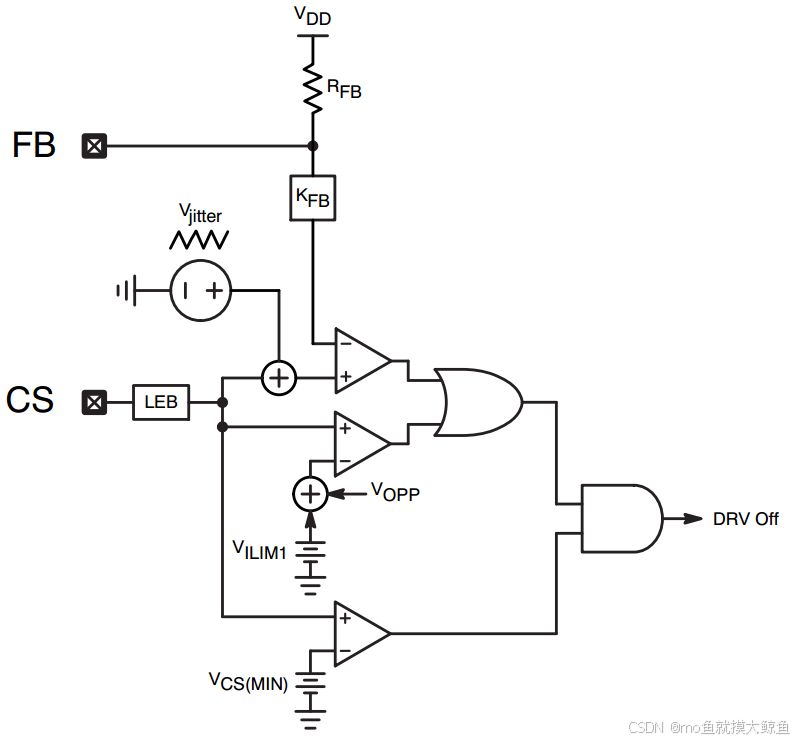

电流感应逻辑(包含最小电流峰值调制)

该部分原理图包含了零电流检测和功率补偿引脚ZCD/OPP,QR反激控制器输入端口FB和电流检测端口CS

工作原理:

CS所连MOS管由DRV引脚控制开断,DRV off为总结构图中通过一个或门连接至SR锁存器中的R引脚,输出为1时DRV置0,VCS(min)表示CS管关断时的最小电压,只有VCS>VCS(min)时DRV off才有可能置1。Rsense设置回路中流过的峰值电流,FB通过光耦实现输出电压反馈。当输出电压过小时,流过光耦晶体管的电流较小,VFB在RFB上的压降小,给到PWM运放负极的电压大,使DRV off置1所需的电流更大,MOS管的开通时间增加,此时根据Flyback电路输出电压的公式可知,此时D增大,VO增大,起到负反馈作用。

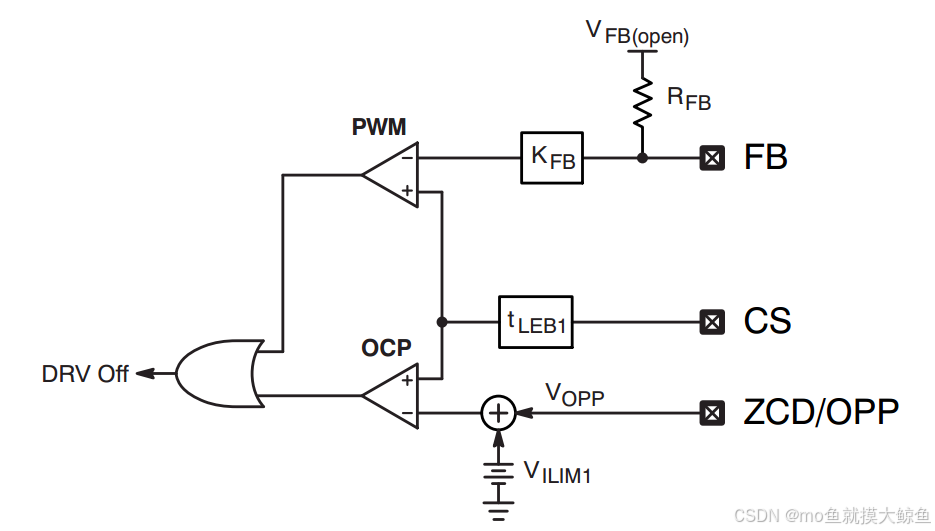

过功率保护补偿电路原理

工作原理:

该部分主要用于监视变压器的退磁。变压器退磁时,辅助绕组产生逐渐降低的反向电流,通过电阻在ZCD上产生反向压降,与VILIM1叠加。当退磁完成,电流到波谷时,VILIM1+VOPP>0,OCP输出低电平,若此时PWM输出低电平,则DRV off输出低电平,DRV导通,用于减少开关损耗和电磁干扰。

软开关实现

软开关定义建议参考这篇什么是硬开关和软开关?_软开关和硬开关的区别-CSDN博客

jitter ramp,频率抖动谐波,向内部时钟增加一个远小于开关频率的抖动波,可以用来减少电磁干扰EMI,参数包括抖动幅度、抖动频率和抖动频率的变化范围。

工作原理:

软启动是通过提高内部参考VSSTART,也就是VCS+Vjitter,并将其与当前感知信号FB进行比较来实现的。控制器初始上电,VSSTART从0V开始上升。峰值电流设定值随后受到VSSTART斜坡的限制,在VCS>VCS(min)的情况下,VCS+Vjitter不能超出VFB,若超出这个值,DRV off则置1关断开关管,使电流降低。Vjitter为周期性变换谐波,导致在启动期间开关电流逐渐增加。软启动时间tSSTART一般为4ms。

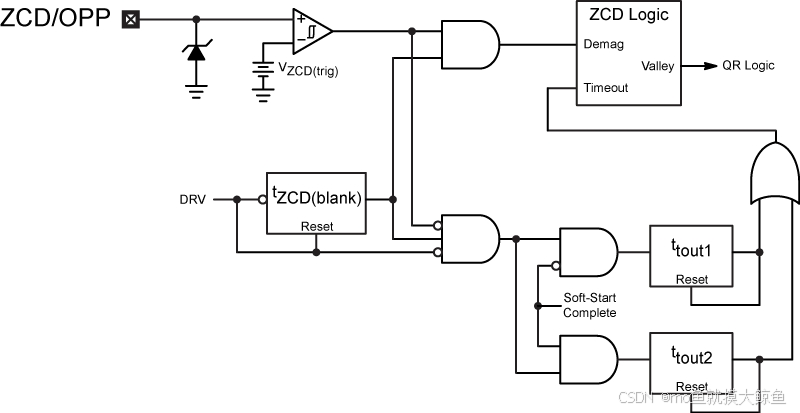

谷值超时电路

谷值检测控制:在准谐振反激式转换器中,变压器初级绕组的电压会在每个开关周期内经历一个振荡过程。谷锁电路通过检测这些振荡波形的谷值(即电压最低点,此时MOS管电压趋近于0),选择最佳的开关时机,最大限度地减少开关损耗

tZCD(blank):去磁化检测的前缘消隐时间,用来防止在开关瞬间由于寄生振荡或噪声引起的误触发;tout1和tout2:软起动超时时间和稳态超时时间,前者100us,后者6us,用来在未能检测到谷值电压(即VZCD(trig)表示的去磁阈值电压)时延时后启动,前者用来限制重载下CCM操作(即连续导通模式)后者用来限制频率步进(即轻载或无负载情况下降低开关频率)

工作原理:

去磁检测信号正确触发:VZCD(trig)表示去磁阈值电压,退磁时绕组两端通常有一个负向脉冲。当ZCD/OPP上的电压高于VZCD(trig)+VZCD(HYS)(滞后电压,防止误导通)时,VZCD所连接的运放输出端置1;当DRV置0(开关管关断)时,经过tZCD(blank)后置1,此时Demag置1,QR logic允许开关管导通;

去磁检测信号未正确触发:当软开关过程未完成时,经后Timeout置1,QR logic置1,强制开关导通,通常用于重载;当软开关过程完成时,经

后Timeout置1,QR logic置1,强制开关导通,通常用于轻载。

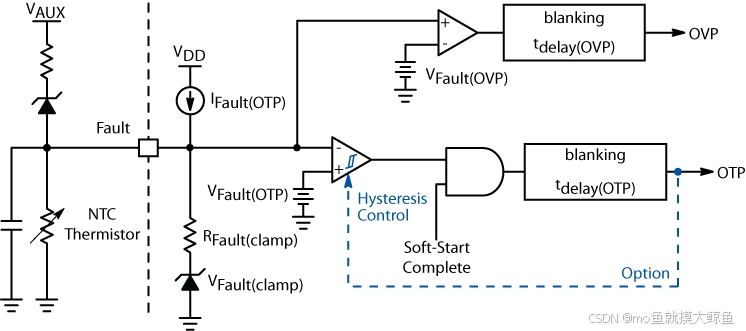

故障引脚工作原理图

工作原理:

Fault引脚上通常接一个负温度系数热敏电阻,用来防止实际运行中出现的散热问题,实现过温保护。VAUX为电路中实际电压,Fault引脚上同样可以实现过压保护。

当Fault引脚上电压过高,超出时,经过一段时间的延时后过压保护启动,控制器锁存,直到电压降至复位电压;当处于过热状态下,引脚上电压低于

,控制器检测到故障,若此时软开关过程已完成,则进入过温保护中,控制器锁存,直到电压超过

+

(存在滞后控制以确保稳定性时)复位。

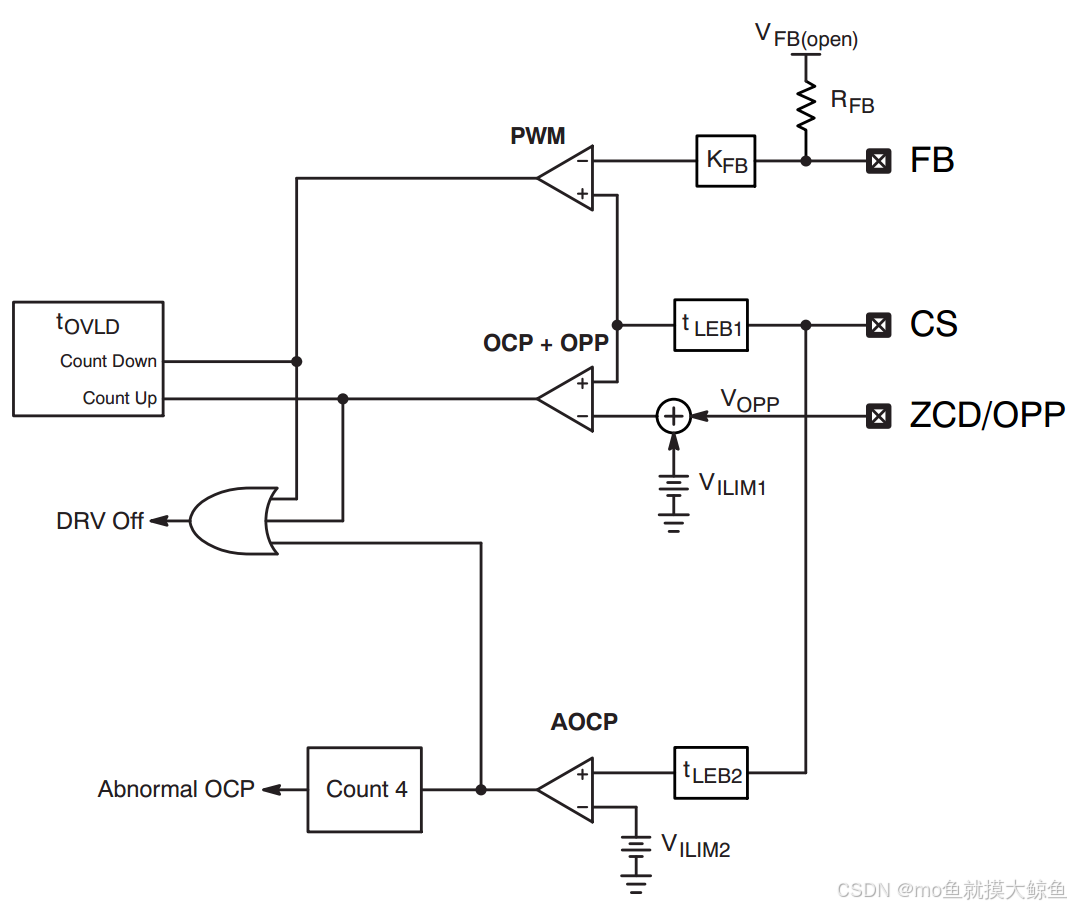

过载电路

工作原理:

过载保护过载定时器集成了过载故障的持续时间,定时器计数在故障出现时增加,在故障消除后减少,超时后控制器检测到过载情况,根据版本的不同采取锁存断开或进入安全、低占空比的自恢复模式等措施。

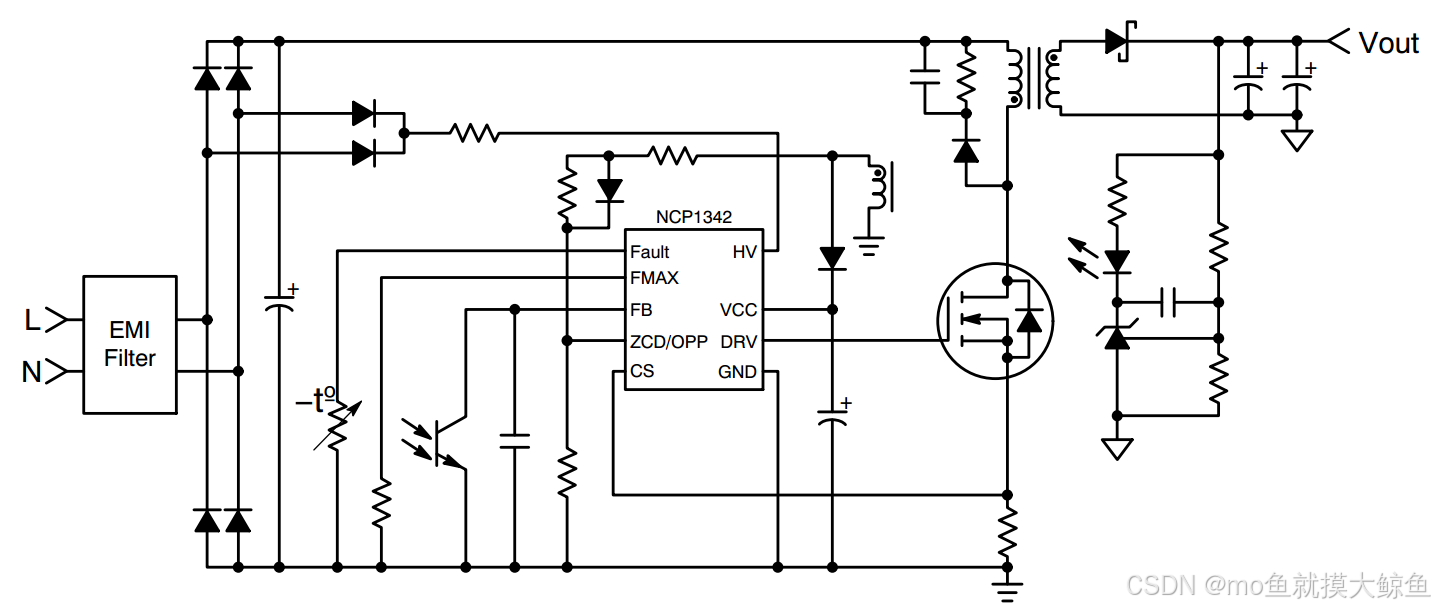

典型应用—Flyback反激变换器分析

工作原理:

当HV上电压达到启动值时,芯片经一系列过程启动,MOS管开通,变压器绕组上电流增加,此时副边绕组上感应电压为负,由于二极管的存在,回路无法导通,不传递给Vout,此时Vout因为接负载而存在少量的下降;

输出端所接发光二极管通过FB上所接光耦隔离,向芯片传递输出电压信号,用来调控Vout。当CS上由所接电阻而产生的电压达到一定值时,DRV置0,MOS管关断,经原边绕组所接二极管续流,此时电流下降,副边绕组感应电压为正,导通,将电压传递给Vout,辅助绕组上两端电压大于0,电流流入同名端加速退磁,流经电阻,给ZCD引脚一个负电压;

当退磁完成后,ZCD通过与去磁阈值电压的对比感应到退磁完成,经过一段时间后再次导通二极管,实现谷值检测控制(具体参考谷值超时电路部分)如此循环往复。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?