最近看了不少SiC MOSFET封装的文章,但总感觉只是基于现有工艺的总结,没有明确的优化路线,所以写了这篇。如果大家是完全的新手小白,可以看看这个回答碳化硅(Silicon Carbide,SiC)功率器件封装关键技术 - 知乎

有一定条件的可以去知网搜这篇《碳化硅功率模块封装及热管理关键技术》里面讲的挺全的

最后,本人所有文章都是完全公开免费的,如果有朋友发现哪篇被转成了付费的,请随时私信我,我来修改权限。

目录

SiC MOSFET模块封装概述—是什么

SiC MOSFET模块封装是将碳化硅MOSFET芯片封装在特定的结构中,以保护芯片、提供电气连接、实现散热和机械支撑等功能,实现其在高功率、高频率、高温等复杂环境下的稳定运行。封装技术需要考虑电气连接、散热管理、机械支撑和环境防护等多个方面。

封装过程

-

芯片准备:将SiC MOSFET芯片准备好,确保芯片的质量和性能符合要求,一般芯片大小都是5mm×5mm。

-

芯片贴装:将芯片安装在DBC基板或其他合适的基板上,通常采用银烧结等先进工艺,以提高热导率和机械强度。

-

电气连接:通过引线键合或无引线结构(比如铜带连接)实现芯片与外部电路的电气连接。无引线结构可以显著降低寄生电感,提高高频性能,但对工艺有一定要求。

-

封装:使用环氧树脂或其他封装材料对模块进行封装,以保护芯片免受外界环境的影响。

-

测试:对封装后的模块进行电气性能、热性能和机械性能的测试,确保其满足应用要求

SiC MOSFET模块封装价值—为什么

关于MOSFET的分析部分可参考我的这一篇文章器件(二):一文读懂SiC MOSFET-CSDN博客

碳化硅材料特性

-

高击穿电场:碳化硅的禁带宽度约为硅基材料的3倍,临界击穿场强约为硅基材料的10倍,这意味着碳化硅器件能够在更高电压下稳定工作,可承受更高电压。这使得碳化硅MOSFET模块在高压应用中具有更好的耐压性能和可靠性,如在智能电网、电动汽车等领域。

-

高热导率:碳化硅的热导率约是硅基材料的3倍,能快速散热,确保器件工作时不会因过热而性能下降。这一特性对于高功率密度的碳化硅MOSFET模块尤为重要,能够有效提高其在高功率工作状态下的稳定性和寿命。

-

高频特性:碳化硅的电子饱和漂移速率约是硅基材料的2倍,大幅提升了器件的开关速度,显著提高电力转换系统的效率和功率密度。这使得碳化硅MOSFET模块在高频应用中表现出色,如在通信电源、数据中心等领域。

为何需要专用封装技术

-

材料特性需求:碳化硅材料具有高击穿电场、高热导率、高频特性等优势,但芯片面积更小、发热密度更高,这使得传统的硅基封装技术难以满足其需求。例如,传统的硅基封装可能无法有效散发碳化硅芯片在高功率密度下产生的热量,导致芯片过热,影响性能和寿命。

-

性能优化:专用封装技术能够针对碳化硅MOSFET的特性进行优化,如降低寄生参数、提高散热效率、增强高温可靠性等,从而充分发挥其在高频、高压等应用中的优势。比如,通过采用特殊的封装结构和材料,可以减少封装内的寄生电感和电容,提高模块的开关速度和效率。

封装技术的四大功能

-

电气连接:封装技术需要确保芯片与外部电路之间的可靠电气连接,以实现信号和功率的传输。对于碳化硅MOSFET模块,电气连接的质量直接影响其开关性能和效率。

-

机械支撑:封装为芯片提供机械支撑和保护,防止芯片在使用过程中受到外界机械应力的损坏。这对于高功率密度的碳化硅芯片尤为重要,能够提高其可靠性和寿命。

-

散热管理:有效的散热管理是碳化硅MOSFET模块封装的关键。封装需要能够快速散发芯片产生的热量,保持芯片在合适的工作温度范围内。

-

环境防护:封装能够保护芯片免受外界环境因素的影响,如潮湿、灰尘、腐蚀等,提高模块的稳定性和可靠性。

封装技术优化方向—怎么做

封装技术的优化大部分都是从实际的研究方向入手,比如材料、结构等。但对于新手来说,想快速确定自己到底要从哪个方向入手非常难,因此我对几大优化参数进行了总结。在实际的模块优化中,除了工艺创新是间接性提升这些性能,其它的所有优化方式都是在针对这几个参数进行优化,万变不离其宗。

电性能优化

电性能优化无外乎寄生参数的提升和绝缘特性的优化,绝缘特性通常由绝缘结构的材料所决定,如常用DBC封装中的氮化铝陶瓷,就是非常典型的绝缘材料。因此针对模块封装本身的优化一般集中在寄生参数的优化上,而由于模块的电容特性主要由MOSFET本身决定,电性能的提升集中在了优化电流回路,主要关注寄生电感。

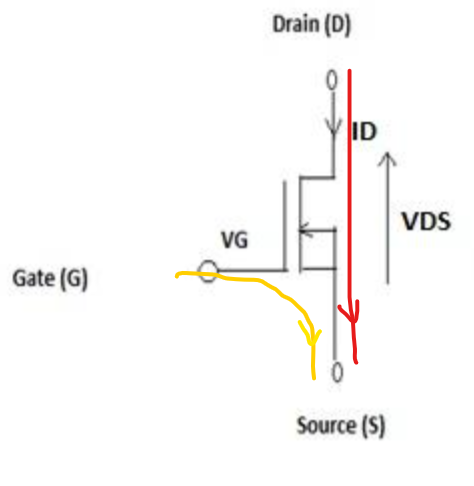

电流回路优化的主要目的在于防止瞬时变化的电流经寄生电感引起巨大的过冲电压,MOSFET的电流路径如下图所示,因此,对电流回路的优化多在优化栅源回路和漏源回路中。

而在多芯片并联的情况下,除了需要考虑单芯片电流回路本身,还需要考虑多芯片电流回路间的均流特性,减少芯片并联时的电流不均衡度,平衡芯片动态电流。

栅源回路优化

MOSFET导通时,通常给栅极加15V~20V的电压,因此在漏源间无电流时,栅源回路流过的电流较小,对寄生电感的要求较为宽裕。然而,当栅源和漏源的两个源极集成在一起时,漏源间流过的大电流会同样作用在栅源的电流回路中,通过栅源间的寄生电感,在栅极引发过冲电压。

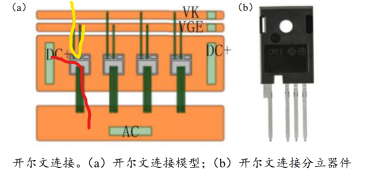

为此,目前栅源回路的设计大部分采用开尔文源极,也就是将栅源的源极和漏源的源极分开,以此避免栅源间的电压过冲

当然,开尔文连接的实际连接方式有很多种,但核心部分都在于“隔离栅源回路和漏源回路”。而在实际应用过程中,如果能降低栅源间的寄生电感,那也许可以在MOSFET的Qg允许的范围内提高栅源电流,增加开关速度。

漏源回路优化

目前现有电流回路的优化方向主要集中在漏源回路优化,降低漏源间的寄生电感,减少开通时芯片两端电压过冲,提高整体电路的EMI性能。漏源回路寄生电感的优化方向又分两种,一种是降低自感,一种是利用互感相消。

降低自感

降低自感的方式主要在于缩短电流回路,例如半桥模块的双面散热封装,3D封装,还有PCB+DBC混合封装、埋入式PCB封装等,就是通过缩短电流回路来降低自感,而材料和封装器件大小的调整同样可以做到这一点。

然而,这种优化方式虽然效果非常不错,但存在工艺上的问题。譬如目前很多3D封装结构都是一层叠一层,叠的层过多时,对工艺就会有挑战,工艺要求高,良品率低,出现高成本低经济效益的情况,这也是为什么很多看起来效果很好的封装结构尚未批量投产。

互感相消

目前很多封装结构都围绕着互感相消进行。互感相消原理看这篇第 6 章 互感耦合电路,我就不在此赘述。简而言之就是,两条电流路径平行且电流方向相反时,产生的互感能降低整体电感。而这两条电流路径靠的越近,互感越大,对整体寄生电感的降低效果越好。

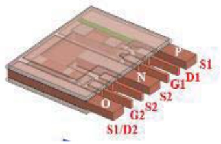

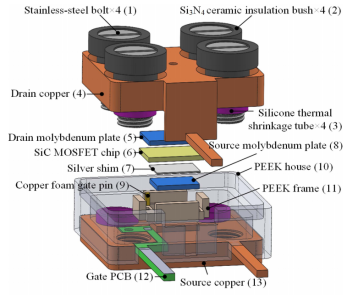

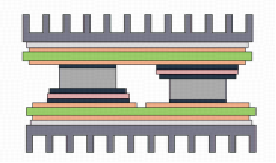

互感相消的方法有很多,包括叠层DBC封装、双面散热封装、2.5D封装等等,大部分都围绕着半桥模块或三相全桥模块进行。DC+流入,DC-流出,AC端子引出交流电,上半桥电流路径与下半桥电流路径平行且电流方向相反,能实现很好的互感相消。也有针对单个MOSFET的压接封装模块,比如下图,这种对实验室的工艺有一定要求。

热性能优化

模块散热性能的参考依据通常是热阻,碳化硅功率模块的热阻主要来源于芯片焊料层、覆铜陶瓷基板(DBC)、金属基板、热界面材料(TIM)和散热器。为了降低热阻,研究者们提出了双面冷却封装、压装封装和冷却集成封装等先进封装技术。这些技术通过充分利用碳化硅芯片底面及顶面的散热面积、缩短热流传递路径来降低模块封装热阻。

而在实际设计中,热性能优化主要集中在模块结构和散热方式上。

从热应力方面来说,模块的封装布局结构一般需要尽可能的对称,这样能极大程度上避免温度分布不均的情况,进而降低功率模块单点脱落的可能性,提高模块的可靠性。

从散热性能方面来说,提升散热性能的方式包括优化封装结构、材料和散热方式,前两者包括选用散热性能更好的材料,将模块制作成双面封装形式、采用银烧结、使用均温板等方式,散热方式的优化包括直接在模块外侧DBC背面蚀刻散热微通道,提高散热器散热性能等。

力性能优化

力学性能的优化主要集中在降低模块中某个部分的应力上。常用方式包括增加缓冲垫块,优化垫块结构,优化焊片结构等。

在设计时,力学性能通常需要考虑以下几点:

-

机械强度:封装结构需要能够承受机械应力,确保在振动、冲击等环境下的可靠性。

-

热膨胀匹配:碳化硅的热膨胀系数较低(约3ppm/K),与封装材料(如铜、陶瓷)的热膨胀系数差异可能导致热应力,影响模块的可靠性。

-

高温稳定性:碳化硅MOSFET模块需要在高温环境下仍能保持较高的力学性能,例如在1200°C到1400°C的温度范围内,其抗弯强度可达500-600MPa。

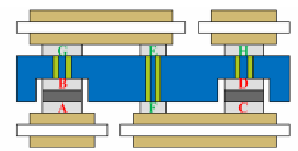

例如下图这种结构,就能极大的降低模块的剪切应力

人工智能优化方式

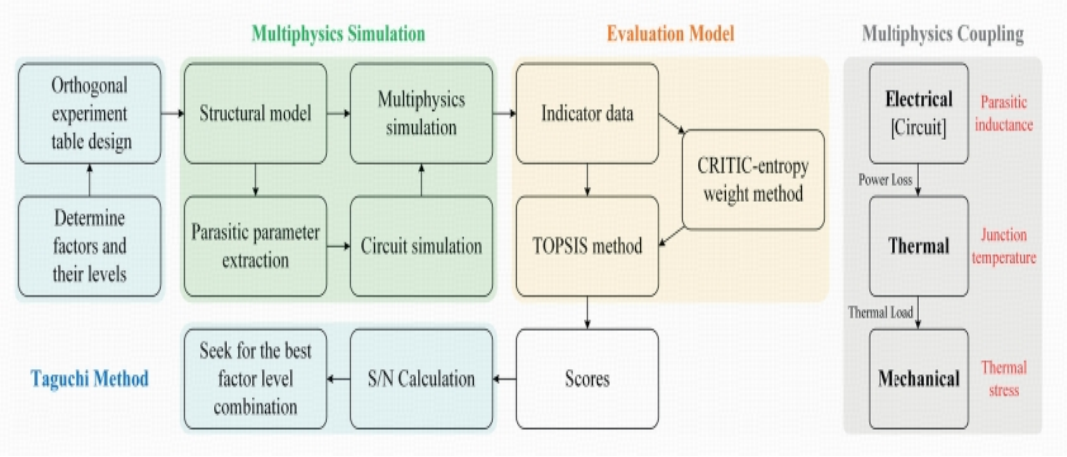

除了上述传统优化方式以外,随着人工智能的发展,功率模块的封装技术同样引入了许多新的优化方式,尤其是在模块的多性能综合提升上,比如下图这种:

人工智能在SiC MOSFET模块封装中的应用主要有以下几点:

优化封装设计

-

降低寄生参数:利用人工智能算法,如遗传算法、粒子群优化等,对封装结构进行优化设计,以降低寄生电感和电容。这些算法可以通过模拟不同的封装布局和材料组合,找到使寄生参数最小化的最优方案,从而提高模块的高频性能。

-

热管理优化:借助机器学习算法,对封装的热管理进行优化。通过对不同封装材料、结构和散热方案的模拟和分析,预测其热性能,并找到最佳的热管理策略,以确保模块在高温环境下稳定运行。

提高封装可靠性

-

剩余使用寿命预测(RUL):利用人工智能技术,如深度学习中的长短期记忆网络(LSTM)等,对SiC MOSFET模块的剩余使用寿命进行预测。通过对模块在不同工作条件下的性能数据进行监测和分析,建立预测模型,及时发现潜在的故障风险,提前进行维护和更换,提高系统的可靠性和可用性。

-

故障诊断与分类:采用支持向量机(SVM)、卷积神经网络(CNN)等机器学习算法,对SiC MOSFET模块的故障进行诊断和分类。通过对模块的电气特性、温度变化等多维数据进行分析,快速准确地识别出故障类型和位置,为故障修复提供指导。

智能封装与集成

-

集成智能传感器:在SiC MOSFET模块封装中集成智能传感器,如温度传感器、电流传感器等,并利用人工智能算法对传感器数据进行实时处理和分析。这可以实现对模块工作状态的实时监测和智能控制,提高模块的性能和可靠性。

-

自适应封装结构:基于人工智能的自适应控制技术,开发自适应封装结构。这种结构可以根据模块的工作状态和环境条件自动调整封装参数,如散热性能、电气连接等,以实现最佳的性能和可靠性。

333

333

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?