Design Compiler(以下简称DC)是Synopsys公司用于做电路综合的核心工具,可以将HDL描述的电路转换为基于工艺库的门级网表。本系列主要介绍综合相关的知识以及DC工具的使用。

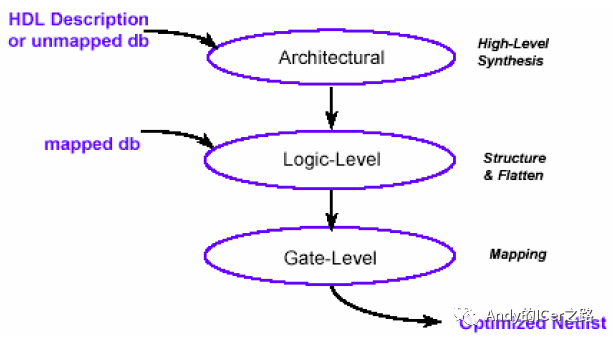

DC进行优化的三个阶段:结构级、逻辑级以及门级。在不同的阶段,DC运用的方法和优化余地是不一样的,下面会对这三个阶段的优化进行介绍。

上图是这三个阶段的关系图,可以看到,结构级属于最高的抽象层次,当读入Verilog代码或者没有经过映射的db文件后,DC的优化从这个阶段层次开始,可以说,结构级是优化的最高层次,所以对DC来说,这个层次的综合可以称为高层次综合(High-Level Synthesis)。结构层的下一个优化阶段是逻辑级阶段,也是读入映射过的db文件的DC的初始优化阶段。再往下一个阶段是门级阶段,也是优化的最后阶段,这里所要作的工作主要就是GTECH到工艺库的映射。

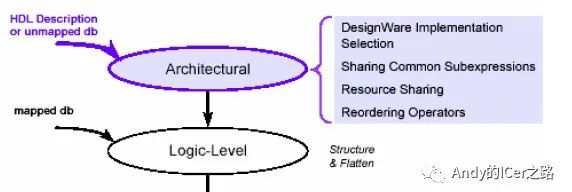

一、结构级优化

因为结构级是优化过程中层次最高的一级,因此它也是DC可以采用的优化方法最多的一级,它的主要优化方法如下图所示。

1. DesignWare选择

DW选择是结构级优化的一个很主要的

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

9182

9182

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?