云计算和大数据等领先趋势推动了指数级的流量增长和400G+以太网的兴起。数据中心网络面临着更大的带宽需求,基础设施需要创新技术来满足不断变化的需求。PCB的设计速率越来越高,随着56Gbps+的需求进来,对PCB layout的要求也越来越高。如100G光模块,就采用了4通道25GbpsNRZ,到200G光模块4通道就可以有56GNRZ和56GPAM4两种方案来选择实现。这两种技术有什么差异呢,对我们的设计有什么影响?

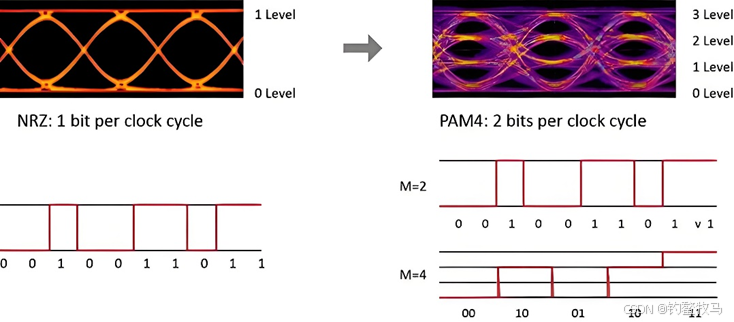

PAM4(4-Level Pulse Amplitude Modulation)即四电平脉冲幅度调制,PAM4信号技术是一种采用4个不同的信号电平来进行信号传输的调制技术。作为下一代高速信号互连的热门信号传输技术,PAM4信号比传统NRZ(Non-Return-to-Zero)信号多了两个电平:NRZ信号采用高、低两种信号电平表示数字逻辑信号的1、0,每个周期可以传输1bit的逻辑信息;PAM4信号则采用4个不同的信号电平进行信号传输,即00、01、10、11,每个周期可以传输2bit的逻辑信息。因此,在相同符号周期内,PAM4信号的比特速率是NRZ信号的两倍。

基本概念了解以后,对于NRZ与PAM4技术的区别和优劣势,采用最近比较火的DeepSeek来看一下吧!

PCB 中 NRZ 与 PAM4 技术的区别与优劣势分析

在高速数字通信领域,NRZ(Non-Return-to-Zero)和 PAM4(4-Level Pulse Amplitude Modulation)是两种主流的信号调制技术。它们在 PCB(印刷电路板)设计中的选择直接影响信号传输效率、功耗和可靠性。以下是两者的核心区别及优劣势对比:

一、核心区别

- 调制原理

- NRZ:采用两个电平(高/低)表示逻辑“1”和“0”,每个符号周期传输 1 比特信息。

- PAM4:采用四个电平(例如 ±A、±3A)表示 2 比特信息(00、01、10、11),每个符号周期传输 2 比特信息。

- 传输效率

- NRZ:比特率等于波特率(如 28 Gbps 对应 28 GBaud),传输效率较低。

- PAM4:比特率为波特率的两倍(如 56 Gbps 仅需 28 GBaud),相同带宽下传输效率翻倍。

- 信号完整性要求

- NRZ:仅需区分两个电平,对噪声和信道失真的容忍度较高,误码率(BER)较低。

- PAM4:四个电平间距更小,对噪声敏感,垂直眼图开口仅为 NRZ 的 1/3,需依赖前向纠错(FEC)补偿误码率。

- 功耗与设计复杂度

- NRZ:硬件实现简单,功耗低,收发器设计成本较低。

- PAM4:需复杂的均衡(如 CTLE、DFE)和 ADC/DSP 架构,功耗更高,且收发器成本增加 20%-30%。

- 适用场景

- NRZ:适用于短距离、低速率(≤28 Gbps)场景,如传感器网络或传统以太网。

- PAM4:专为高速(≥56 Gbps)设计,广泛应用于 400G 以太网、5G 光模块及数据中心互联。

二、优劣势对比

- NRZ

- 实现简单,硬件成本低

- 信噪比(SNR)高,误码率低

- 低功耗,适合短距离传输

- 传输效率低,无法满足56 Gbps以上需求

- 高速时易受码间串扰和时钟漂移影响

- PAM4

- 带宽利用率翻倍,支持 400G 及以上速率

- 兼容现有信道,降低长距离传输损耗

- 标准化程度高,适配5G/数据中心需求

- 对噪声敏感,需复杂均衡和FEC补偿

- 设计复杂度高,功耗和成本增加

- 传输距离受限(通常≤5km)|

三、应用场景选择建议

- NRZ:适合对成本敏感、低速率(如10G/25G以太网)或短距离(PCB内层布线)的场景。

- PAM4:在 400G 光模块、AI 计算集群、5G等高速高带宽场景中更具优势,但需权衡信号完整性设计与成本。

四、未来趋势

随着 224G PAM4 技术的成熟,其将进一步推动数据中心和 AI 应用的带宽需求,但需解决高频损耗(如铜粗糙度)和散热问题。而 NRZ 可能逐步退居特定低速场景,或与 PAM4 形成互补(如混合调制方案)。

如需更详细的实现方案或测试参数,可参考 IEEE 802.3 标准及光模块厂商(如华为、Molex)的技术白皮书。

在大模型回答的基础上,人工补充下:

未来在PCB设计中将会越来越多的遇到PAM4技术,高带宽的光模块将大规模应用该技术,后续如PCIe 6.0 规范也采用了 PAM4 信令,数据速率达到 64GT/s,通过 x16 配置可达到 256Gbps。对于layout而言,采用PAM4的技术以后,同样单对差分速率56Gbps,采用单对差分56GPAM4技术的信道只需要按照常规28GbpsNRZ信道的要求来做要求,比如基材的选型(M6、M6+),铜箔等,包括PCB仿真考虑的基频也均是14GHz。如果是单对差分56GbpsNRZ技术的信道,则需要按照56G来要求,比如基材的选型(M7、M7+),铜箔等,PCB仿真考虑的基频是28GHz。

对于PCIE6.0而言,可以采用同PCIE5.0接近的设计要求,速率可以翻一倍达到64Gbps单对差分。但是采用PAM4技术的信号对收发芯片的均衡能力提出了更大考验,硬件成本更高。

针对layout设计,PAM4技术的信号对噪声异常敏感(眼图窗口变小很多),所以同样做差分设计,PAM4的串扰控制更加严格,比如对于25Gbps信号来说,编码方式是NRZ编码,其实3H是够用的了。如果在同样基频下要跑到56Gbps-PAM4的话,可能需要往5H做,因为PAM4对串扰的要求还是比较高的。

未来大家做设计遇到PAM4技术的信号不要怕,112GbpsPAM4技术的信号砍一刀,就是按常规56Gbps做设计,56GbpsPAM4技术的信号砍一刀,就可以按照常规28Gbps来做!是不是难度小多了。

7038

7038

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?