点击蓝字关注我们

关注、星标公众号,精彩内容每日送达

来源:网络素材有多种类型的时序违例可归类为脉冲宽度违例。

最大偏差违例

最小周期违例(本文详解之重点)。

最大周期违例

低脉冲宽度违例

高脉冲宽度违例

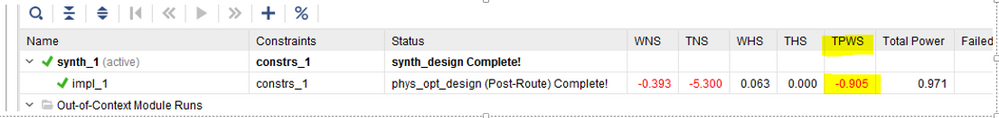

如需了解脉冲宽度违例的详情,请参阅“报告时序汇总”(Report Timing Summary) 的“TPWS”部分。

最严重的脉冲宽度违例在报告中显示为 WPWS。

如需了解脉冲宽度违例的详情,请在 Vivado GUI 中打开脉冲宽度违例报告(单击“Reports” - > “Timing” - > “Report Pulse Width”)或使用以下 Tcl 命令打开此报告:

report_pulse_width

最小周期违例

本文仅介绍“最小周期违例”相关内容。

报告描述:

在脉冲宽度报告中,将检查所有时钟的最小脉冲宽度要求。

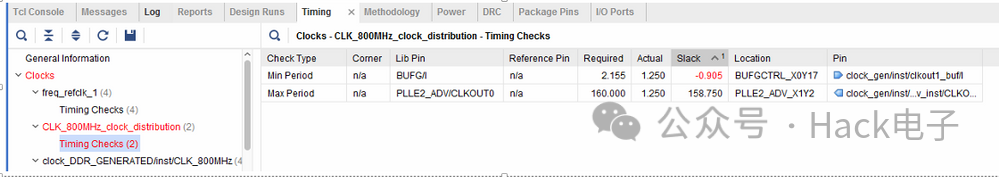

最小周期违例示例:

举例来说,GUI 中打开的报告描述如下所示:

以上示例显示了特定时钟的最小周期 (Min Period) 和最大周期 (Max Period) 要求。

可以看到,针对“Min Period”,裕量 (Slack) 为负值。

此违例现象必须解决,才能避免出现脉冲宽度违例。

在此示例中,显示的预期值 (Required) 为 2.155ns,实际值 (Actual) 为 1.250ns,这两个值均为对应于检查类型 (Min Period) 的值。“Slack”列显示的值即为这两者的差值(Slack = Actual 值 - Required 值)。

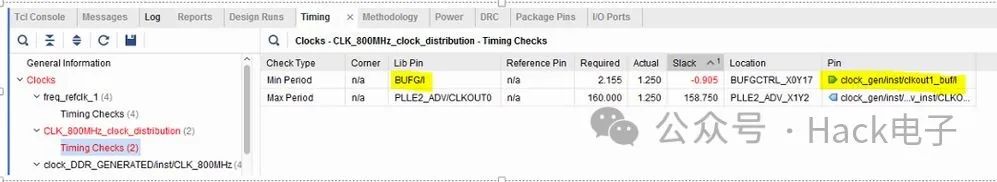

解决办法:

在此示例中,负 Slack 值 -0.905ns 位于 BUFG 的输入引脚 (Lib Pin: BUFG/I) 上。

要解决此违例,必须检查此特定器件系列的 AC 和 DC 特性,其中将显示 BUFG 允许的最大频率。

由于这是硅片层面的限制,您将需要调低频率才能解决此违例。

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索

2387

2387

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?