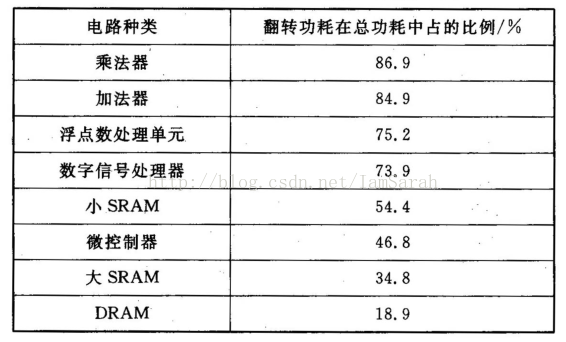

这篇文章主要介绍一下低功耗设计中常用的技术。由上篇文章可知,设计中的功耗可以分为下表给出了翻转功耗在一些示例电路中所占的比例。

在不同电路中,各类功耗所占的比例是不同的,因此进行低功耗设计的重点是不同的。在运算电路中,开关功耗占绝大部分,因此,此类电路的低功耗设计要致力于减小开关功耗;对于DRAM存储器,泄漏功耗占大部分,因此要将重点放在减小泄漏功耗上面。

针对不同的功耗类型,具有不同的低功耗设计方法。

对于动态功耗:可以从降低物理电容、工作电压、频率、翻转概率来着手。

对于静态功耗:可以从增加阈值,降低栅极电流来着手。

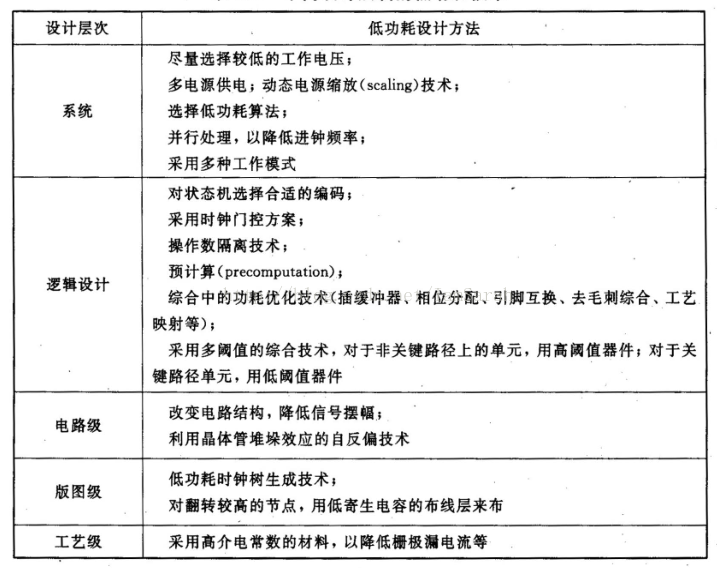

低功耗设计贯穿整个IC设计的流程,下表给出不同层次的功耗降低方法:

下面也分层次详细的介绍一下功耗降低的技术。

(一)系统级的低功耗设计

1)电源缩放技术

电源缩放技术是降低功耗的最直接的技术。在系统设计时,尽量采用低电压。低电压可以显著降低功耗,但会引起性能下降。为了不显著影响性能,可以采用电压设计方案,即将设计分成区域,每个区域采用不同的供电电压。多电压设计需要综合库的支持。综合库中,要包含同一单元在不同电压下的描述。此外要给出多电压设计单元。多电压设计单元是一类特殊的器件,主要包括:

a、电压转换器:用于不同电压域之间传递信号。

b、电源个例单元:避免单元的输入悬空。

c、保值寄存器:在不工作模式下,将寄存器的状态保留起来。

2)低功耗IP的选择

现在的SOC设计依赖于IP的集成。在选择IP的时候,既要考虑性能要求,还需要考虑功耗问题。例如在选择CPU的同事,可以分析在完成相同功能时,哪种CPU功耗大。

本文深入探讨了集成电路中的低功耗设计方法,包括电源缩放、低功耗IP选择、并行处理、流水线技术、状态编码、低功耗算法等系统级设计策略,以及时钟门控、操作数隔离、逻辑级功耗优化等RTL级设计技术,旨在减少动态和静态功耗,实现高效节能的IC设计。

本文深入探讨了集成电路中的低功耗设计方法,包括电源缩放、低功耗IP选择、并行处理、流水线技术、状态编码、低功耗算法等系统级设计策略,以及时钟门控、操作数隔离、逻辑级功耗优化等RTL级设计技术,旨在减少动态和静态功耗,实现高效节能的IC设计。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1812

1812

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?