书接上文(点击查看前文:浅论芯片低功耗的设计实现(上)),在低功耗的道路上,看看还有什么大招可以用

Vt cell的应用

从上一篇文章可以看到,不同Vt下的cell特性是不同的,现在的工艺都会提供不同倾向的Vt库,见下表

| Vt-Type | speed | Leakage Power | pin compatible | priority | performence scenario |

|---|---|---|---|---|---|

| SVT | normal (1) | low (1) | yes | high | common |

| LVT | fast (1.5) | medium (1.5) | yes | medium | high frequency path |

| Ultra-LVT | fastest (3) | high (4.5) | yes | low | very critical path |

可以看到,合理使用不同的Vt cell可以满足不同PPA的需求,在使用过程中,应该优先使用SVT的cell,而后是LVT,最后万不得已的时候再使用ULVT(ULVT的leakage可不是一般的大啊,一般会达到SVT的四到五倍的量级)

工具可以完美支持mix-Vt的设计。工具的策略是,在功耗优化的过程中,根据用户设定的Vt等价置换规则,在不影响timing的情况下,选择leakage小的cell,这样在兼顾性能的时候可以满足power的需求。

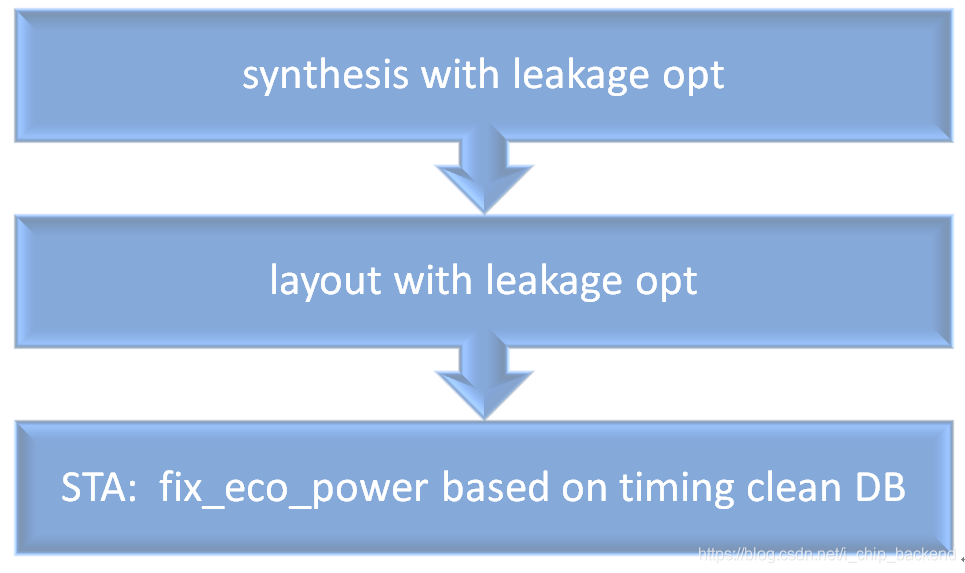

由于,后端实现的时候,通常由三个阶段需要用到这个技术手段,这里给出一个通常的应用场景供大家参考

秘籍:一定要做最后一步,效果会非常显著,可以有效地提高leakage power。

版图优化

在版图实现当中,后端实现的工具是非常灵活的,低功耗的设计当中,经常会使用到power-domain和voltage-area这些技术来优化power,简单的讲,通过UPF,在设计里边定义一些switch-off power和always domain,在某些功能不使用的时候,就把SW domain关掉,这个时候,SW里的power-gating cell的输出会呈现出一个无线接近电源(footer power-gating)或者地(header power-gating)的状态,从而理论上确保了SW domain的leakage是零(但是,这是指理论的,由于power gating cell本身会有漏电的问题,所以零的漏电只是理论上的)。

这里可以引申出一系列的思路,版图工程师可以尽可能的让更多的cell放到SW domain,从而在实际使用的情境下,可以拿到更好的功耗。看一下这个例子:

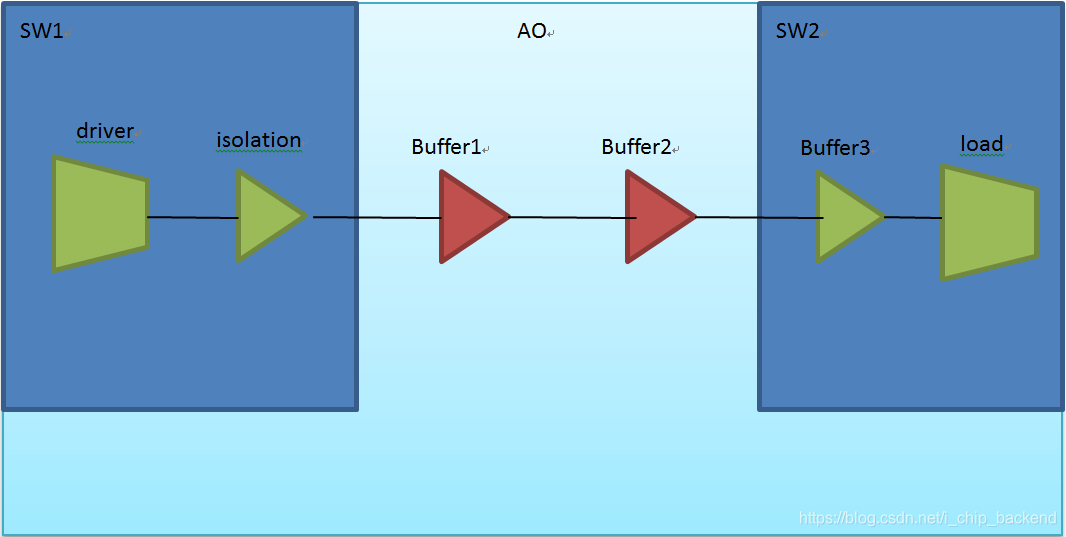

一条路径,从SW1出发到达SW2,中间一共有四级,其中SW里边有一个buffer和一个isolation,AO里边,有两个buffer ,从power上讲,在SW1和SW2同时关断的时候,这两个AO的buffer,不会有任何的动态功耗(dynamic power),这是因为SW1的isolation的输出已经被钳位(clamp)到无效态(一个常值),但是这两个buffer的leakage power是不能省略的,所以下图的floorplan,从power优化上来讲一定是个更好的选择

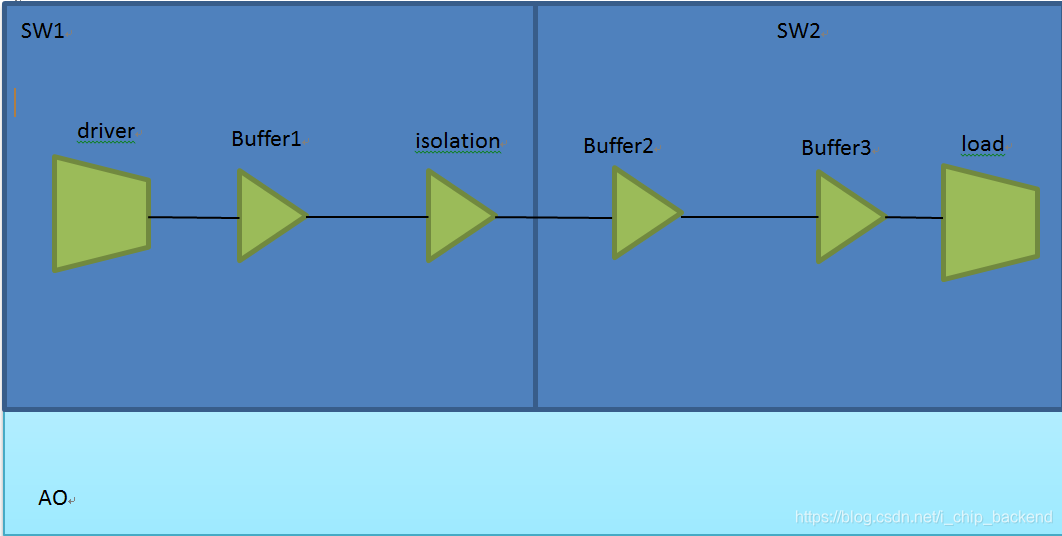

可以看到,中间的级数没有发生改变,但是之前的buffer1和buffer2,都已经被放置到了SW domain了,这样,在SW关断的时候,这两个buffer的leakage power就是零(理论上)。这里只是一个连接和两个buffer的示例,实际中VA之间的连接非常复杂,通过版图的优化调整,可以让出更多的leakage power。

低功耗设计是一套完整的理论体系,从原理、代码、UPF、综合、版图等等,每个步骤的一点点提高,都会带来不同程度的优化,勿以优化小而不为,点点滴滴的进步就会造就更加节能的芯片实现。

本文围绕芯片低功耗设计展开,介绍了Vt cell的应用,指出合理使用不同Vt cell可满足不同PPA需求,工具能支持mix - Vt设计。还阐述了版图优化,通过UPF定义相关域,将更多cell放入SW domain可优化功耗,强调低功耗设计各步骤优化的重要性。

本文围绕芯片低功耗设计展开,介绍了Vt cell的应用,指出合理使用不同Vt cell可满足不同PPA需求,工具能支持mix - Vt设计。还阐述了版图优化,通过UPF定义相关域,将更多cell放入SW domain可优化功耗,强调低功耗设计各步骤优化的重要性。

1246

1246

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?