1、资源

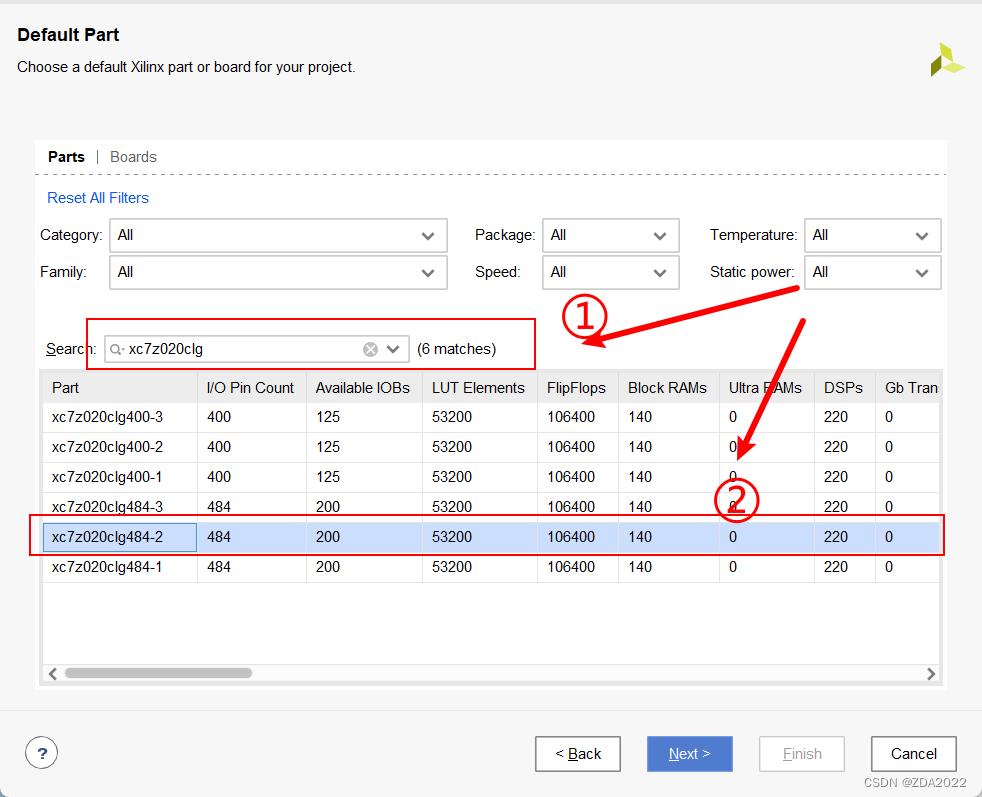

开发板:zynq7020(zc7z020clg484-2)

vivado:2019.1

2、基础结论

①官方评估版PL端无时钟clk,需要提供ps给pl端时钟

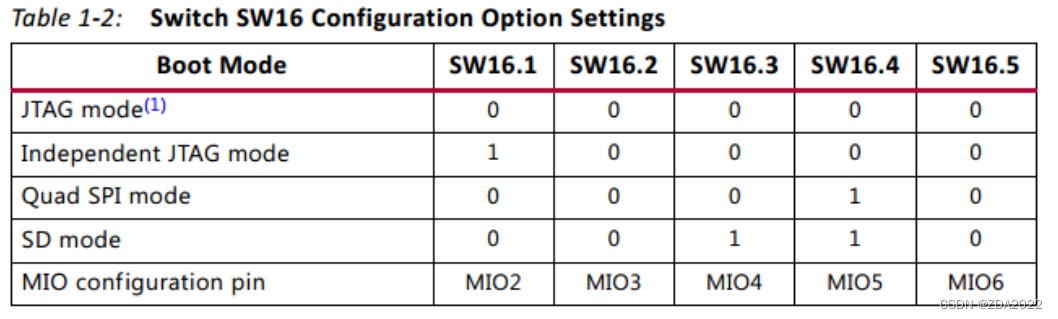

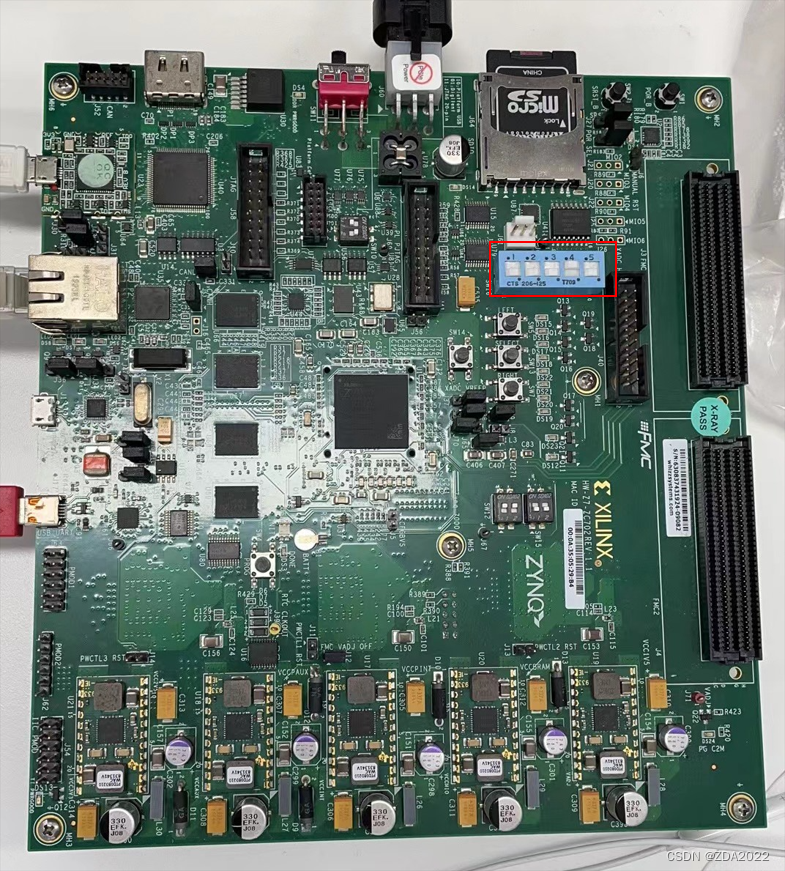

②开发板有几种启动方式,通过拨码开关控制,本文通过JTAG(10000)

3、vivado基本流程

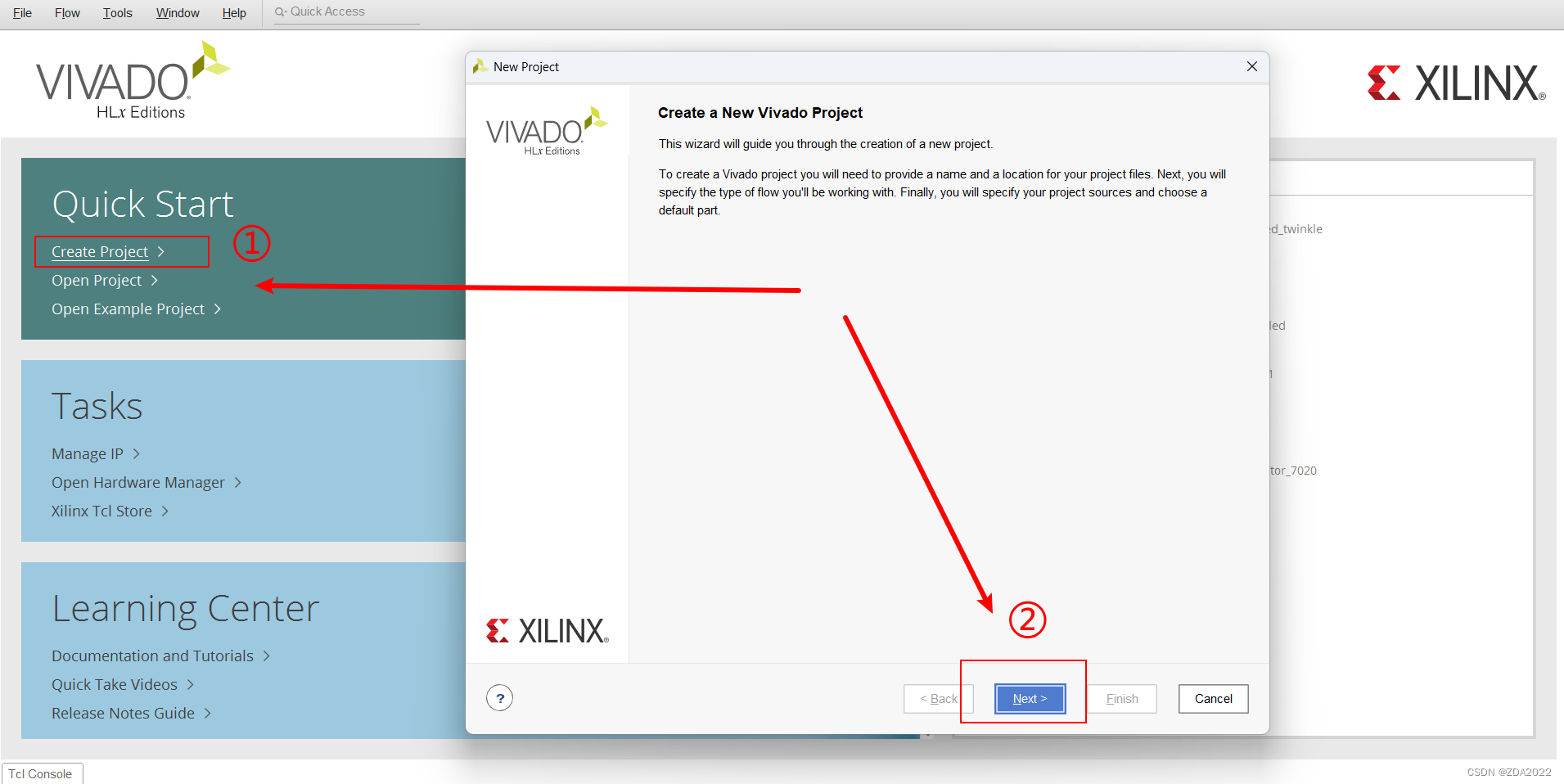

1、双击打开vivado2019.1

2、创建新工程

3、为新工程命名并指定路径

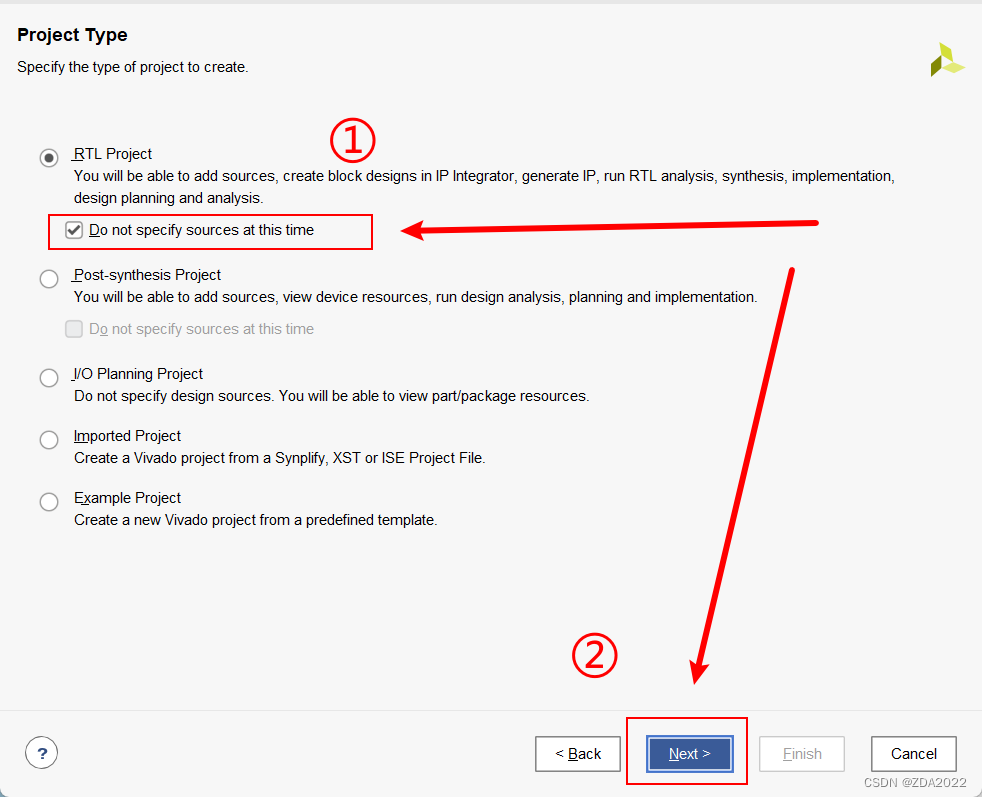

4、指定工程先不添加源文件,在工程内部再编辑

5、选择板子型号(xc7z020clg484-2)

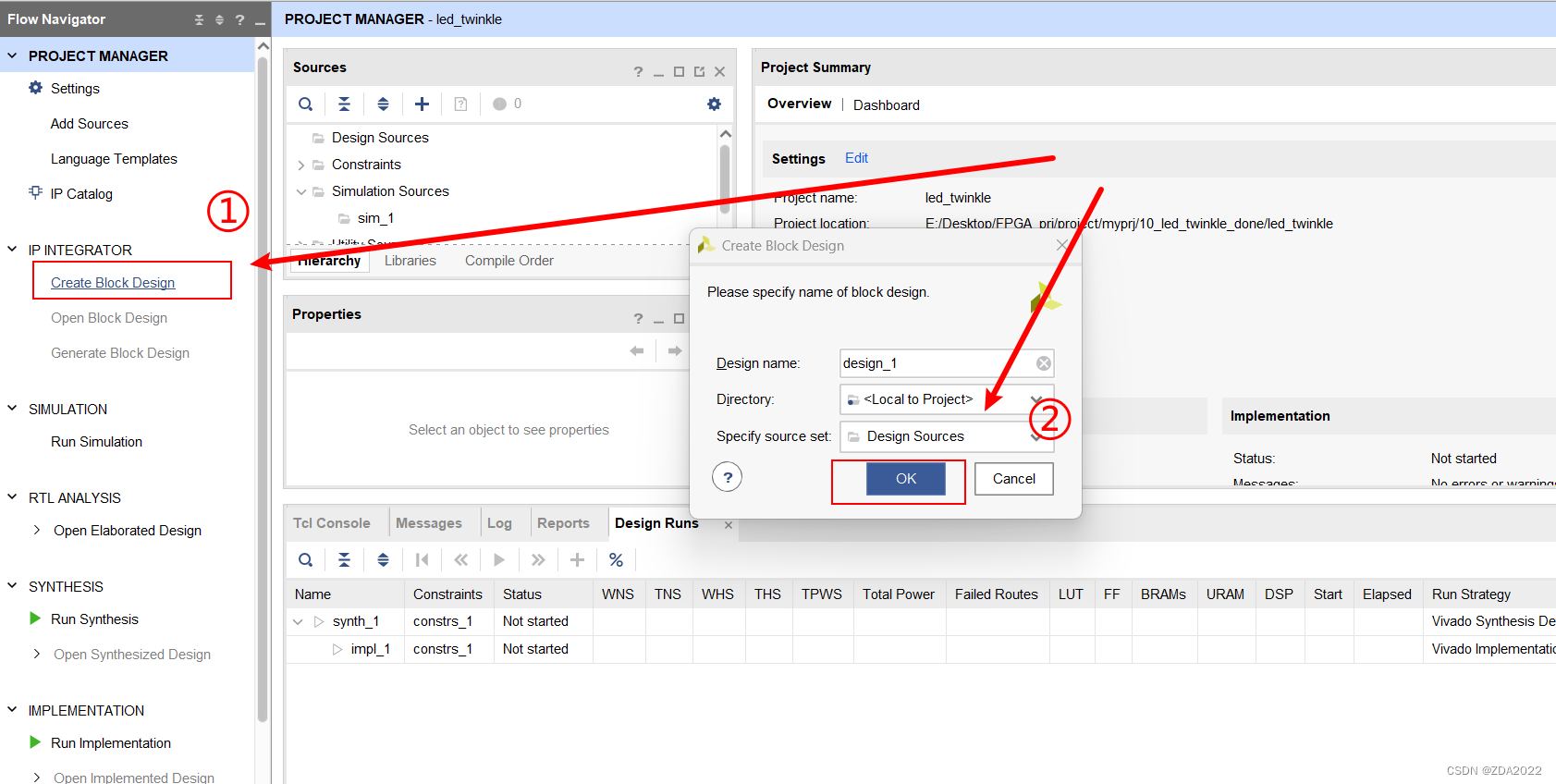

6、create block design->OK

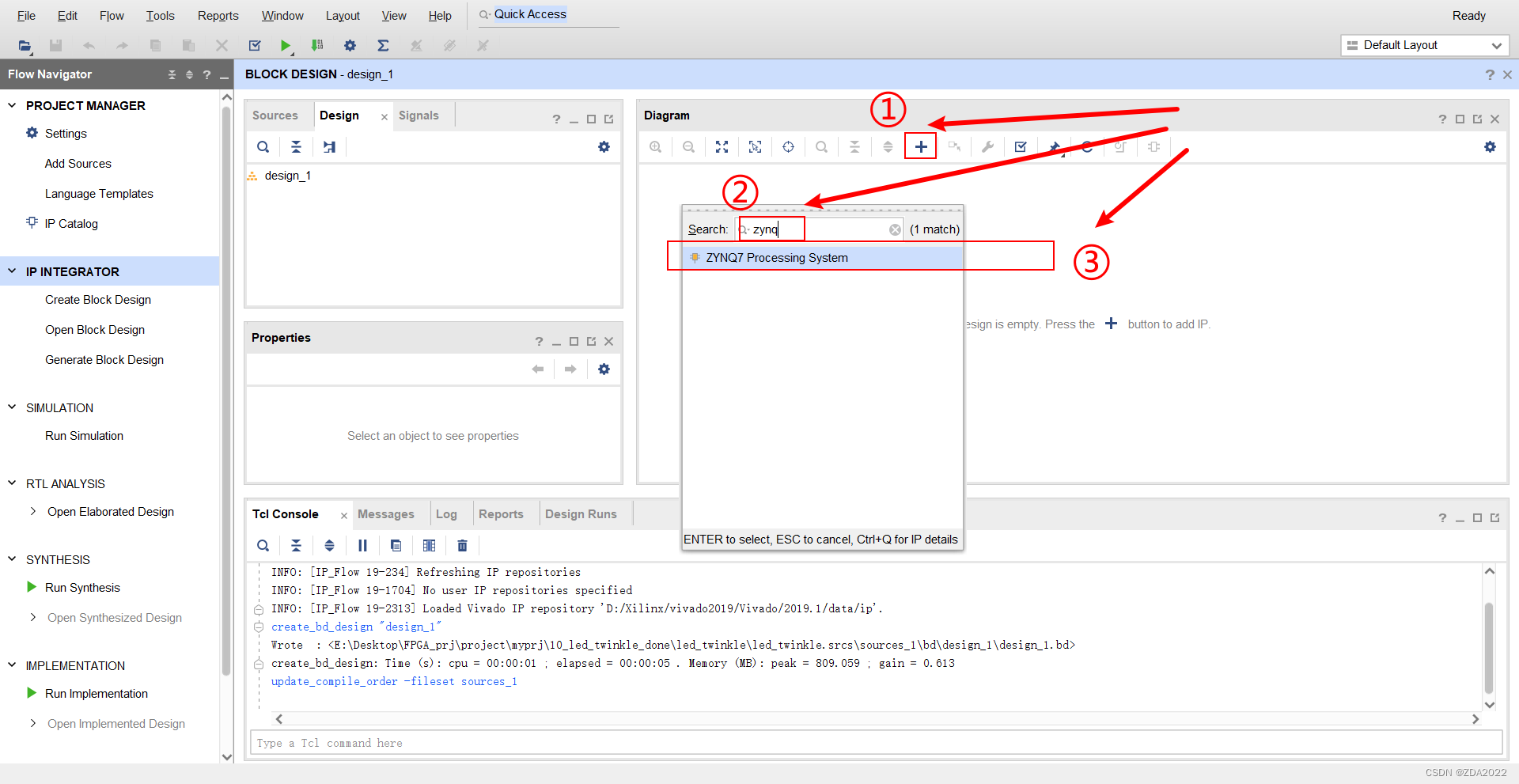

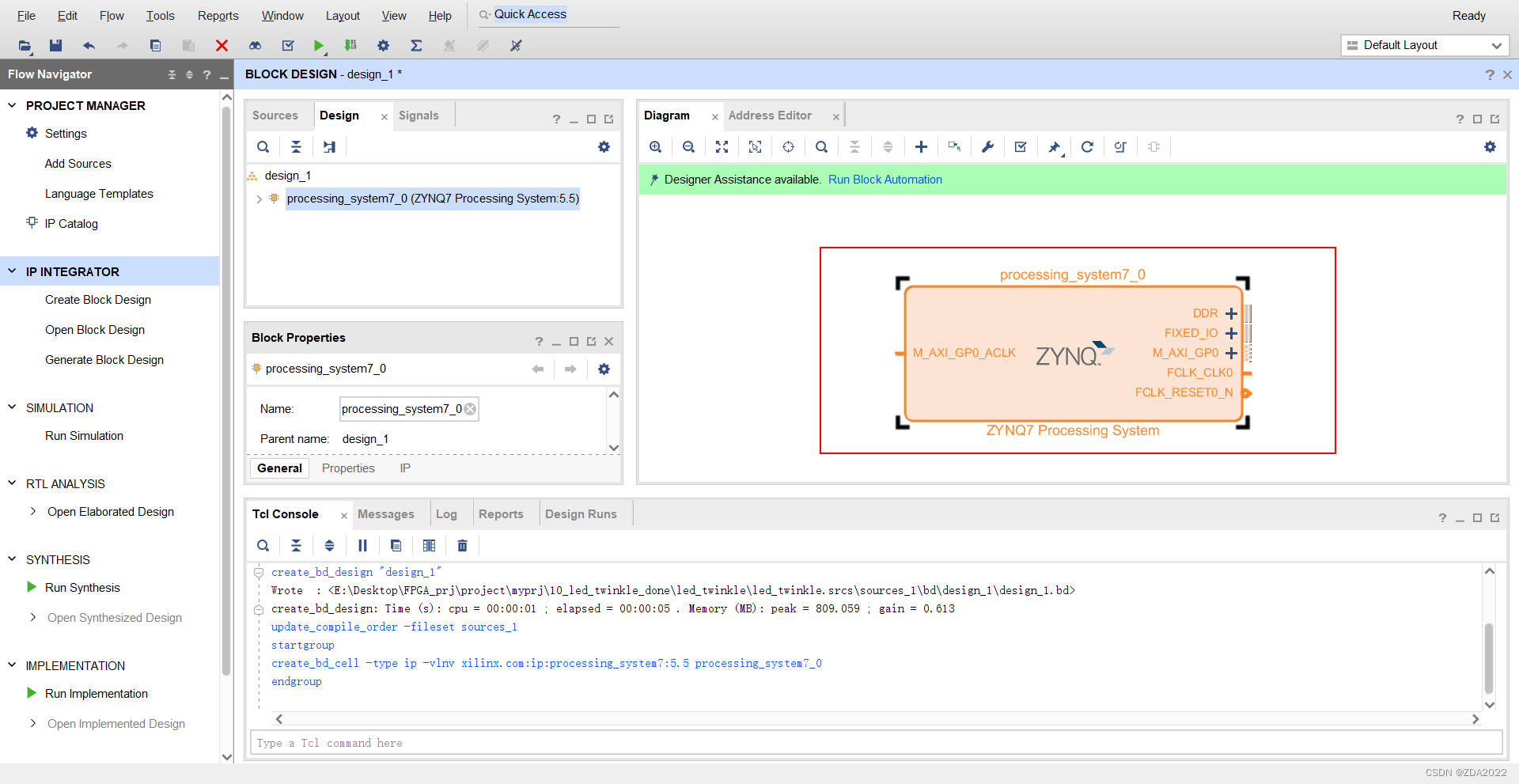

7、添加zynq

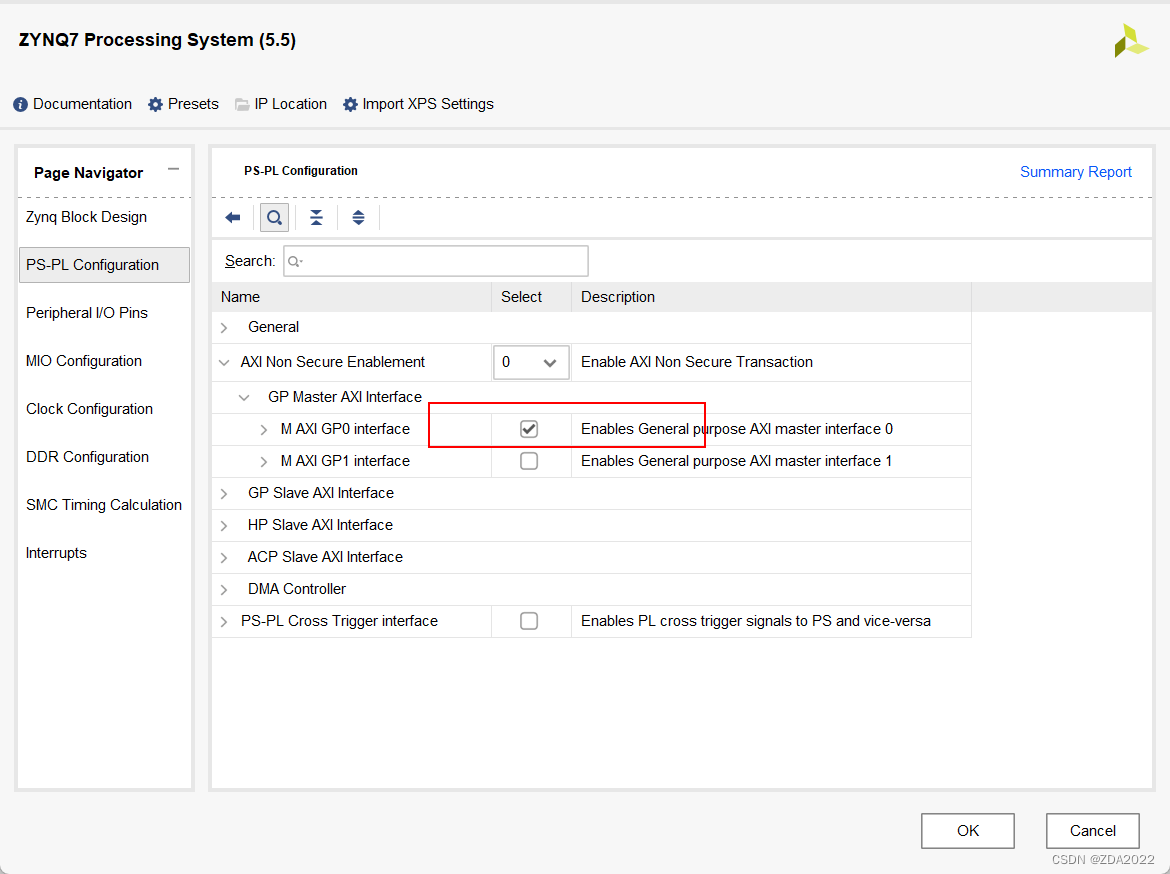

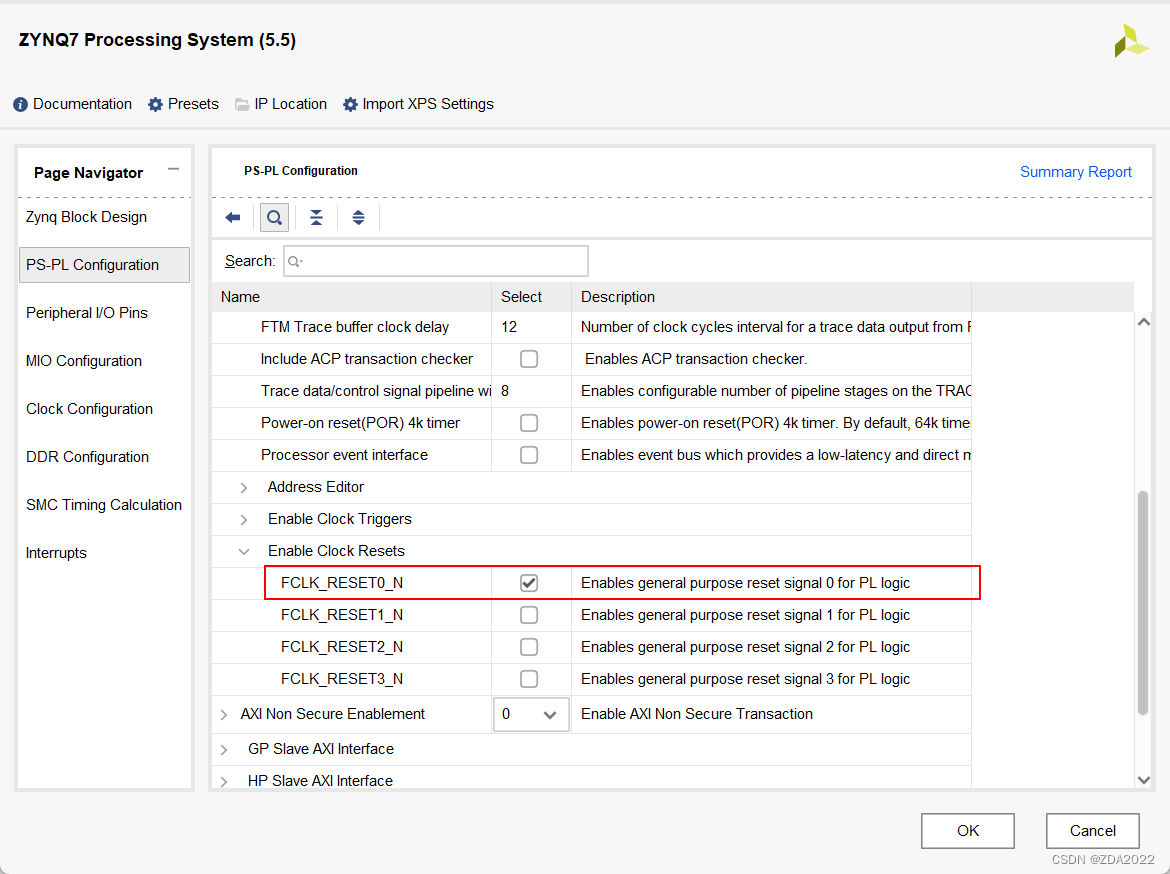

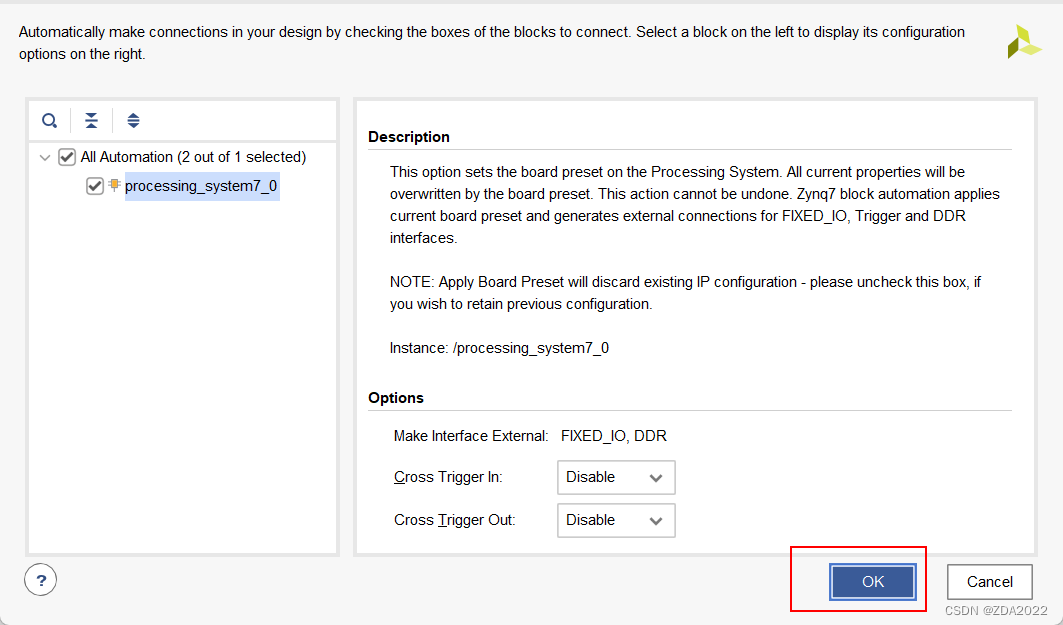

8、双击配置zynq(删除M_AXI_GP0 interface与FCLK_RESET0_N,让后OK退出)

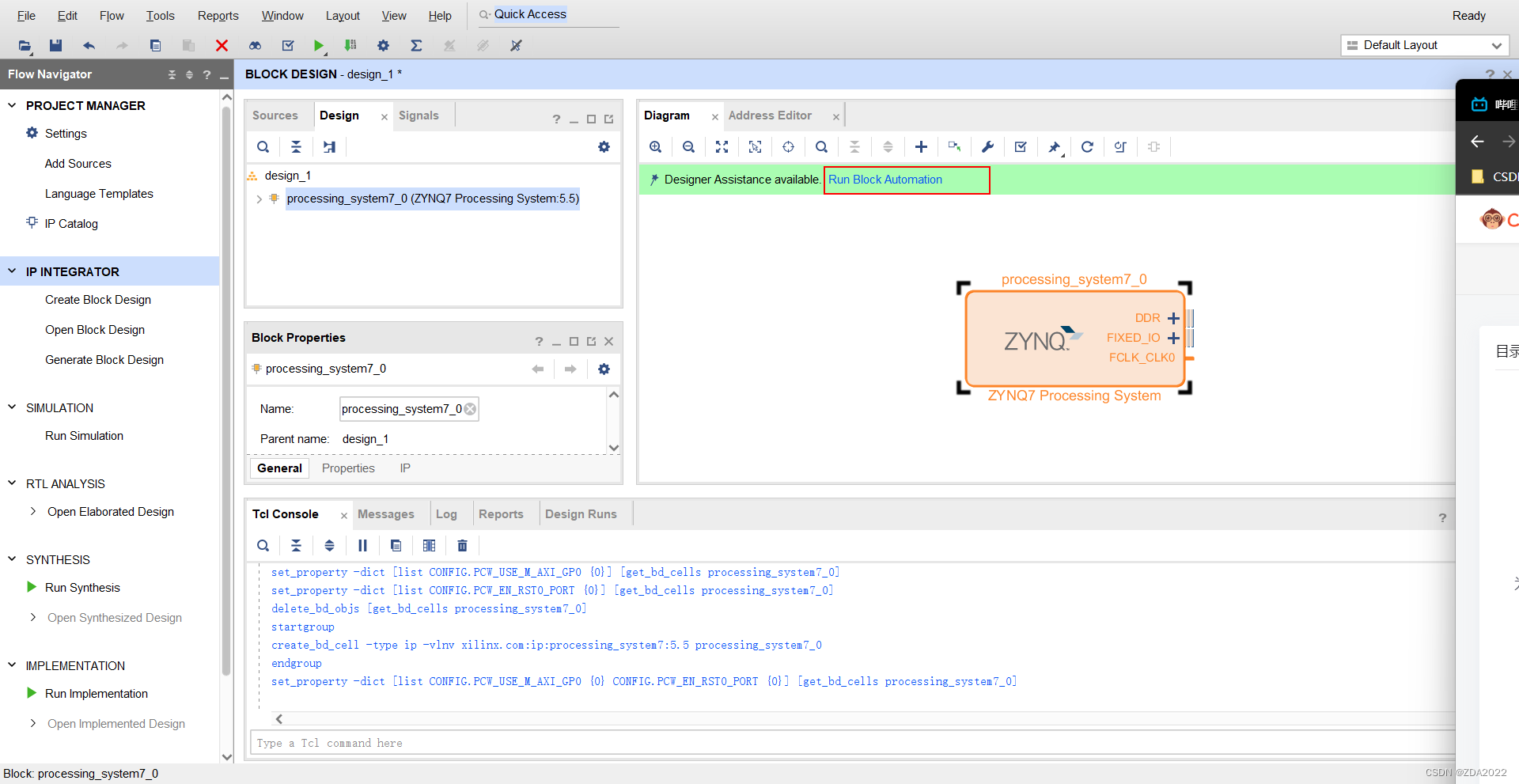

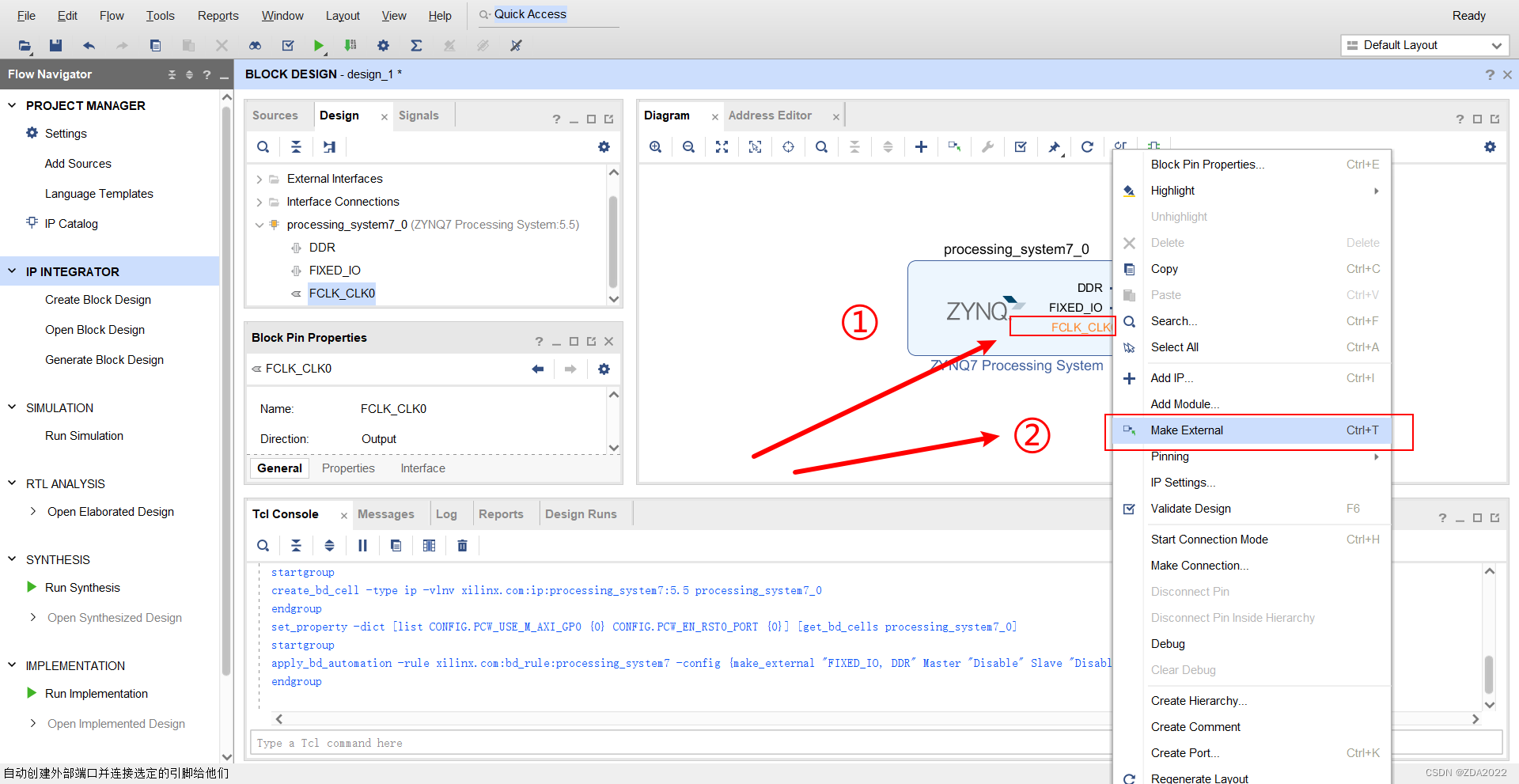

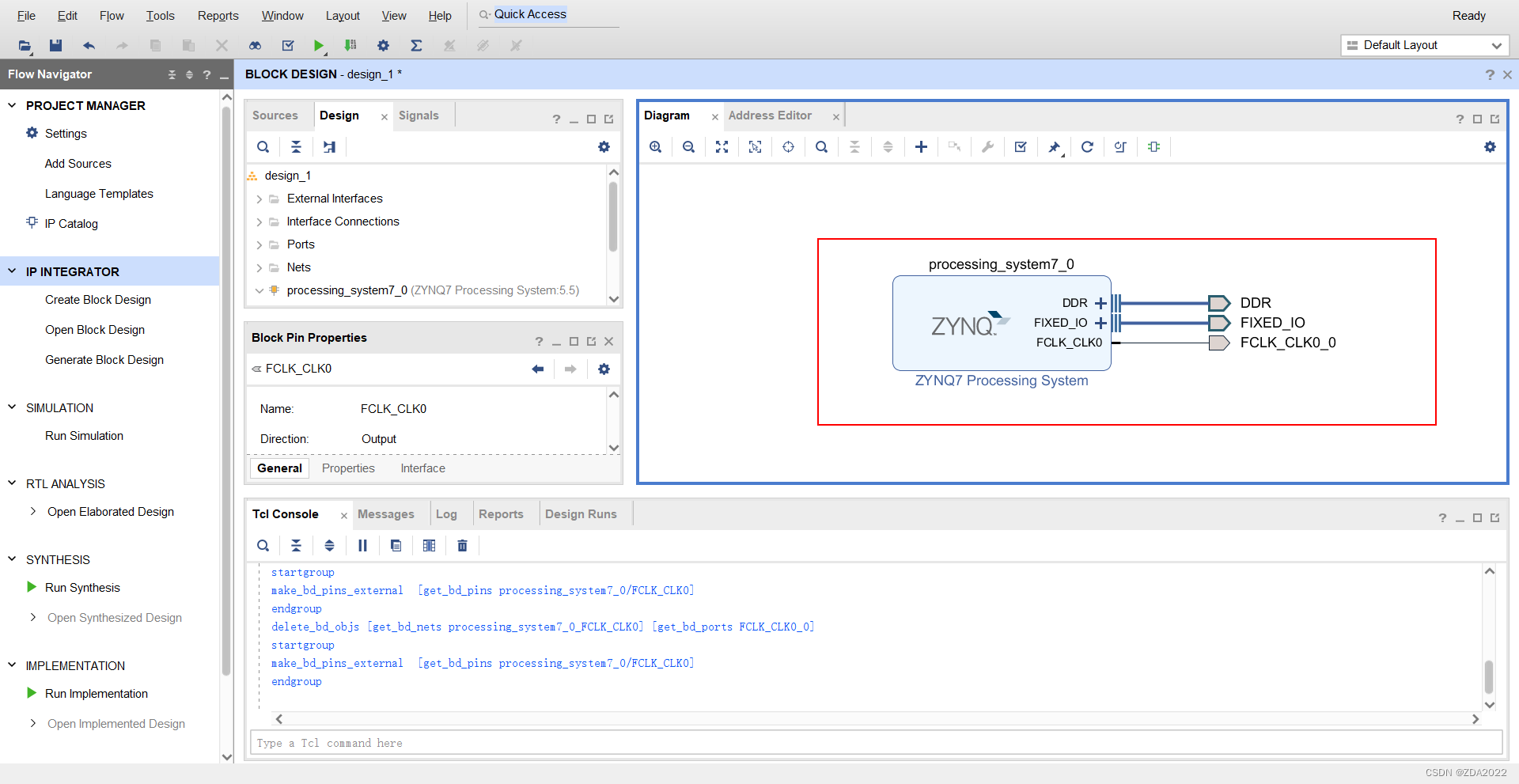

9、自动布局布线并添加引脚(右击FCLK_CLK0,并make externel)

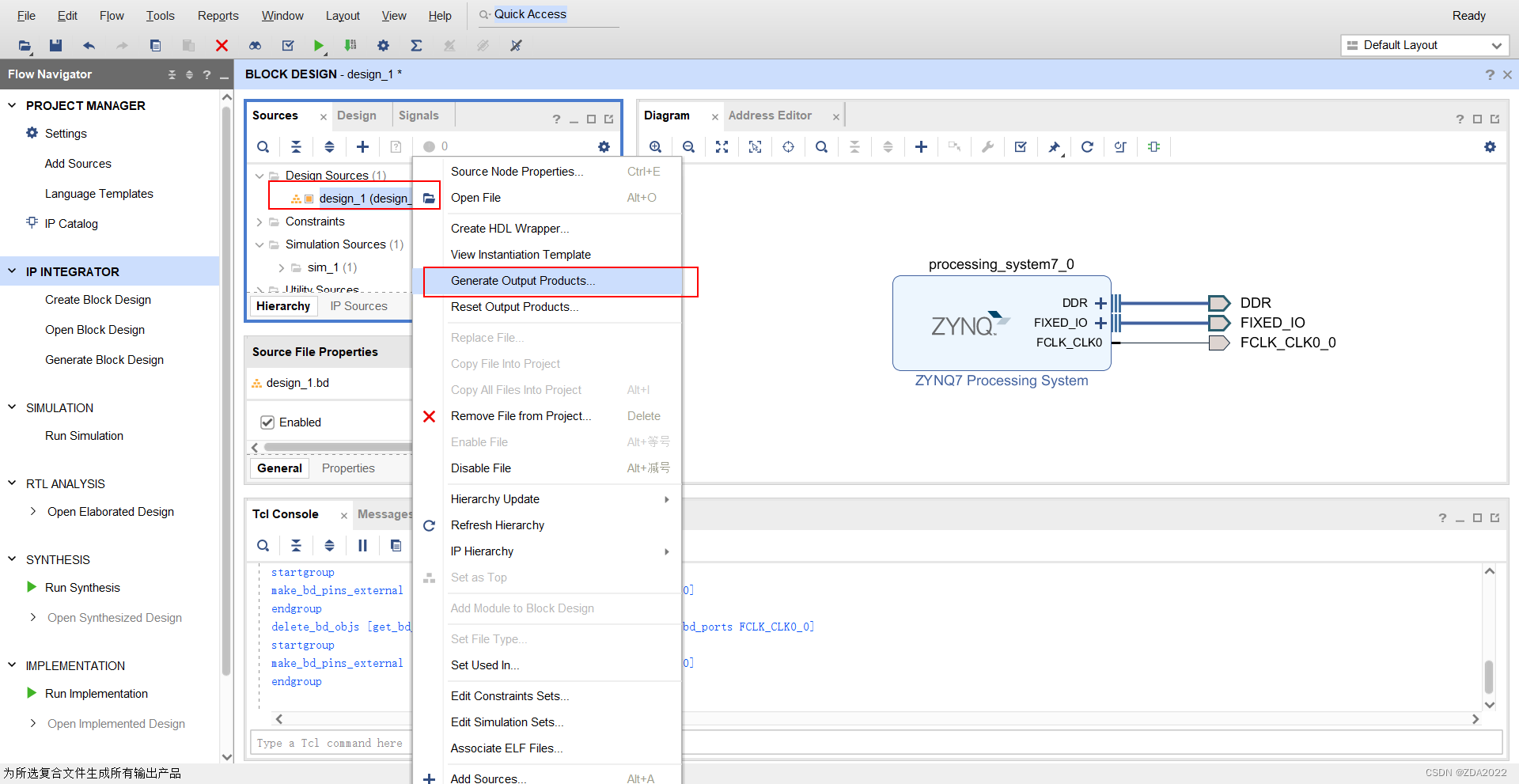

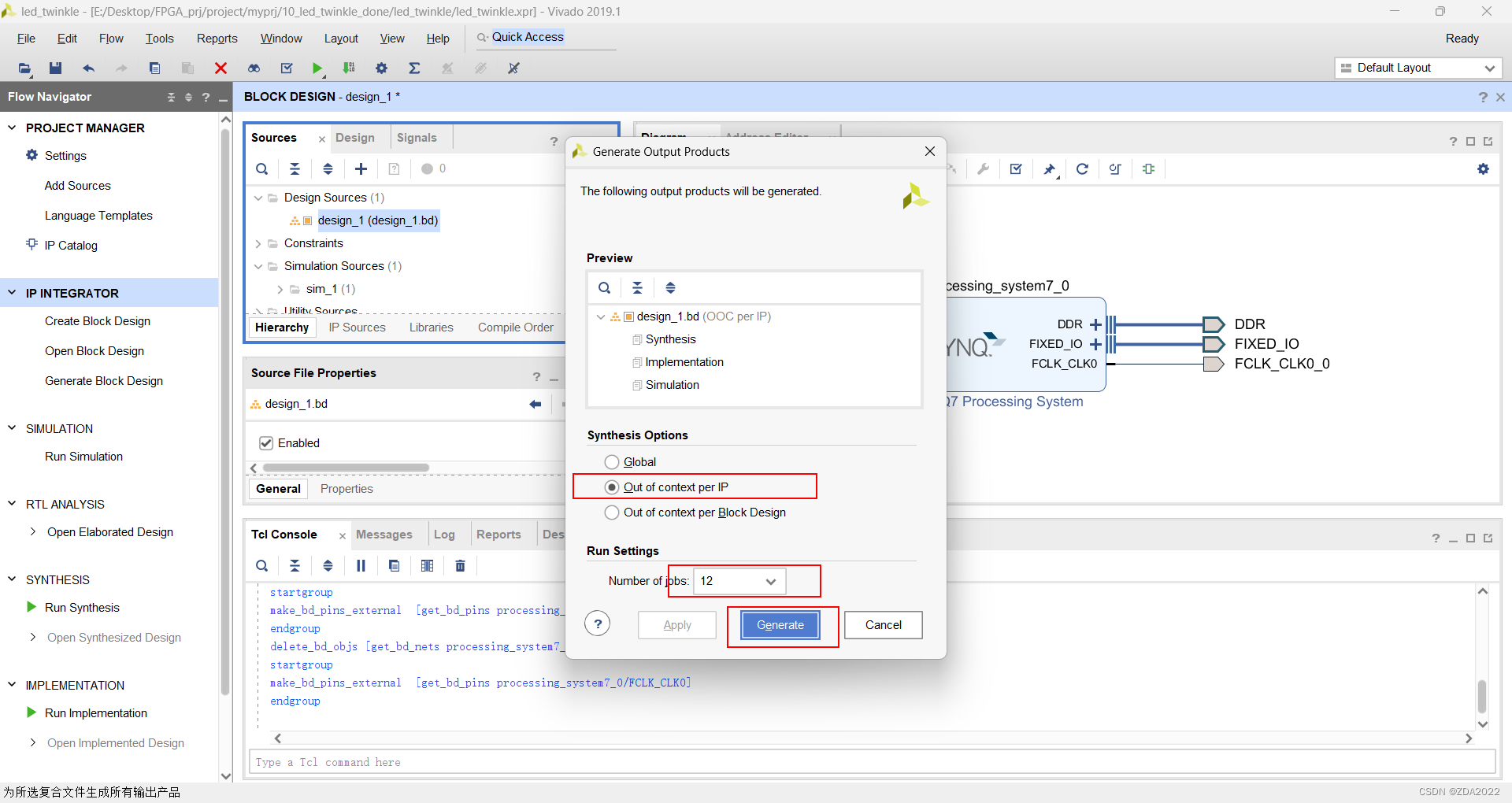

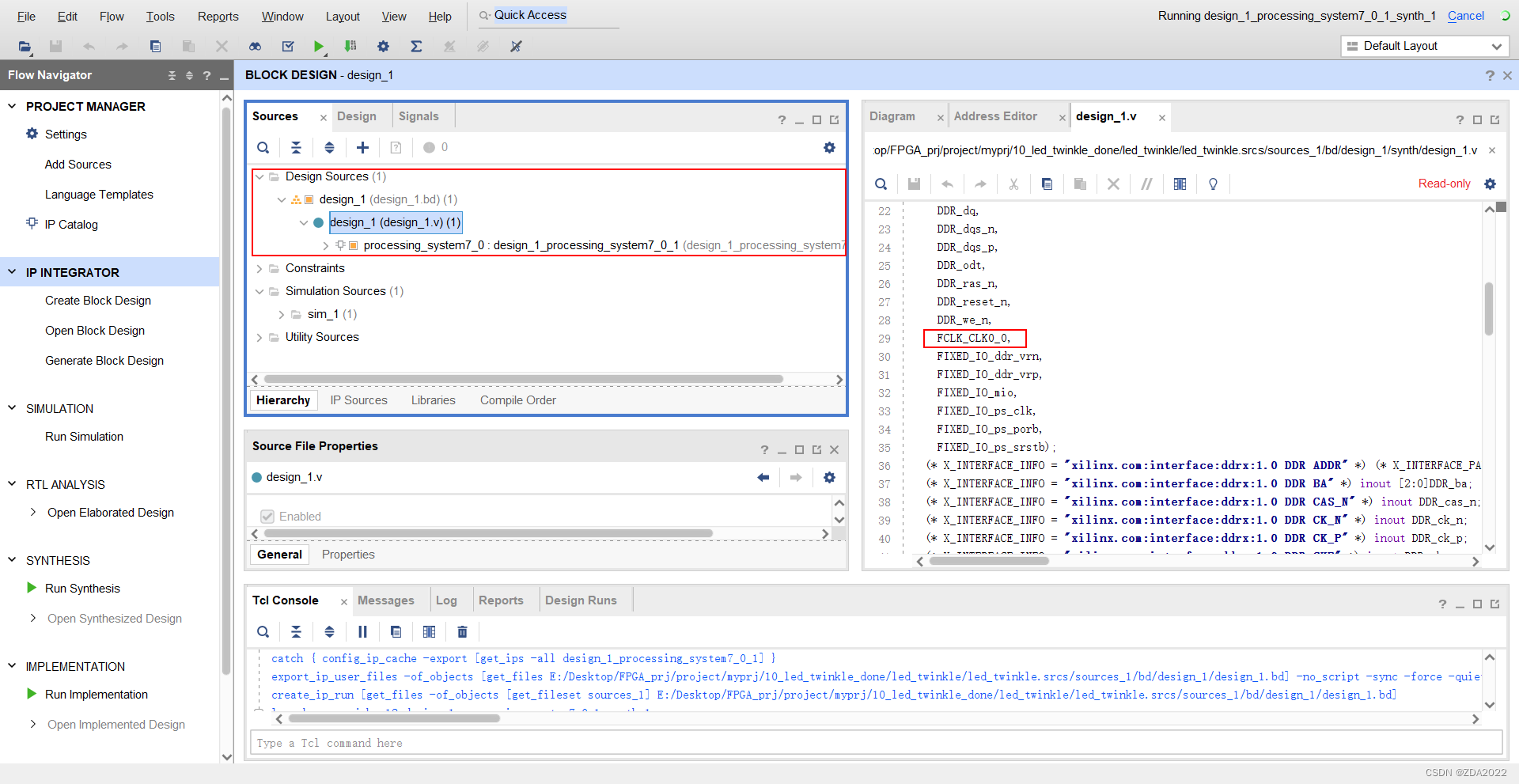

10、生成design_1文件,右击design_1,并general output products

其中的FCLK_CLK0_0即为PS端给PL的时钟

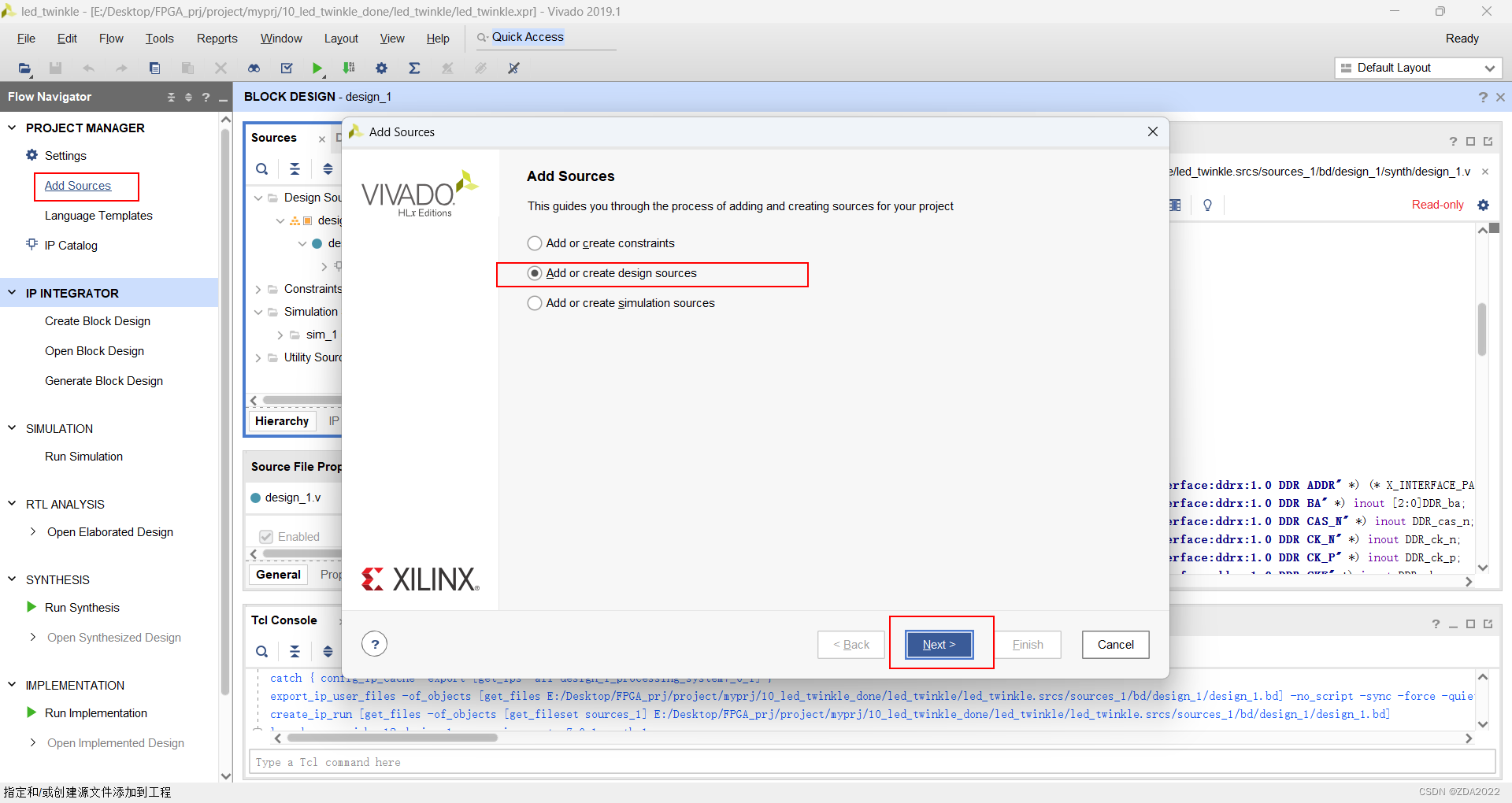

11、编写led的verilog代码

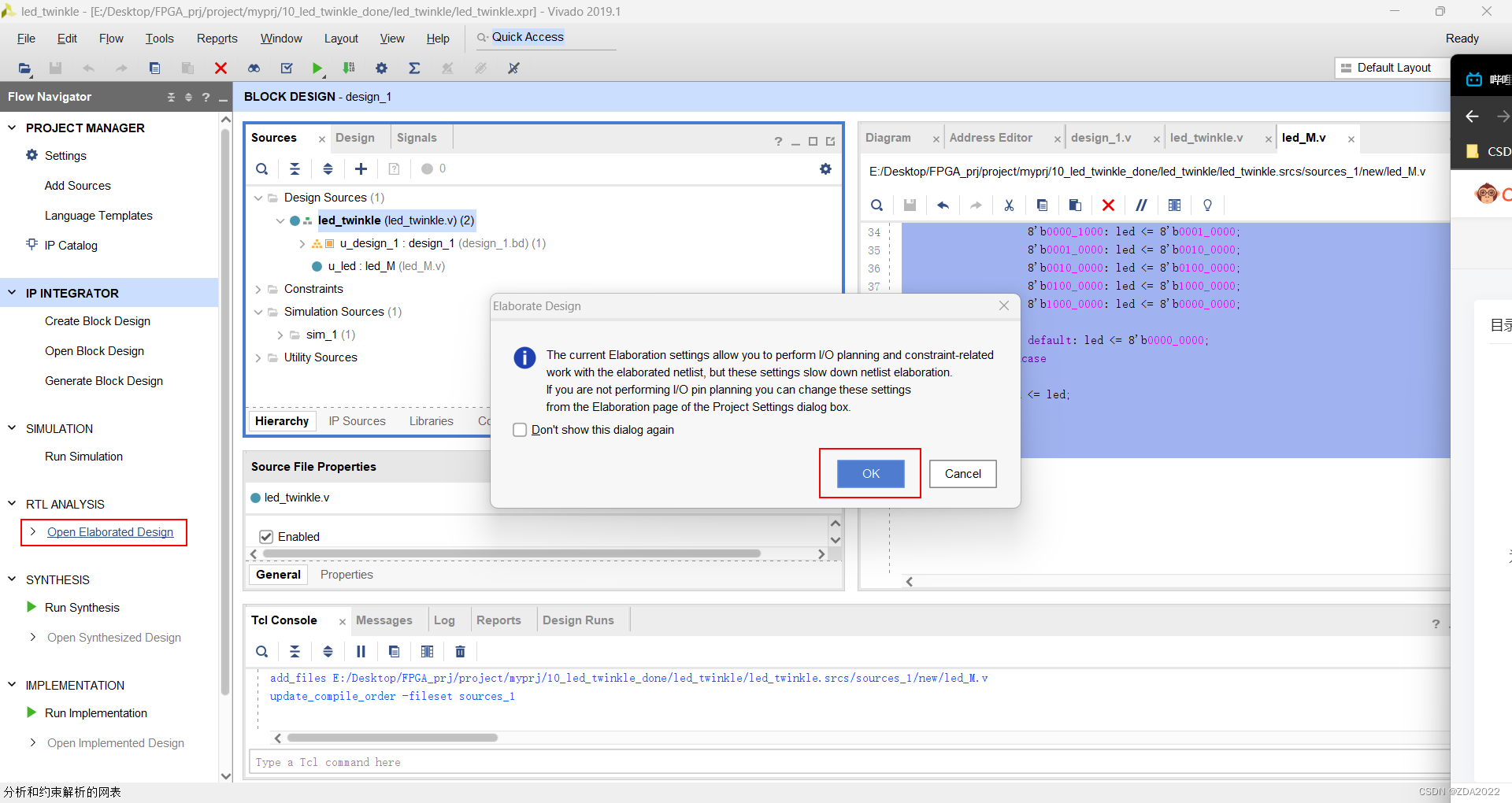

其中led_twinkel例化了design_1.v与led_M模块

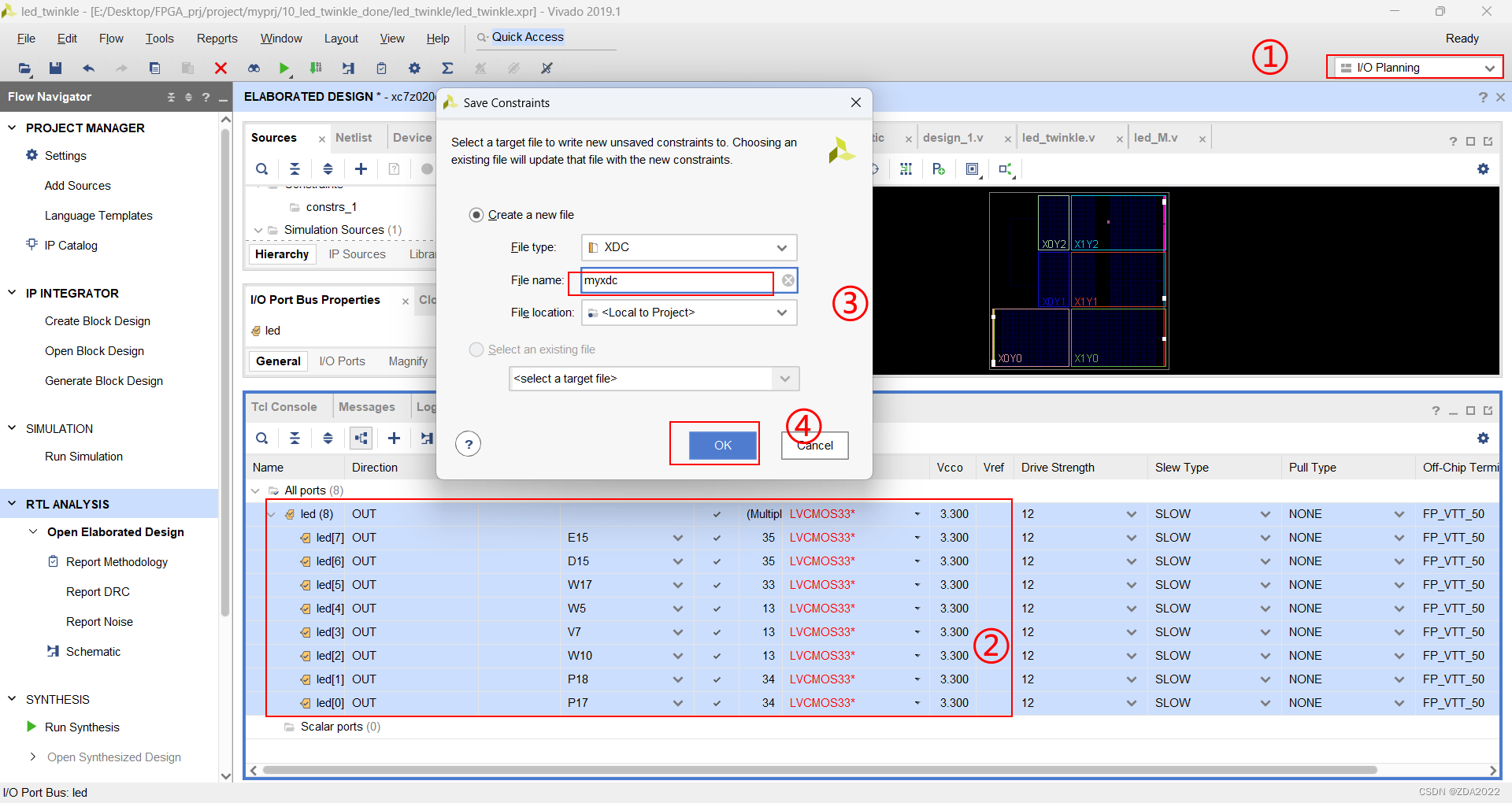

module led_twinkle( //output output[7:0]led ); parameter times = 28'b0010_1111_1010_1111_0000_1000_0000; wire clk;//时钟 50M design_1 u_design_1( .FCLK_CLK0_0(clk) ); //assign led = 8'b0; led_M #(.times(times)) u_led ( .clk (clk), .rst_n (1'b1), .led (led) ); endmodulemodule led_M #(parameter times = 28'b1111_1111_1111_1111_1111_1111_1111) ( input clk, input rst_n, output reg [7:0]led ); reg [27:0]cnt = 28'b0; always@(posedge clk or negedge rst_n) begin if(!rst_n) cnt <= 28'b0; else begin if(cnt >=times) cnt <= 28'b0; else cnt <= cnt + 1; end end always@(posedge clk or negedge rst_n) begin if(!rst_n) led <= 8'b0; else begin if(cnt >=times) case(led) 8'b0000_0000: led <= 8'b0000_0001; 8'b0000_0001: led <= 8'b0000_0010; 8'b0000_0010: led <= 8'b0000_0100; 8'b0000_0100: led <= 8'b0000_1000; 8'b0000_1000: led <= 8'b0001_0000; 8'b0001_0000: led <= 8'b0010_0000; 8'b0010_0000: led <= 8'b0100_0000; 8'b0100_0000: led <= 8'b1000_0000; 8'b1000_0000: led <= 8'b0000_0000; default: led <= 8'b0000_0000; endcase else led <= led; end end endmodule12、分配引脚

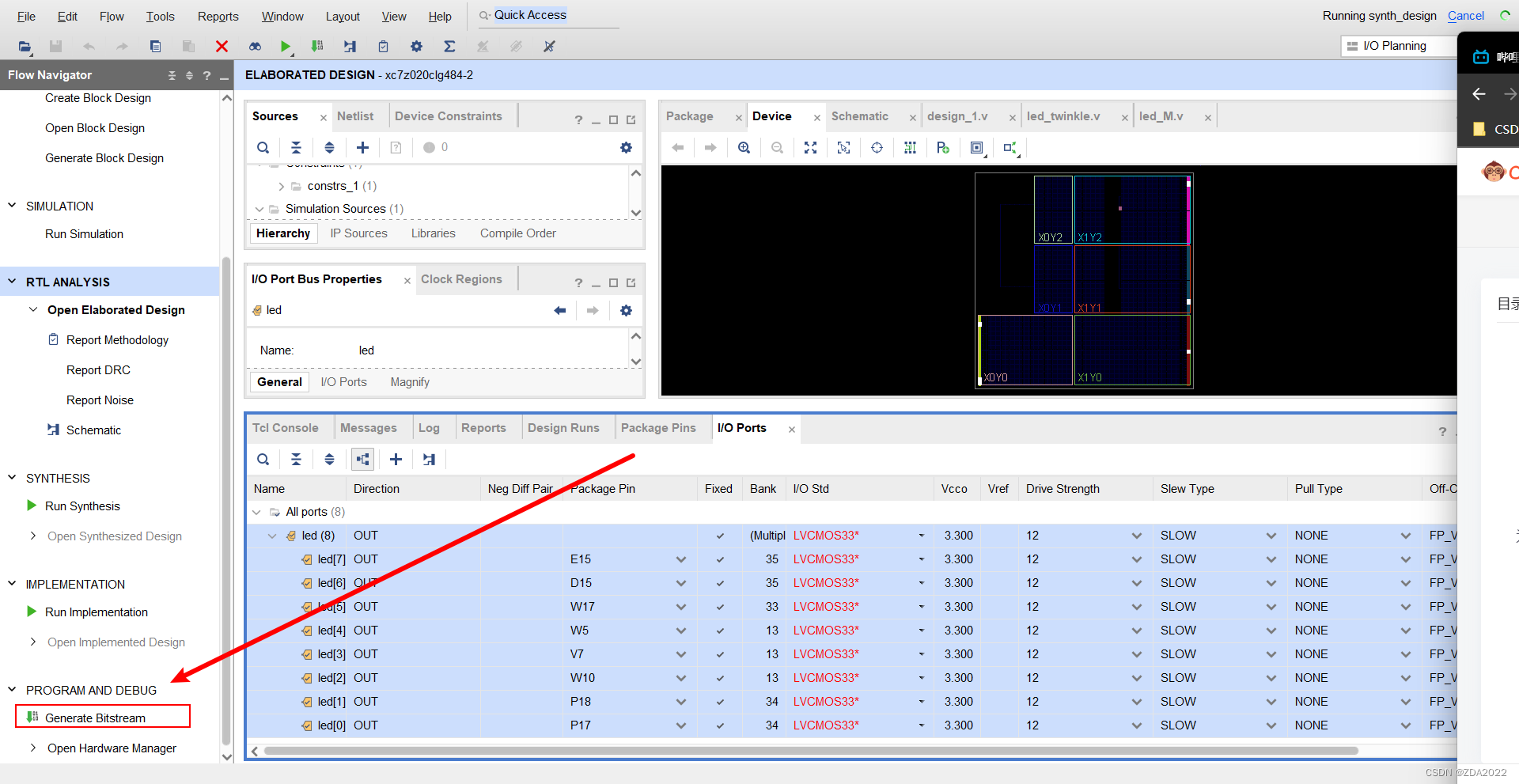

13、生成bit文件

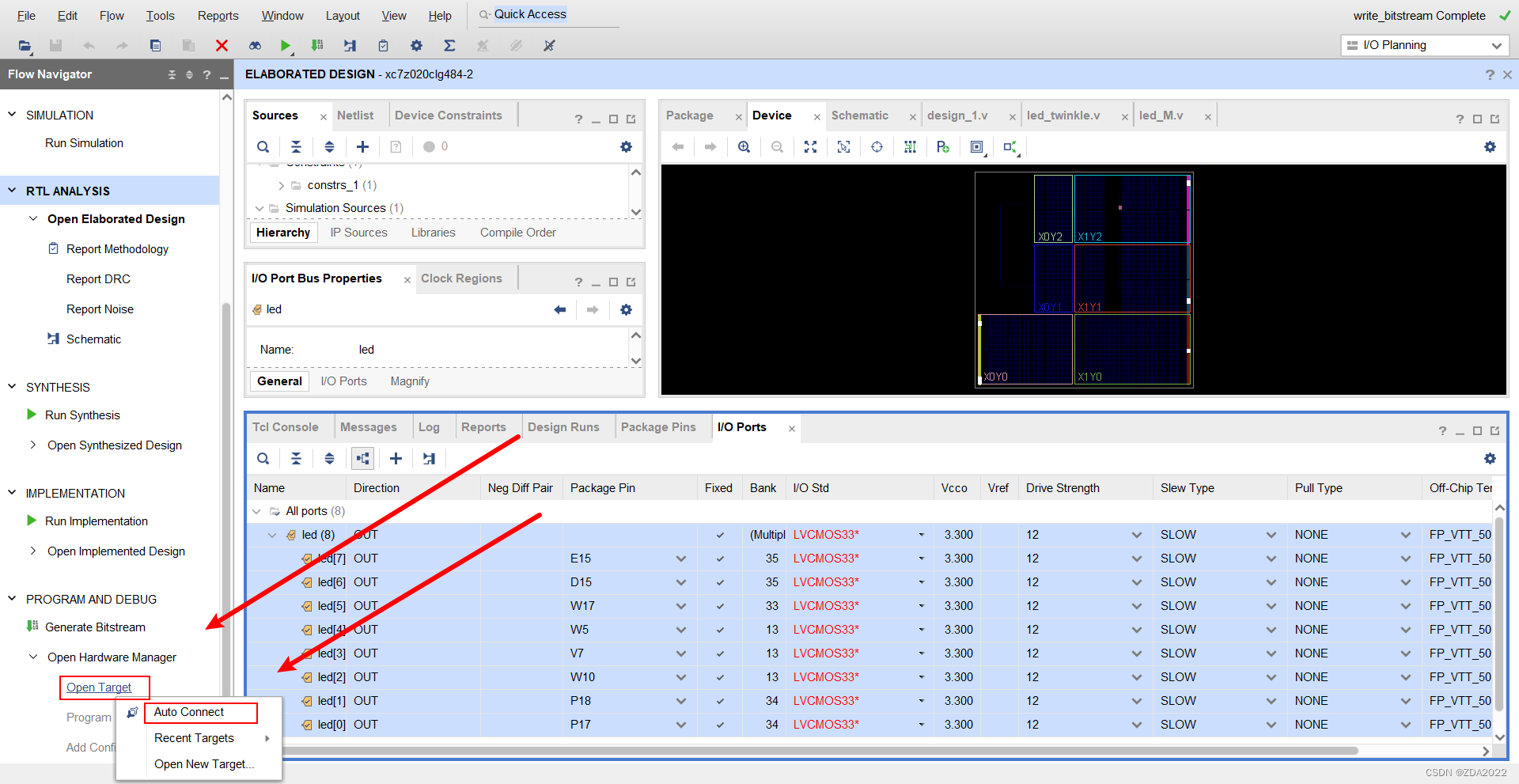

14、打开开发板,并下载bit文件,可以看到流水灯成功

4、gif展示

1514

1514

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?