作者:林良胜

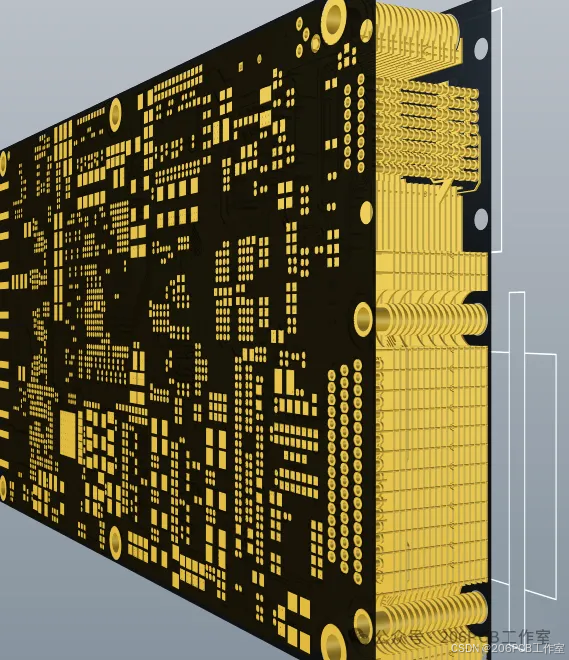

层叠设计概述:

在我们设计PCB过程中,首先影响EMC的设计便是层叠的设计;正常情况下PCB层叠由POWER层(电源)、GND层(地)、信号层组成,POWER层、GND层、信号层的排布顺序以及平面分割,都是影响EMC指标的重要因素。

POWER与GND层:

PCB设计过程中,电源层的数量一般由 电源数量、电源交错程度、电源布线通道大小、电源电流大小、以及发热情况 来决定;在单一电源的设计,一个电源层进行单一电源铺铜即可;若是多个电源的设计(在不交错、电源通道满足的情况下),我们可以进行平面分割进行电源设计(相邻层若有关键信号,设计时不可出现跨分割),若是多个电源的设计(交错复杂、载流散热不达标、单一平面层通道瓶颈等情况下),我们则需要两个或两个以上的电源层进行设计。

POWER层设计需要满足的条件:

(1)单一电源或多种电源设计不交错

(2)关键信号不可出现跨分割现象

(3)满足电源设计需求的载流、散热等问题

GND层设计需要满足的条件:

(1)器件层下面(正数第二及倒数第二层)需要有完整的GND参考平面,例如六层板,即为第二层和第五层需要为GND层。

(2)关键信号(关键的信号层)至少有一面参考GND层,条件允许最好上下参考平面均为GND层。

(3)关键电源至少有一相邻层为GND。

(4)若有多种GND,关键信号不可出现跨分割现象

POWER与GND层的平面阻抗问题:

(1)POWER与GND层均存在自身的特性阻抗,但是POWER层的阻抗会比GND层的高。

(2)为降低POWER层的特性阻抗,需将关键电源、主电源与其GND层(地回流平面)相邻排布,利用POWER与GND层之间的耦合电容特性,降低其POWER层的特性阻抗。

POWER与GND作为参考平面的区别:

POWER与GND层均能作为参考平面(在前面已做过讲解:PCB设计小知识(二)),且都具有一定的屏蔽作用,但相对而言,电源层自身存在较高的特性阻抗,与参考电平存在较大的电位势差:从屏蔽效果的角度考虑,GND层一般均做了接地处理,并作为基准电平参考点,其屏蔽效果是远远优于POWER层,所以在选择参考层的时候,优先选择GND层。

信号层:

PCB设计过程中,信号层的数量一般由 单板器件密度、布线空间、特殊处理的信号布线数量、工作频率、传输速率、性能与指标、以及成本 来决定;信号层的数量主要取决于功能的实现,从EMC角度考虑,需要关注关键信号(强辐射信号;易受干扰的弱、小信号)的屏蔽或隔离措施。

层叠排布原则:

在确认好我们所需要的POWER层、GND层、信号层后,他们之间的排布是每一个PCB工程师需要面对的问题,正如上所述:它们之间的排布顺序以及平面分割,都是影响EMC指标的重要因素。所以层叠的排布顺序有以下原则:

(1)器件层下面(正数第二及倒数第二层)需要有完整的GND参考平面,其目的是给器件提供屏蔽层,以及给器件层的布线提供更好的参考平面。

(2)所有信号尽可能与GND层相邻,关键电源至少有一相邻层为GND。

(3)关键电源至少有一相邻层为GND,减短回流路径,且降低POWER层特性阻抗。

(4)兼顾层压结构对称

层叠排布模板:

在实际层叠排布设计时,要对以上原则灵活掌握,根据实际情况进行排布(折中选择),以下列出层叠排布模板,供大家参考:

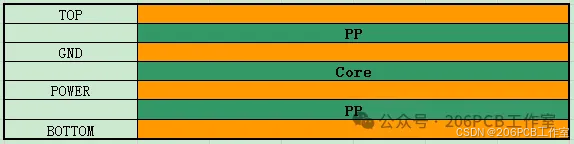

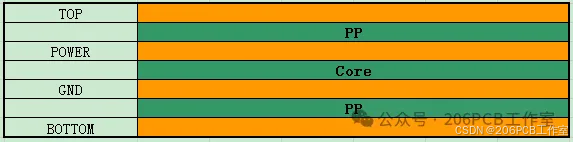

4层板:

优选方案1,可选方案3(注:S为信号层;G为GND层;P为POWER层)

方案1:

此为4层板常规主流层叠设计方案,TOP层(顶层器件层)参考层为GND,关键信号优先走TOP层,但对于层厚有以下建议:

(1)满足关键信号的阻抗控制

(2)板芯(板芯位于GND层与POWER层之间)不宜过厚,使其降低电源平面与地平面的分布阻抗,保证电源平面的去耦效果。

方案2:

此方案为了达到屏蔽效果,会引起以下几点缺陷:

(1)GND层距离POWER层过远,导致电源平面阻抗较大

(2)平面层位于器件层,器件焊盘等因素导致平面不完整

(3)由于参考平面不完整导致阻抗不连续

此方案的GND层与POWER层平面不完整,很难达到预期的屏蔽效果,方案2的使用范围有限,但是在个别单板的特殊情况下,方案2却是最佳的层叠设计选择

方案2在某款接口滤波板上使用,案例特点:

(1)整板无电源,只有GND与PGND,二者各占一个平面层

(2)整板布线简易,作为接口滤波板,最需要关注的是布线辐射

(3)贴片器件少,基本为插件器件

分析特点:

(1)整板无电源,就不存在电源平面阻抗问题

(2)由于贴片器件少,可以采取单面布局;表层为参考层,若是表层有少量布线,由于布线简易,相邻的内层可以大面积铺地铜,让器件有参考相对完整的屏蔽层,以及保证了布线的完整参考层。

(3)作为接口滤波板,PCB布线辐射必须关注,若是如上所述在内层布线,且表层均为GND,走线就能得到很好的屏蔽效果,布线的辐射也能得到很好的控制。

方案3:

此方案与方案1类似,适用于关键器件或关键布线在BOTTOM层。

下期预告:

PCB小知识(6): 6-12层的PCB层叠设计

以上内容对您有帮助的话,避免您需要时找不到,记得点赞关注收藏哦~后续将持续更新设计理论与操作小技巧!

同学们的毕业PCB设计遇到难题、或者工程师们PCB设计上遇到难题欢迎大家私信或评论交流哦~

4223

4223

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?