一、问题痛点

我们在使用PMOS控制电路通断的情况下,如果后端容性负载比较大的话,一般采用PMOS缓启动电路进行设计,在PMOS管的栅源极并入合适大小的电容,实现PMOS管的缓慢开通,但是在关断的过程中,PMOS管栅极的充电过程非常的缓慢,如果此时后端依旧有负载情况,很有可能造成PMOS管的损坏。

二、解决方式

在PMOS管的栅源极之间加入快速泄放控制回路,当关断使能给触发后,迅速将PMOS管栅极电压恢复到与源极电压保持一致,实现PMOS管的快速关断。

三、仿真电路的建立

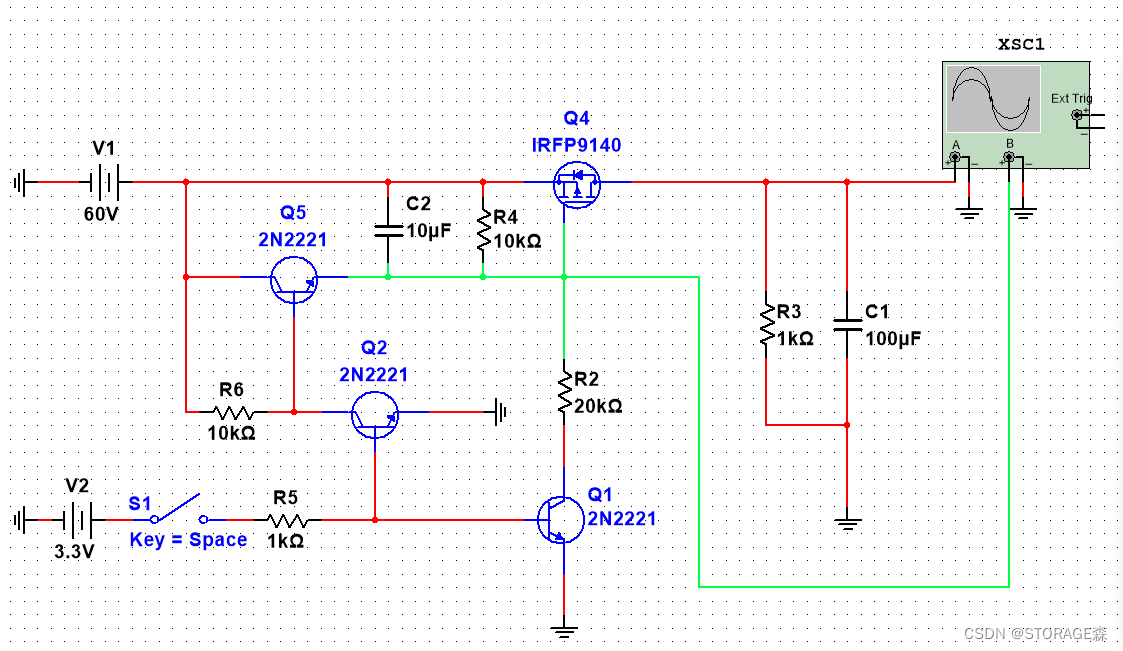

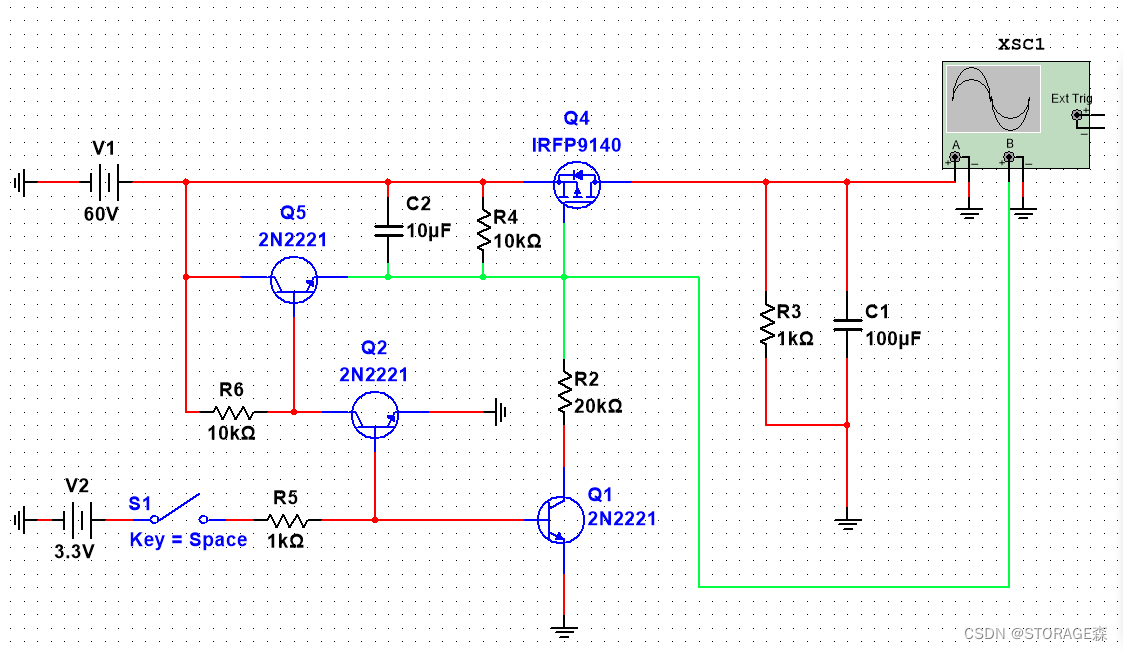

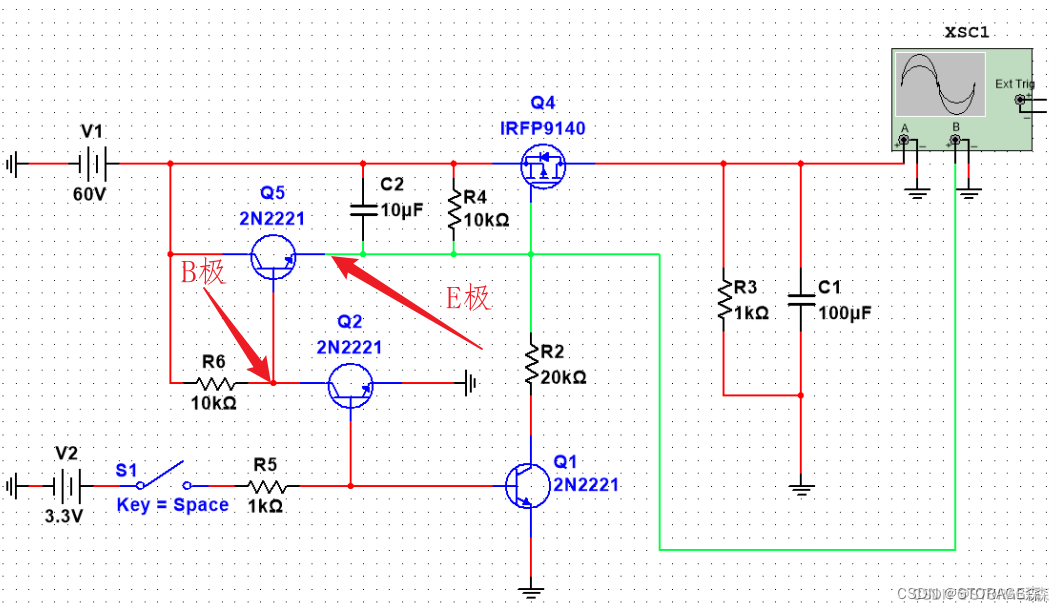

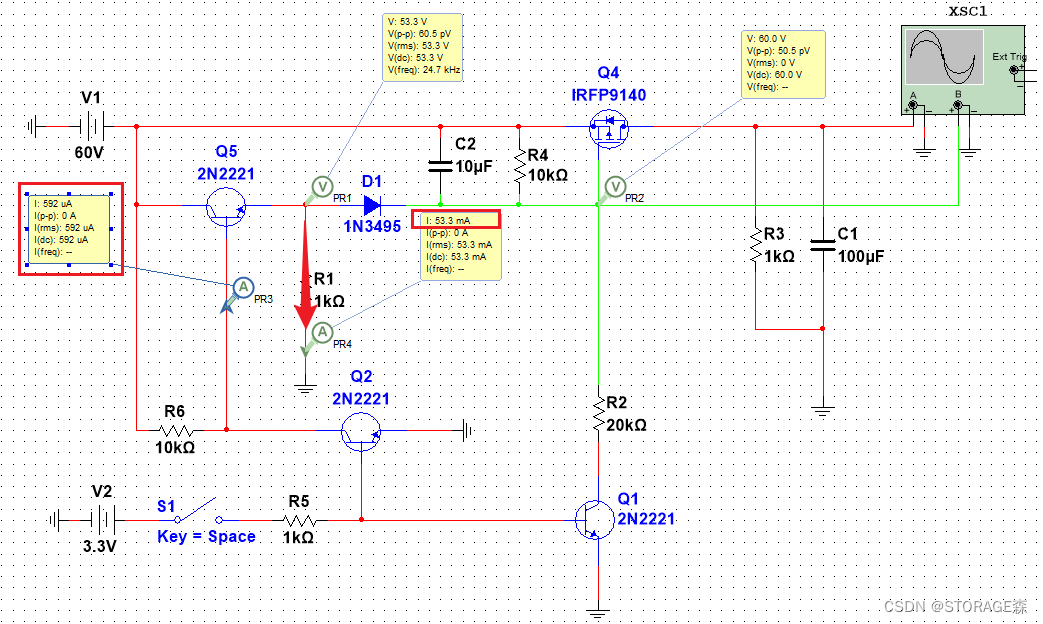

在栅源极之间并入10uF电容,实现PMOS管的缓启动设计,同时使得仿真的波形图更加直观,仿真电路如下图1所示。

图1 PMOS管栅极泄放电路仿真图

四、仿真结果

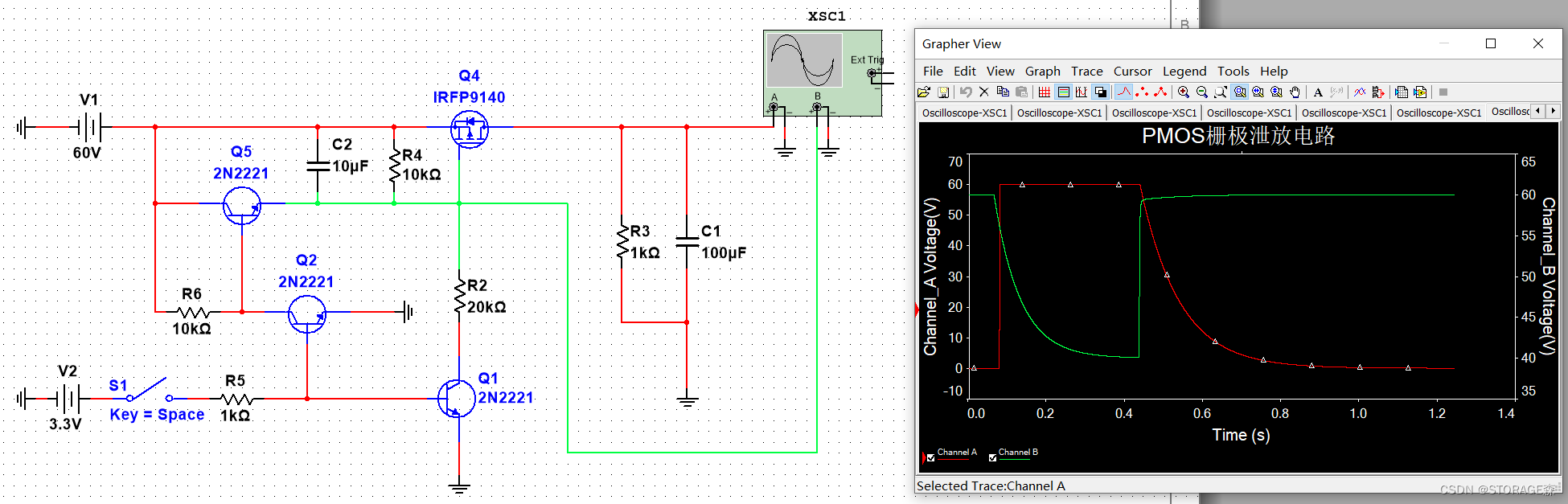

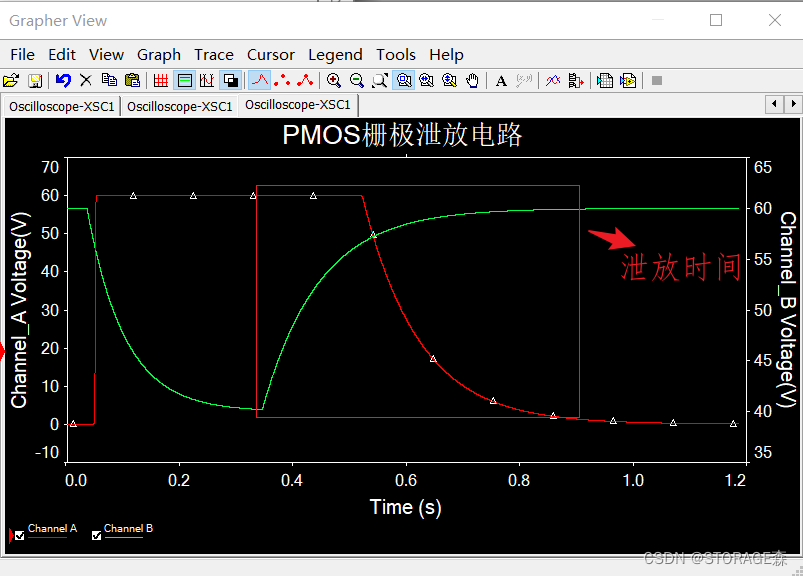

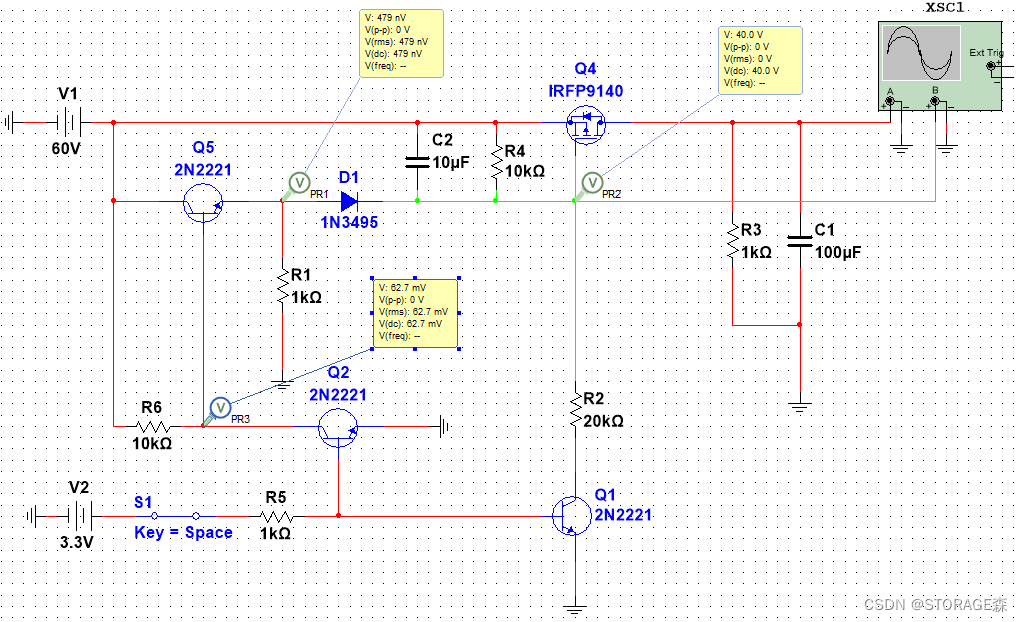

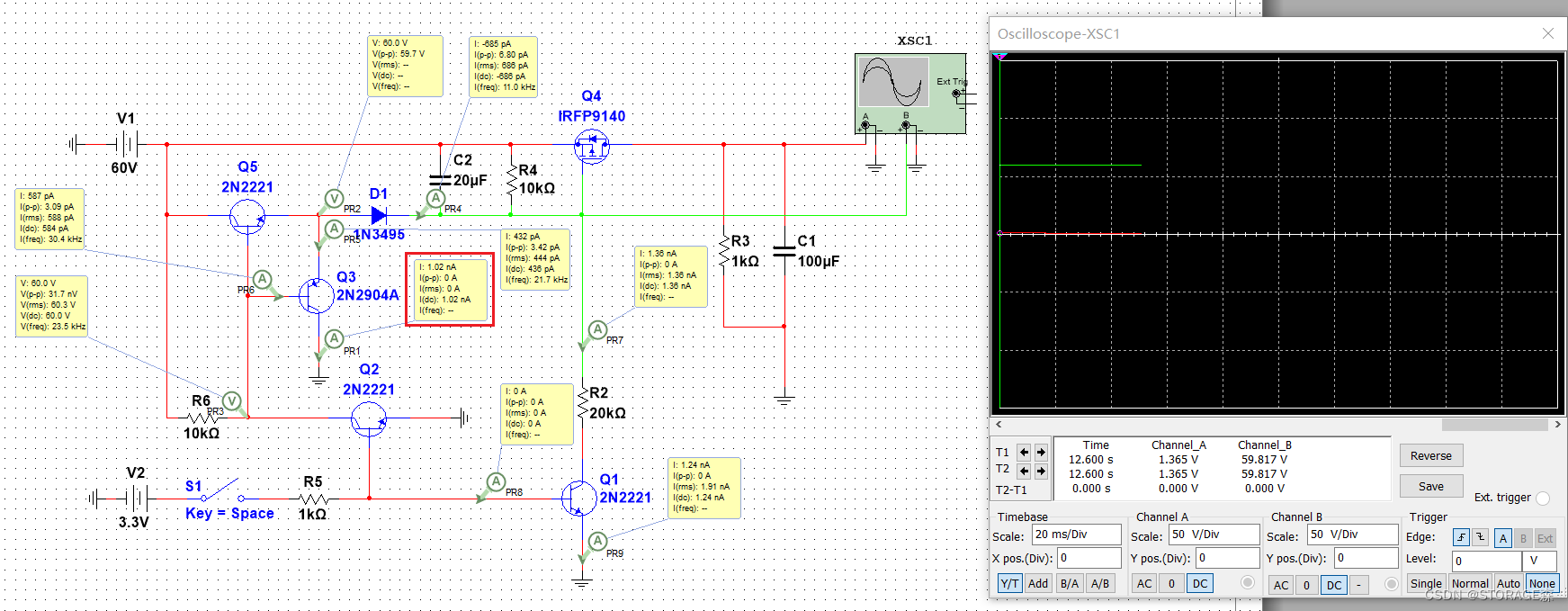

加入栅极泄放电路仿真图如图2所示,栅、漏极电压波形图如3所示。其中绿色波形为PMOS管的栅极电压波形,红色波形为PMOS管的漏极电压波形。

图2 加入栅极泄放电路仿真图

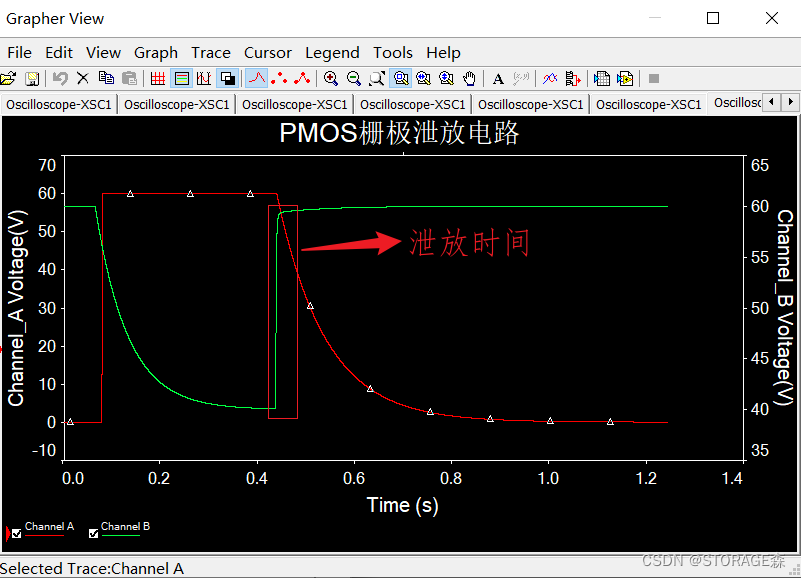

图3 加入栅极泄放电路栅、漏极电压波形图

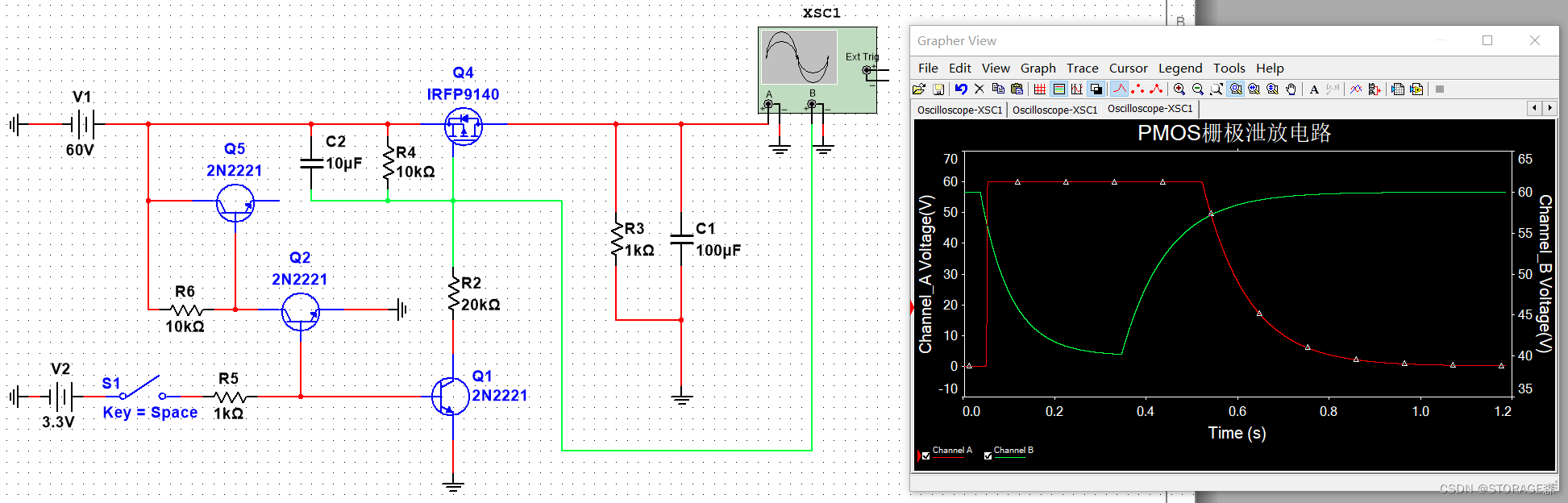

未加入栅极泄放电路(断开Q5三极管发射极与PMOS栅极的连接)仿真图如图4所示,栅、漏极电压波形图如图5所示。其中绿色波形为PMOS管的栅极电压波形,红色波形为PMOS管的漏极电压波形。

图4 未加入栅极泄放电路仿真图

图5 未加入栅极泄放电路栅、漏极电压波形图

五、原理分析

在S1未使能的情况下,三极管Q2、Q1的b极无电流,三极管Q2、Q1不导通,此时PMOS管的栅极电压、三极管Q5的基极、发射极均为60V,PMOS管不到导通;

在S1使能的情况下,三极管Q1、Q2导通,此时Q5的基极为0V,发射极在电阻R4、R2的作用下为40V,此时PMOS为导通状态。当S1断开瞬间,三极管基极在R6的作用下快速充电至60V,此时三极管Q5导通,60V直接通过Q5到达PMOS的栅极,实现PMOS管的栅极快速泄放,实现PMOS管的快速关断。调节电阻R6的大小可以实现快速泄放的速度。

六、结论

从上述仿真结果可以看出,加入栅极泄放回路的栅极电压上升时间远比未加入栅极泄放回路上升时间小的多,由此可得出该栅极泄放电路可以实现PMOS缓启动电路的栅极快速泄放,加快PMOS管的快速关断。

七、实物电路的搭建

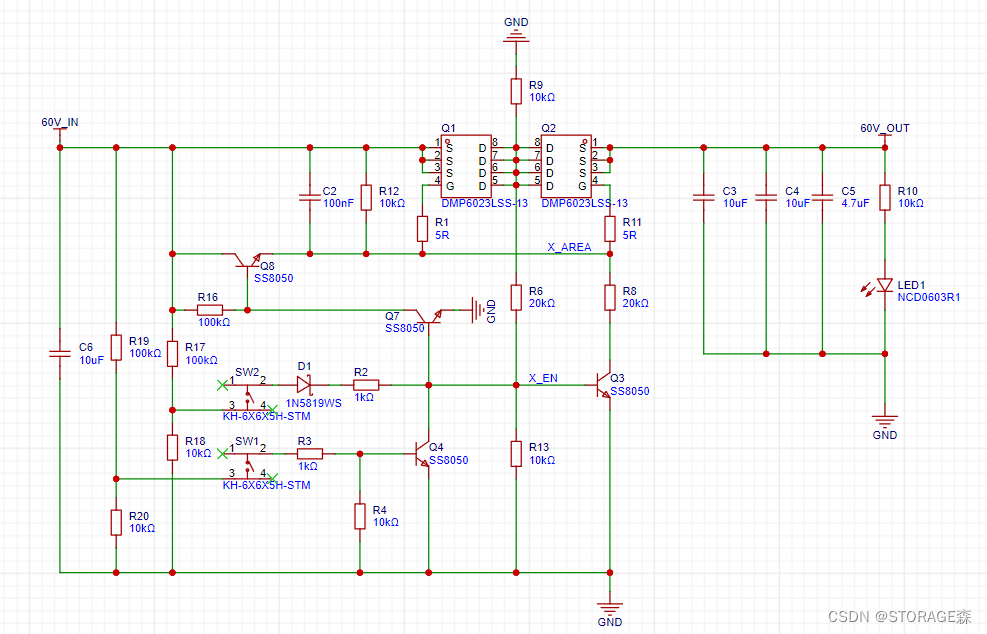

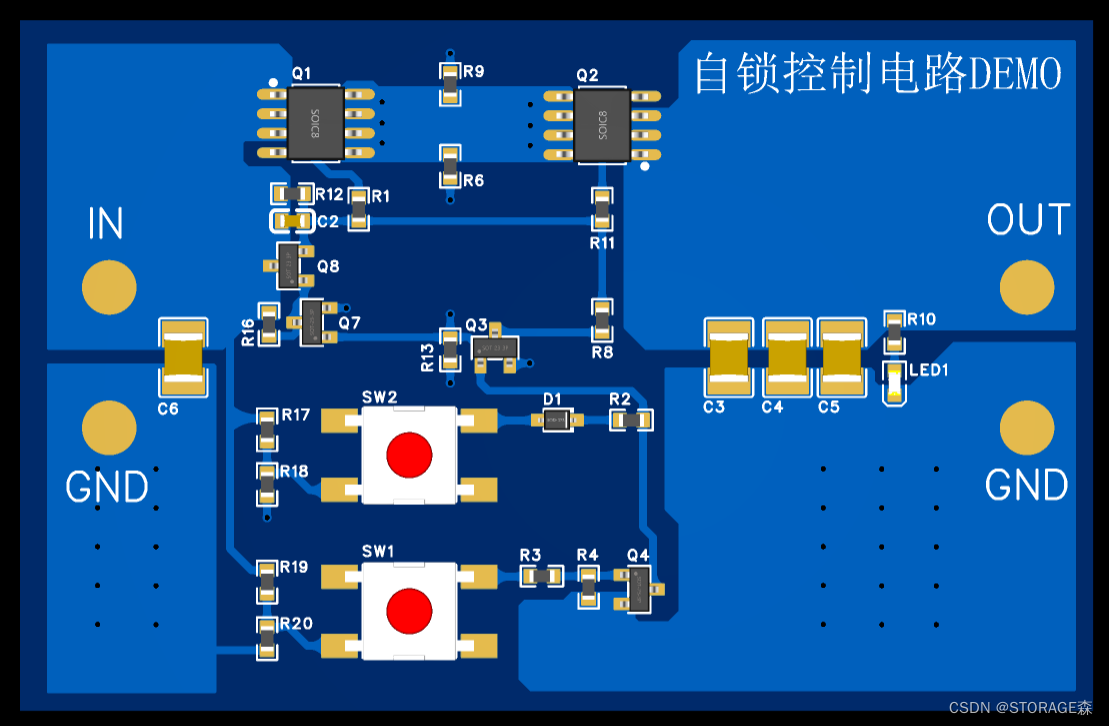

一如既往,白嫖党上线,我们在立创EDA搭建原理图及PCB。立创EDA原理图如图6所示,立创EDA实物渲染图如图7所示。

图6 立创EDA原理图

图7 立创EDA实物渲染图

八、实物验证结果

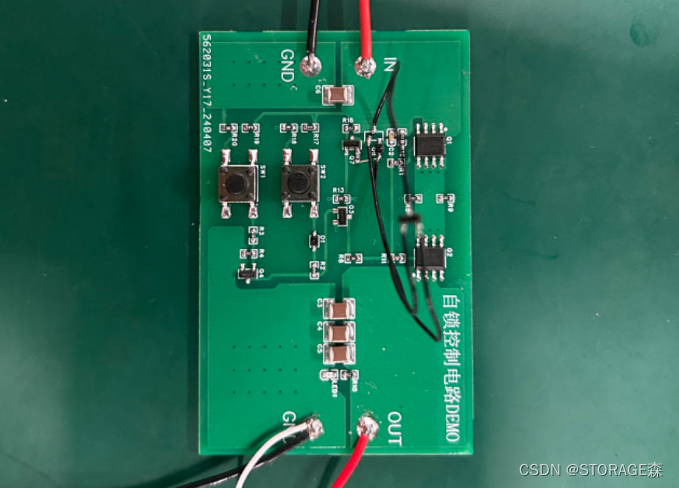

等待许久,终于拿到实物,省去手工焊接的步骤,下面放一张调试过程中的实物图片。

按照上述的原理图在进行调试中,可以证实该电路可以实现PMOS关断过程中的栅极泄放,但是在测试过程中,发现一个问题,即在S1开关闭合后,NPN三极管的E极电压并不是R4、R2分压后的电压,后仔细查证,发现在开启Q4管过程中以及Q4管完全开通后,三极管Q5的E极电压远高于B极电压,造成了NPN三极管EB极之间电压超过器件所能承受的电压,故该电路存在一定的问题。

九、电路改进

为解决上述的NPN三极管的EB极压差超过器件额定电压范围,便设计如下原理图,并通过实物飞线验证(见上图实物图)。

上图原理分析:加入了二极管D1(实物器件选择时反向击穿电压需要大于最大输入电压) 、电阻R1。当S1开关闭合后,三极管Q5的B极在Q2的作用下拉到GND,三极管Q5的E极由于在D1的作用下通过电阻R1下拉到GND,此时三极管Q5的EB极压差在器件的正常范围内,故该原理图电路可正常工作,实际测试数据如下。

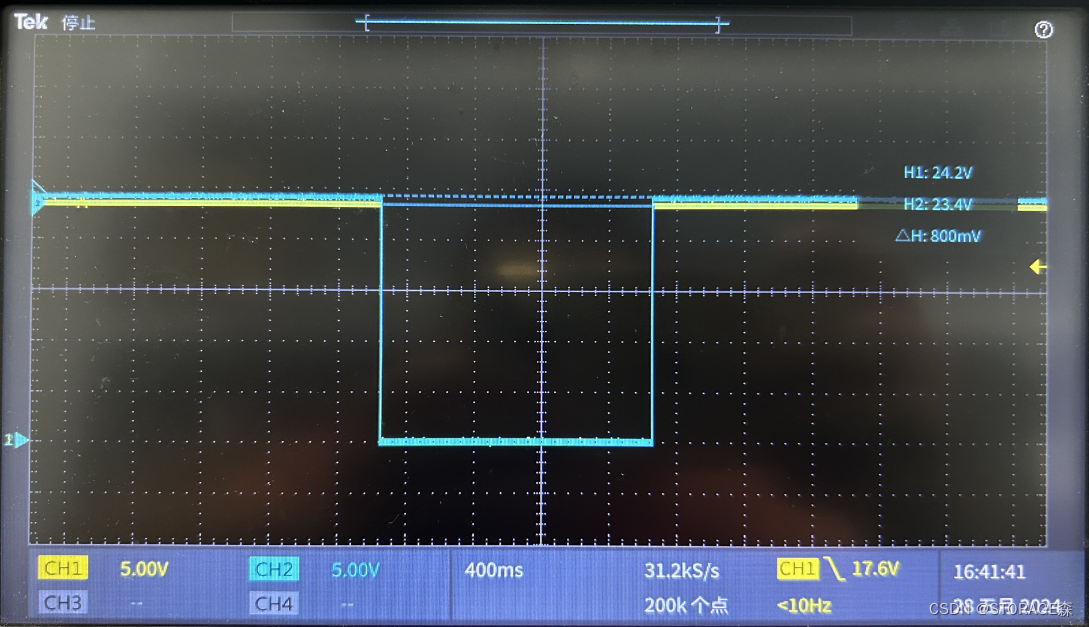

蓝色为Q5三极管B极电压,黄色为Q5三极管E极电压

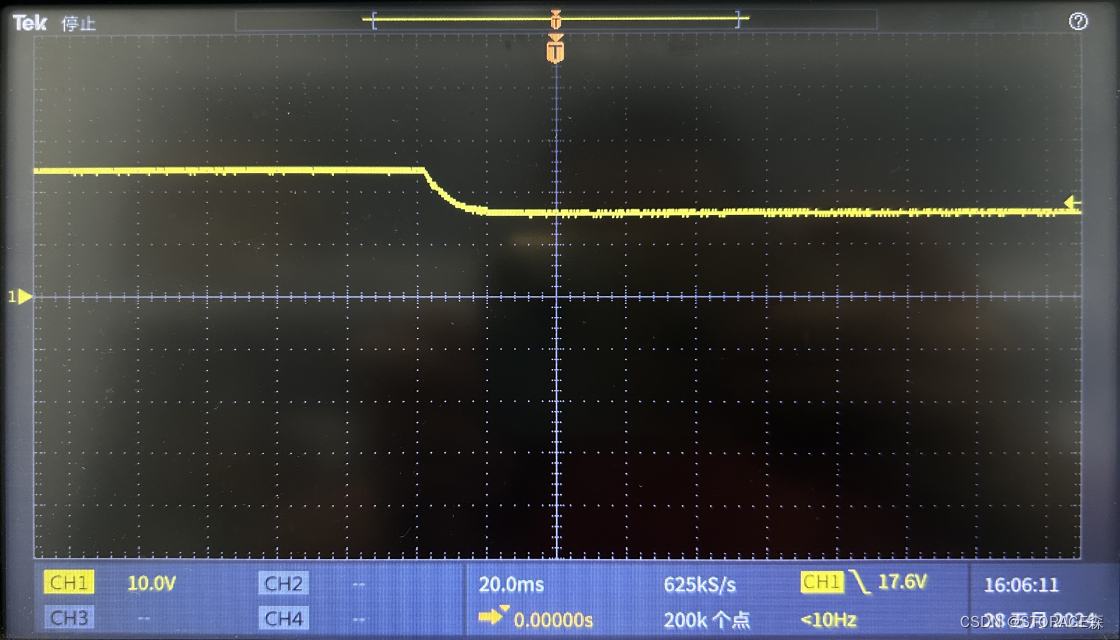

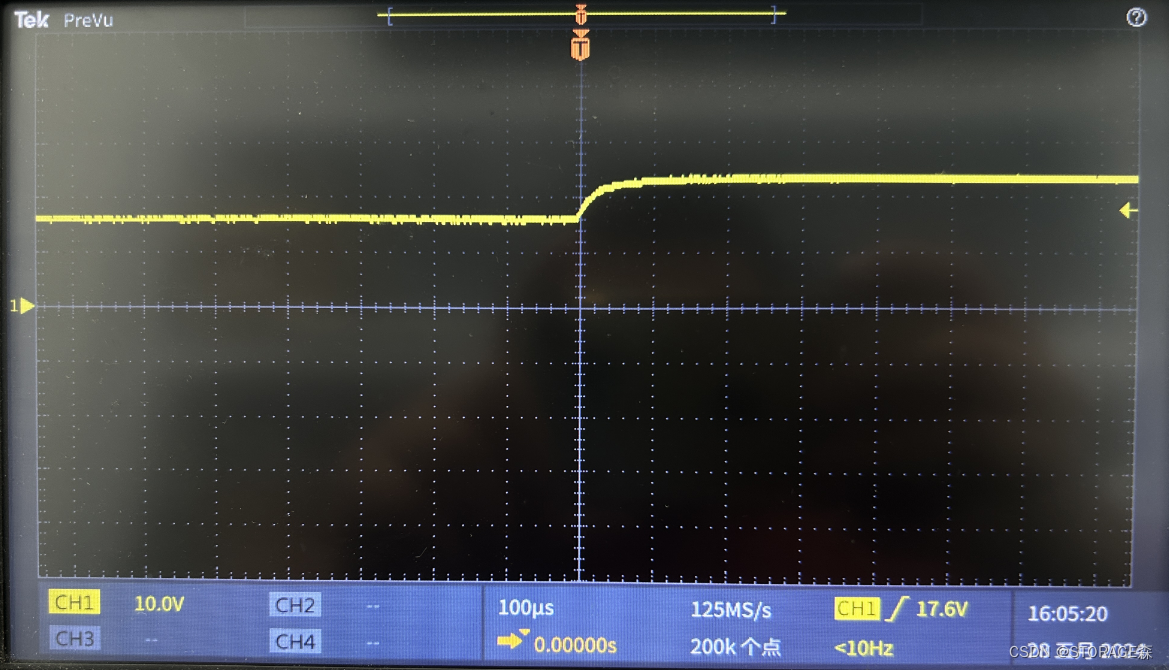

后端空载时,S1开关开通与断开时PMOS管的栅极电压如下图所示。

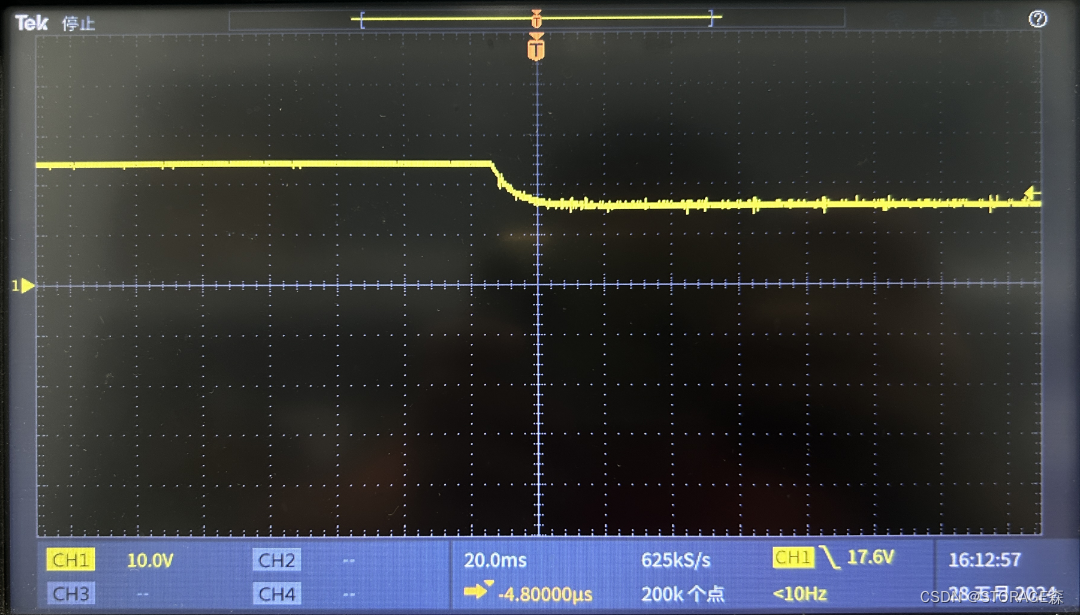

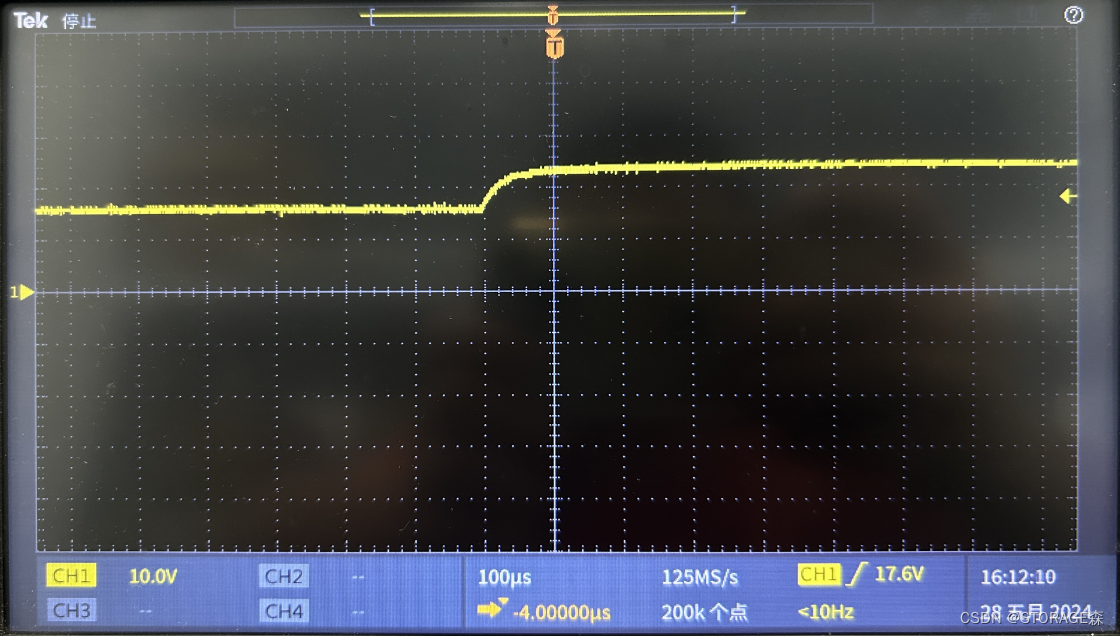

后端带载5A时,S1开关开通与断开时PMOS管的栅极电压如下图所示。

由上图分析可知,无论在后端空载还是带载5A情况下,控制主路通断的PMOS管Q4在使能开关S1开通的时候,PMOS管Q4的栅极放电时间大约为20ms,S1断开的时候,PMOS管Q4的栅极充电时间大约为200us,明显关断的速度远大于缓启动的速度,由此可验证该PMOS管栅极泄放电路应用成立。

十、电路优化

在用PMOS管通断作为锂电池设备的开关的时候,需要考虑到静态功耗的问题。上述电路在使能开关未使能的情况下,会一直产生静态功耗,其主要矛头就是下拉的电阻R1,当电阻R1阻值越小,静态功耗就越大。当S1断开的时候,三极管Q5的B极一直有电流存在,此时E极一直会有电流通过R1流入GND。当然可以通过变大R1的阻值来减小静态功耗,但不是最优解决方案。

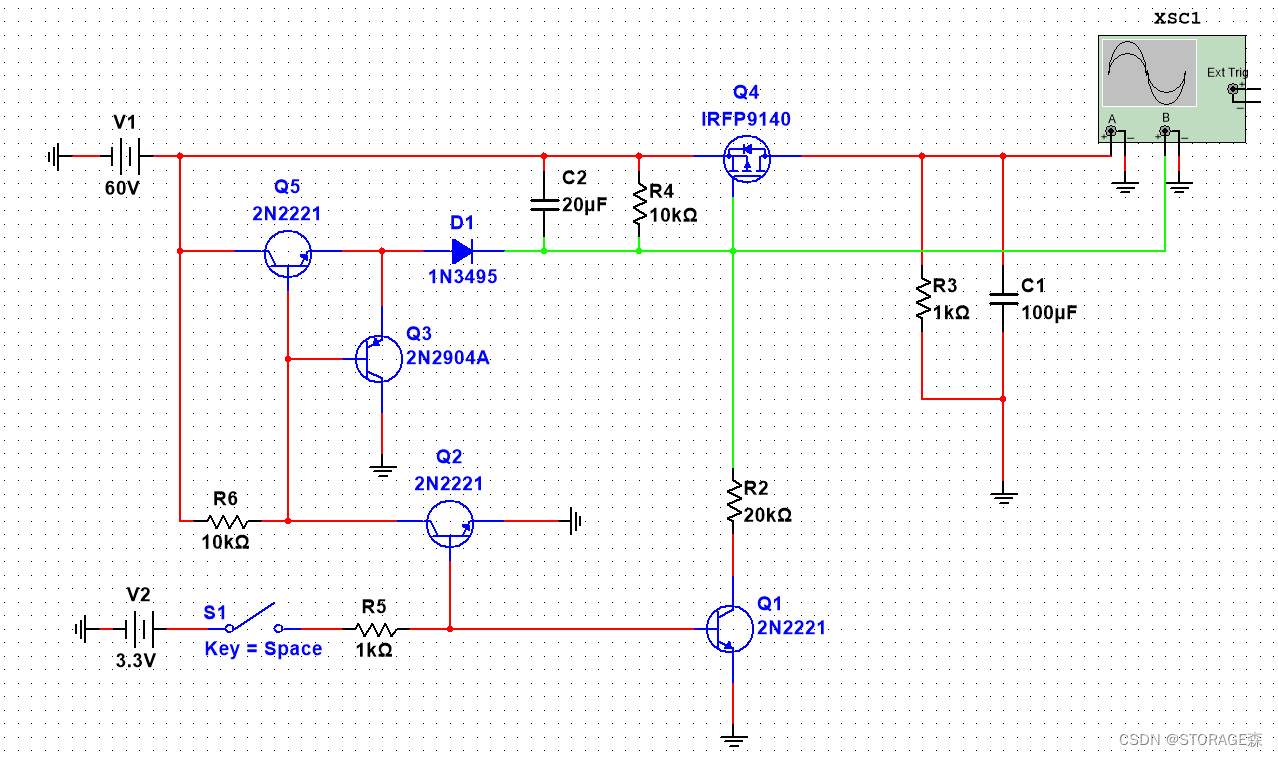

最终,解决方案如下图所示。

原理分析:当使能开关S1断开时, Q2截止,此时R6右侧电势为60V,而此时Q5的E极电势为60V,也即三极管Q3的E极为60V,三极管Q3的BE无电势存在,也即三极管Q3截止,也即当使能开关未开通时,无静态电流经过Q3流向GND,此时PMOS管作为锂电池后端控制开关静态损耗达到最低值。

十一、最终方案图

本文介绍了在处理大容性负载时,PMOS管在关断过程中可能面临的挑战。通过在栅源极间加入快速泄放控制回路,实现PMOS的快速关断,通过仿真和实物验证展示了该方法的有效性。作者使用立创EDA进行了电路设计和模拟验证。

本文介绍了在处理大容性负载时,PMOS管在关断过程中可能面临的挑战。通过在栅源极间加入快速泄放控制回路,实现PMOS的快速关断,通过仿真和实物验证展示了该方法的有效性。作者使用立创EDA进行了电路设计和模拟验证。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?