讲一讲Xilinx家的MIPI方案。这里以普通7系列作为讨论的对象, X家高端的KU+/MPSOC+有已经可以直接支持MIPI接口的IO了。

由于MIPI信号的比较特别,在设计之初应该充分考虑了低功耗,所以MIPI原生的信号电平支持HS和LP模式,工作于不同的电平标准:

从图中可以 清楚的看到,MIPI电气信号存在同时存在2个电平模式,如果接到FPGA的引脚上,很明显FPGA是无法支持的。

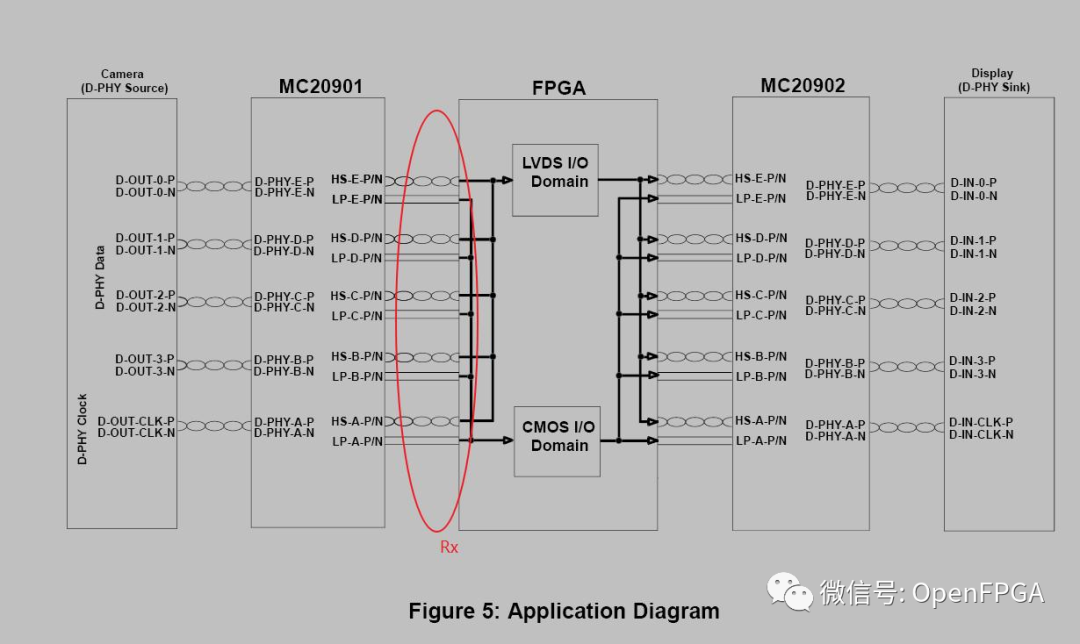

同时,HS模式的电平标准FPGA也是不支持的。所以,Xilinx家给出了2种方案,实现MIPI信号电平的转换,这个在文档XAPP894中有详细的介绍,下面只给出MIPI DPHY Rx部分

1电阻网络

在MIPI线速率较高的情况下,不建议使用该方式。

2外部芯片 MC20901

在用于接收摄像头时,只需要用到MC20901即可

关于MIPI的调试

MIPI的调试前提是你正确的完成了sensor的配置,建议从网上或者FAE那里获取一组已经验证过的配置来驱动sensor。这样接下来调试的重心就可以放到MIPI部分。(补充说一句,高中生物我印象最深的一个概念就是:做实验要进行变量控制,满足单一变量的重复对比试验才能说明问提。然而工作中,很多时候出了问提定位都是胡乱猜)

由于使用的四Xilinx的MIPI RX Subsystem IP解决方案,所以用户能配置的部分其实并不多。但是这个Subsystem内部其实是2个IP构成,一个是MIPI-DPHY,另外一个是MIPI-CSI2接口,然后两个IP之间采用PPI接口互联。

MIPI DPHY通过接收比特流数据,然后根据帧格式,恢复出packet。协议中对packet进行了ECC校验,具备一定的识别和纠正错误的能力。但是如果信号质量不好,出现的错误较多,则会出现不可恢复的错误,在图像上显示的就是时许不对导致的飞线,甚至花屏。

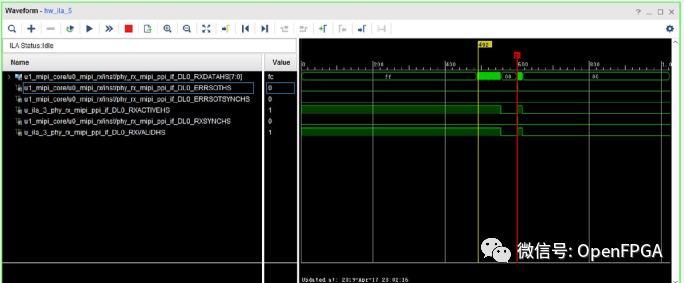

在综合完成以后,打开综合后的原理图,进入MIPI DPHY部分,对物理层后缀为err的信号进行mark_debug,然后保存到xdc文件中用于后期的调试

从图中可以看到xilinx 的MIPI IP PPI接口中 errorths信号拉高,说明存在行丢失的情况,出现该情况,如果物理层错误信号不断,再检查完FPGA工程本身没问题,则可以从硬件方面考虑是否存在问题。

本文转自博客园:

https://blog.csdn.net/wuyanbei24/article/details/104603426/

本文内容仅代表作者观点,不代表平台观点。

如有任何异议,欢迎联系我们。

- END -

NOW现在行动!

推荐阅读

【Vivado那些事】如何查找官网例程及如何使用官网例程【Vivado使用误区与进阶】总结篇【Vivado那些事】Vivado中常用的快捷键(二)其他常用快捷键SystemVerilog数字系统设计_夏宇闻 PDFVerilog 里面,always,assign和always@(*)区别图书推荐|ARM Cortex-M0 全可编程SoC原理及实现

简谈:如何学习FPGAVitis尝鲜(一)拆解1968年的美国军用电脑,真的怀疑是“穿越”啊!

一文最全科普FPGA技术知识你见过1-bit CPU吗?高级FPGA设计技巧!多时钟域和异步信号处理解决方案

【Vivado那些事】Vivado中电路结构的网表描述现代计算机的雏形-微型计算机MCS-4

世界上第一个微处理器真的是Intel 4004吗?其实这是个很复杂的故事…

【每周一问】如何控制加载FPGA程序时,Xilinx FPGA的IO管脚输出高低电平

【Vivado那些事】vivado生成.bit文件时报错-ERROR: [Drc 23-20]

AD9361 和Zynq及其参考设计说明1202年了,还在使用虚拟机吗?Win10安装Ubuntu子系统及图形化界面详细教程谈谈Xilinx FPGA设计的实现过程

Github 上有哪些优秀的 VHDL/Verilog/FPGA 项目

AD936x+ZYNQ搭建收音机(一)

AD936x+ZYNQ搭建收音机(二)含视频演示

AD936x+ZYNQ搭建收音机(三)-终篇

AD936x+ZYNQ搭建OpenWIFI

Verilog 版本:Verilog-95、Verilog-2001与System Verilog区别简谈

FPGA时钟设计方案无招胜有招-Vivado非工程模式下的详细设计

追寻ARM的起源-Acorn电脑简史及FPGA实现

面试中经常会遇到的FPGA基本概念,你会几个?

点击上方字体即可跳转阅读

4694

4694

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?