赛灵思近日宣布推出 Vivado® ML 版,这是业内首个基于机器学习(ML )优化算法以及先进的面向团队协作的设计流程打造的 FPGA EDA 工具套件,可以显著节省设计时间与成本,与目前的 Vivado HLx 版本相比,Vivado ML 版将复杂设计的编译时间缩短了 5 倍,同时还提供了突破性的平均达 10% 的结果质量( QoR )提升。

Vivado® ML 概述

1

基于 ML 的设计优化

加速设计收敛

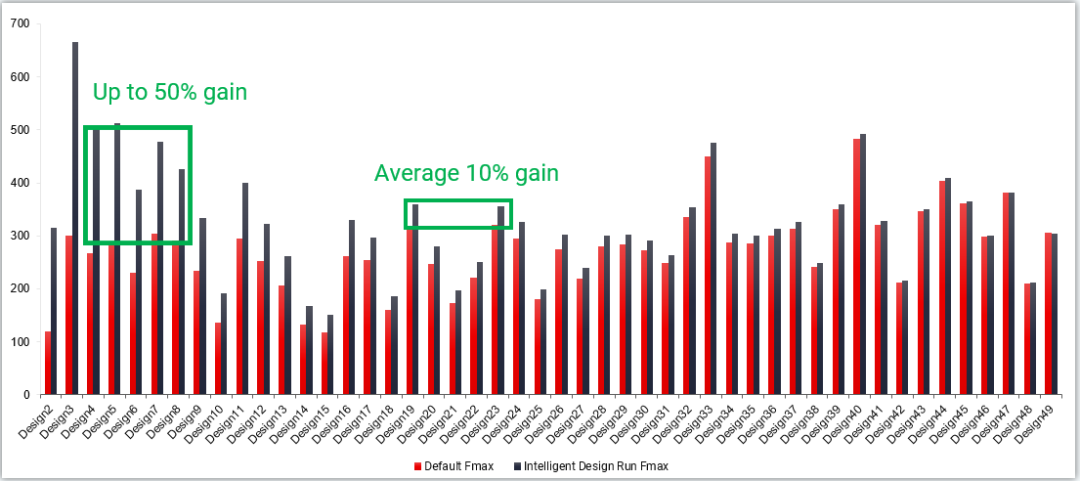

与当前的 Vivado HLx 版本相比,全新w Vivado® ML 版本在复杂设计上实现了高达 50%(平均 10%)的突破性结果质量 (QoR) 提升。

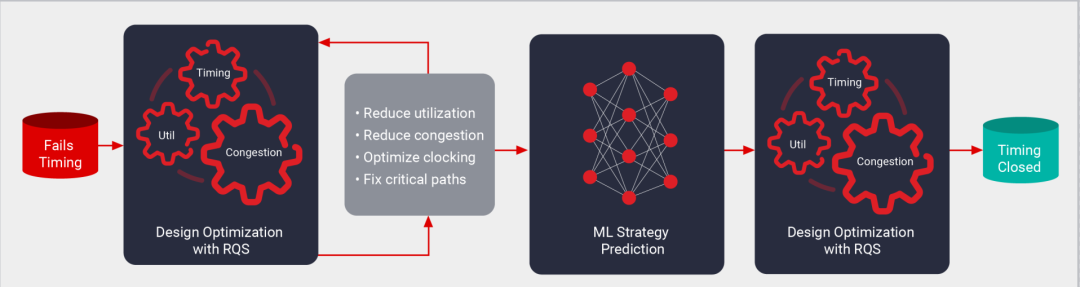

基于 ML 的逻辑优化、拥塞估计、延迟估计和智能设计运行等新功能和算法有助于自动化策略以减少时序收敛迭代。

2

协同设计环境

提升生产力

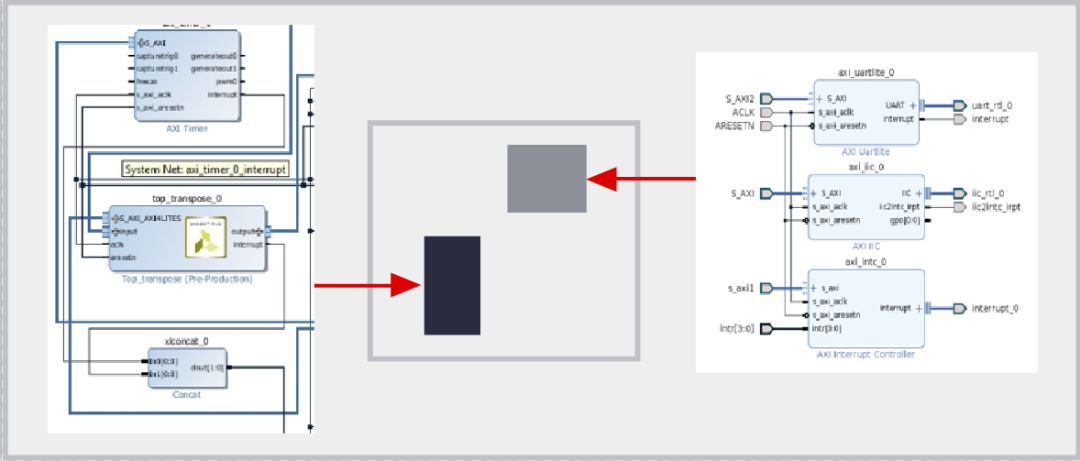

使用 Vivado IP Integrator 改进协作设计,使用全新的“块设计容器”功能实现模块化设计。

推广基于团队的设计方法,并允许采用分而治之的策略来处理具有多站点协作的大型设计。

3

全新高级 DFX 功能

编译时间减少

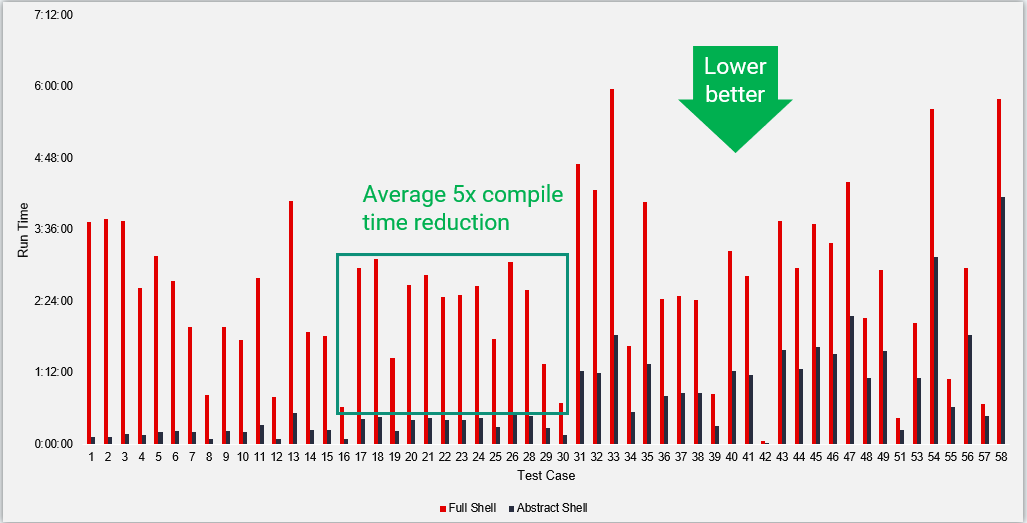

Xilinx 引入了抽象 Shell 的概念,允许用户在系统中定义多个模块以进行增量和并行编译。

与传统的完整系统编译相比,此功能可将平均编译时间缩短 5 倍,最多可缩短 17 倍。

Abstract Shell 通过将设计细节隐藏在模块之外来帮助保护客户的 IP

功能介绍

1

高层次设计

Vivado IP Integrator 可提供基于 Tcl、设计期正确的图形化设计开发流程。设计团队在接口层面上工作,能快速组装复杂系统,充分利用 Vitis™ HLS、Vitis Model Composer、Xilinx IP、联盟成员 IP 和自己的 IP。通过利用全新提升的 Vivado IPI 和 HLS 的完美组合,客户能将开发成本相对于采用 RTL 方式而言节约高达 15 倍。

2

验证

应对当前复杂器件的验证挑战,需要在各种设计层面上应用大量工具及技术。Vivado® 设计套件在紧密结合的环境中提供这些工具和技术,从而可加速模块及芯片级设计的验证。

3

实现

具有高级机器学习算法的 Vivado ML 设计套件提供了在运行时和性能方面具有显着优势的最佳实现工具。凭借用于综合、布局、布线和物理优化的一流编译工具以及 Xilinx 编译方法建议,设计者可以加快设计周期的实现阶段。

平台版本

Vivado ML 标准版

Vivado ML 的器件受限免费版本。

Vivado ML 企业版

包括对所有 Xilinx 器件的支持。

文章转自: XILINX开发者社区

版权归Xilinx官方所有

- END -

NOW现在行动!

推荐阅读

【Vivado那些事】如何查找官网例程及如何使用官网例程【Vivado使用误区与进阶】总结篇【Vivado那些事】Vivado中常用的快捷键(二)其他常用快捷键SystemVerilog数字系统设计_夏宇闻 PDFVerilog 里面,always,assign和always@(*)区别图书推荐|ARM Cortex-M0 全可编程SoC原理及实现

简谈:如何学习FPGAVitis尝鲜(一)拆解1968年的美国军用电脑,真的怀疑是“穿越”啊!

一文最全科普FPGA技术知识你见过1-bit CPU吗?高级FPGA设计技巧!多时钟域和异步信号处理解决方案

【Vivado那些事】Vivado中电路结构的网表描述现代计算机的雏形-微型计算机MCS-4

世界上第一个微处理器真的是Intel 4004吗?其实这是个很复杂的故事…

【每周一问】如何控制加载FPGA程序时,Xilinx FPGA的IO管脚输出高低电平

【Vivado那些事】vivado生成.bit文件时报错-ERROR: [Drc 23-20]

AD9361 和Zynq及其参考设计说明1202年了,还在使用虚拟机吗?Win10安装Ubuntu子系统及图形化界面详细教程谈谈Xilinx FPGA设计的实现过程

Github 上有哪些优秀的 VHDL/Verilog/FPGA 项目

AD936x+ZYNQ搭建收音机(一)

AD936x+ZYNQ搭建收音机(二)含视频演示

AD936x+ZYNQ搭建收音机(三)-终篇

AD936x+ZYNQ搭建OpenWIFI

Verilog 版本:Verilog-95、Verilog-2001与System Verilog区别简谈

FPGA时钟设计方案无招胜有招-Vivado非工程模式下的详细设计

追寻ARM的起源-Acorn电脑简史及FPGA实现

面试中经常会遇到的FPGA基本概念,你会几个?

Xilinx FPGA MIPI 接口简单说明

介绍一些新手入门FPGA的优秀网站

Vivado ML(机器学习) 2021尝鲜

点击上方字体即可跳转阅读

5928

5928

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?