自从召集2020届校招同行加入新建立的“IC/FPGA校招笔试面试交流群“,见识到了很多关于建立时间和保持时间分析的题目,在为别人解答疑惑,以及别人为自己解答疑惑的同时,自己对于知识的理解更加深刻了。

对于建立时间而言,从单独的对触发器的建立时间和保持时间的分析到了对电路(系统)的建立时间到保持时间的分析,前者是核心,后者是扩展,后者建立在前者的基础之上进行推到得到,同时也是芯片内部实际遵循的时序规则。

注:下面博文中的蓝色字体均为链接!

以下图片均来自互联网以及群内讨论。

对于触发器的建立时间和保持时间,可见之前的博文:

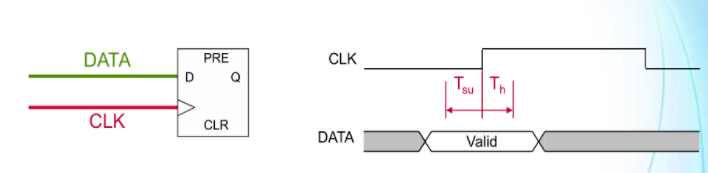

从这篇博文上,我们可以知道建立时间和保持时间的概念,建立时间就是时钟有效沿到来之前数据必须保持稳定的时间,而保持时间就是时钟有效沿到来之后数据必须保持稳定的时间,如果不满足建立时间或保持时间,就会导致时序违规,这对电路的功能实现是有很大影响的。

我们还可以了解到Tco这个时序参数,它的名字是数据输出延时,它是对于触发器而言的,含义是从触发器的时钟有效开始,数据从输入到输出之间的延迟。(触发器的数据输入到输出是有一段时间的,所以有这

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3701

3701

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?