目录

MATLAB操作

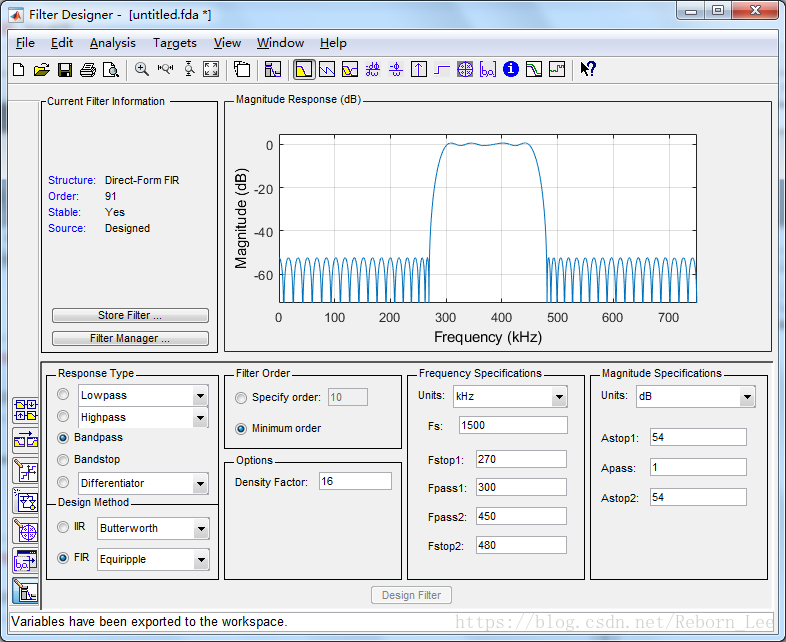

在matlab中命令窗口中输入:filterDesigner,设计如下参数的带通滤波器;

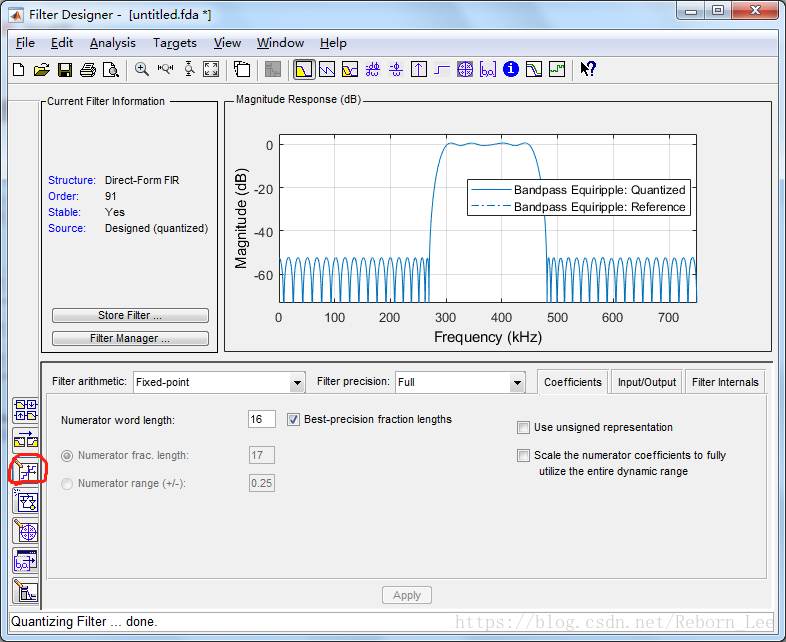

在左侧第三个功能设置:Set quantization parameters,选择Filter arithmetic为Fixed-point,由于只是测试,参数保持默认即可。

在菜单栏中选择targets,展开选择生成Xilinx的coe文件:(自己选择路径,命名)

Vivado操作

需要设计的FIR的系数文件搞定了,下面进入Vivado进行IP核设计:

简单的创建一个Vivado工程,这些都无关紧要,随便创建一个工程,然后按照下图的方式创建一个IP核:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

62

62

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?