TI的DSP芯片,GPIO的内部上拉在默认情况下是使能的(能够配置为PWM输出的GPIO除外,这类GPIO默认情况下内部上拉被禁用)。对于在默认情况下内部上拉被使能的GPIO来说,有些情况下,需要对其寄存器进行配置来禁用内部上拉。

如果GPIO配置为输出,内部上拉是否被使能,影响不大,因为主要取决于输出的是高电平还是低电平。

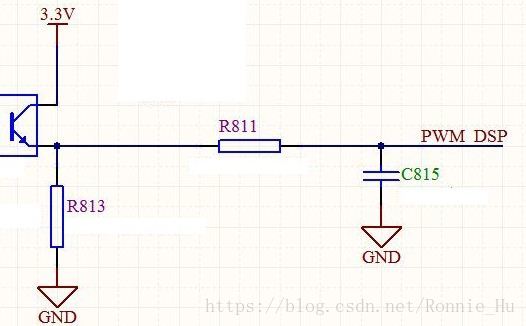

如果GPIO配置为输入,就要注意了,是否需要禁用内部上拉,取决于外部硬件电路的设计,比如,下图中的这种情况就应该禁用内部上拉,PWM_DSP输出到DSP芯片,如果使能了内部上拉,当光耦输出为开路时,由于R813、R811与DSP内部上拉电阻形成分压,PWM_DSP的电平就不为0了。

本文详细介绍了TI的DSP芯片中GPIO的内部上拉特性,默认情况下,除配置为PWM输出外,GPIO的内部上拉是使能的。文章探讨了在不同配置下内部上拉的影响,特别是当GPIO配置为输入时,如何根据外部电路设计决定是否禁用内部上拉,以避免电路分压导致的信号干扰。

本文详细介绍了TI的DSP芯片中GPIO的内部上拉特性,默认情况下,除配置为PWM输出外,GPIO的内部上拉是使能的。文章探讨了在不同配置下内部上拉的影响,特别是当GPIO配置为输入时,如何根据外部电路设计决定是否禁用内部上拉,以避免电路分压导致的信号干扰。

1004

1004

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?