verilog边缘检测电路分析

一、前言 按位与,按位或,按位异或

首先清楚几个概念

- 按位与&:都为1,则为1,否则为0

- 按位或|:只要有一个为1则为1,否则为0

- 按位异或^:不同则为1,否则为0

c=a&b

| a | b | c |

|---|---|---|

| 1 | 0 | 0 |

| 0 | 1 | 0 |

| 0 | 0 | 0 |

| 1 | 1 | 1 |

c=a|b

| a | b | c |

|---|---|---|

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 0 | 0 | 0 |

| 1 | 1 | 1 |

c=a^b

| a | b | c |

|---|---|---|

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 0 | 0 | 0 |

| 1 | 1 | 0 |

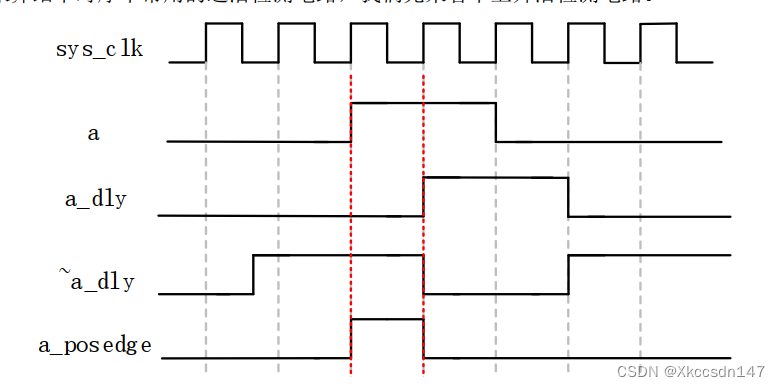

二、上升沿检测

把a 信号寄存一拍,得到 a_dly 信号。 我们再用 a 信号和 a_dly 取反再相与

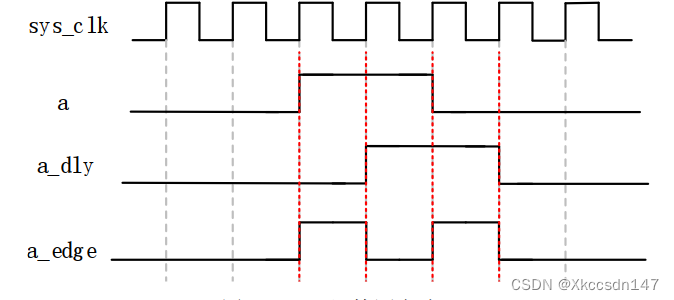

三、下降沿检测

利用时序逻辑,把 a 信号寄存一拍,得到 a_dly 信号,我们再把 a 信号取反,用 a 取反的信号和 a_dly 相与

四、双沿检测

我们可以发现寄存一拍后与原波形对比,有且仅有两处存在 一高一低/一低一高 的情况,其他地方都是要么全为高,要么全全为低,把延迟后的波形取反,又正好反过来了,有且仅有两处存在 同高/同低 的情况,正好使用异或条件把他们摘出来。

verilog代码实现

module edge_test

(

input wire clk ,

input wire rst_n ,

input wire a ,

output wire a_edge ,

output wire a_edge2 ,

output wire a_negedge ,

output wire a_posedge ,

output wire a_flip ,

output wire a_dly_flip

);

reg a_dly ;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

a_dly <= 0;

end

else begin

a_dly <= a;

end

end

assign a_negedge = a & ~a_dly ;

assign a_posedge = ~a & a_dly ;

assign a_edge = a_posedge ^ a_negedge ;

assign a_edge2 = a ^ a_dly ;

assign a_flip = ~a ;

assign a_dly_flip= ~a_dly ;

endmodule

testbench代码

`timescale 1ns/1ns

module tb_edge_test();

reg sys_clk ;

reg sys_rst_n ;

reg a ;

wire a_edge ;

wire a_negedge ;

wire a_posedge ;

wire a_edge2 ;

wire a_flip ;

wire a_dly_flip ;

initial begin

sys_clk = 1'b1;

sys_rst_n <= 1'b0;

a <= 1'b0;

#201

sys_rst_n <= 1'b1;

#20

a <= 1'b1;

#100

a <= 1'b0;

end

always #10 sys_clk <= ~sys_clk;

edge_test edge_test_inst(

.clk (sys_clk ),

.rst_n (sys_rst_n ),

.a (a ),

.a_posedge (a_posedge ),

.a_negedge (a_negedge ),

.a_edge (a_edge ),

.a_edge2 (a_edge2 ),

.a_flip (a_flip ),

.a_dly_flip (a_dly_flip )

);

endmodule

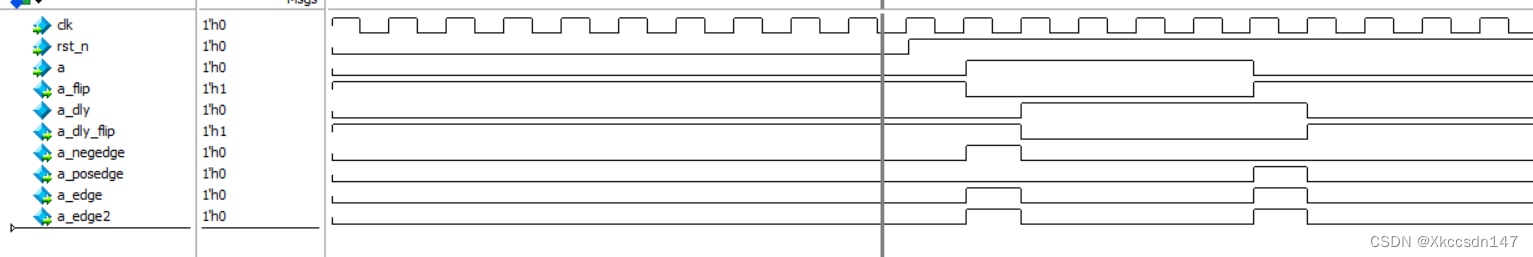

modelsim仿真波形图

765

765

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?