目录

3.特性阻抗(Characteristic Impedance)

术语

概念一览

1.信号完整性(Signal Integrity)

信号完整性是指信号在信号线上的质量。信号具有良好的信号完整性是指当在需要的时候具有所必需达到的电压电平数值。

2.传输线(Transmission Line)

传输线是一个网络(导线),并且它的电流返回到地或电源。

3.特性阻抗(Characteristic Impedance)

组成信号传输回路的两个导体之间存在分布电感和分布电容,当信号沿该导体传输时, 信号的跃变电压(V)和跃变电流(

I

)的比值称为特性阻抗(

Z

0

),即

Z

0

=V/I

。

4.反射(Reflection)

反射就是在传输线上的回波。信号功率(电压和电流)的一部分传输到线上并达到负载处,但是有一部分被反射了。如果源端与负载端具有相同的阻抗,反射就不会发生。

5.串扰(Crosstalk)

串扰是两条信号线之间的耦合。信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。

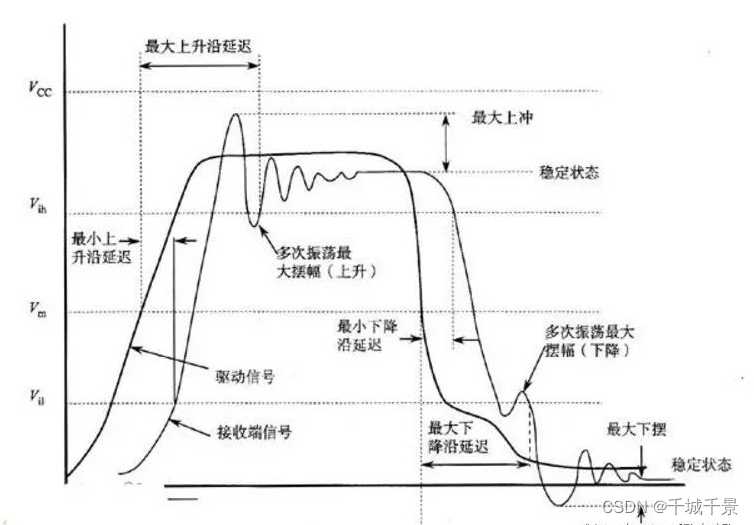

6.过冲(Overshoot)

过冲就是第一个峰值或谷值超过设定电压。对于上升沿是指最高电压,而对于下降沿是指最低电压。过分的过冲能够引起保护二极管工作,导致过早地失效。

7.下冲(Undershoot)

下冲是指下一个谷值或峰值。过分的下冲能够引起假的时钟或数据错误(误操作)。

8.电路延迟

指信号在器件内传输所需的时间(

T

pd

) 。例如,

TTL

的电路延迟在

3 ~ 20nS

范围。

9.边沿时间

器件输出状态从逻辑低电平跃变到高电平所需要的时间(信号波形的 10~90%

),通常表示为上升沿(T

r

)。器件输出状态从逻辑高电平下降到低电平所需要的时间(信号波形的 90~10%

),通常表示为下降沿(

T

f

)。

10.占空比偏斜

信号传输过程中,从低电平到高电平的转换时间与从高电平到低电平的转换时间之间的差别,称为占空比偏斜。TTL和

CMOS

信号的占空比偏斜问题较为突出,主要是因为其输出的上升沿和下降沿延迟不同。

11.输出到输出偏斜

同一器件不同输出引脚之间的信号延迟差别,称为输出到输出偏斜。

12.器件到器件偏斜

由于制造工艺和使用环境的变化,造成的不同器件对应引脚之间的信号延迟差别,称为器件到器件偏斜。通常,器件之间的偏差远大于其他类型的偏斜。

13.动态偏斜

主要是指由于温度变化、地或电源噪声造成阀值电平随时间漂移,从而产生信号延迟的变化。

1561

1561

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?