目录

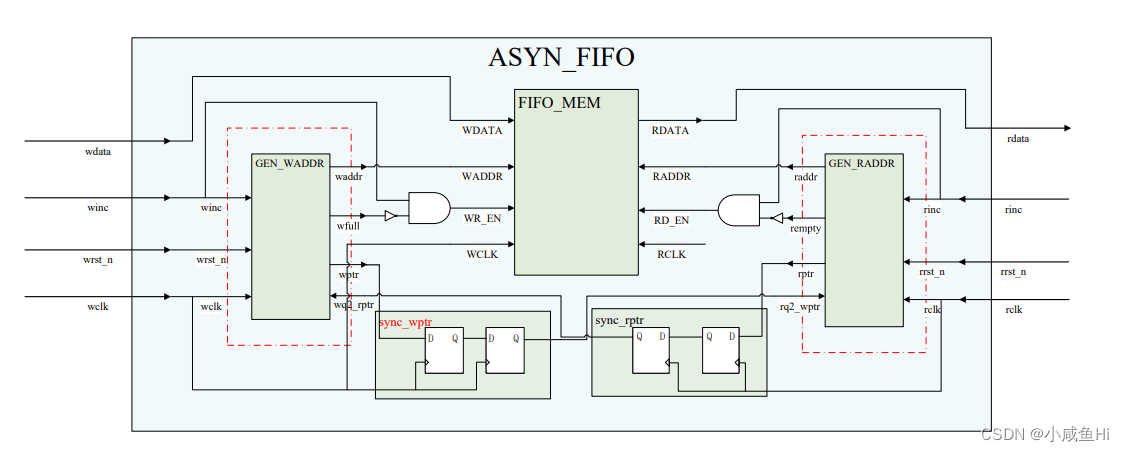

1.DUT 设计

本设计框图及信号端口如下,同经典asyn_fifo设计。

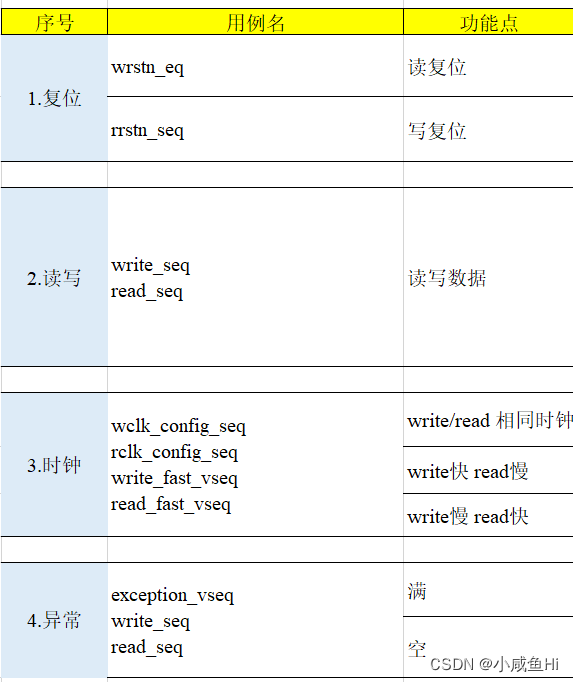

2.UVM 验证

2.1 测试功能点

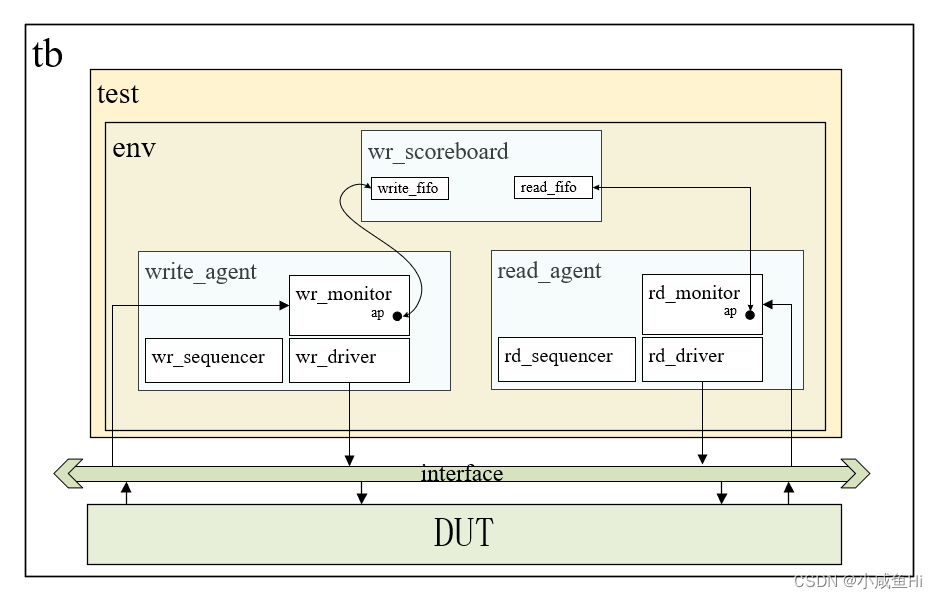

2.2 环境搭建

验证框图大致为:

2.2 功能仿真测试

2.2.1 复位测试

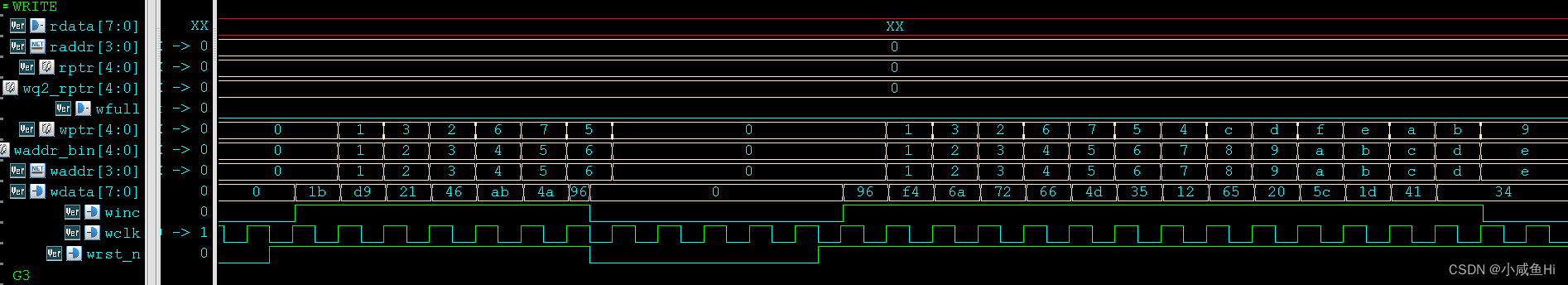

2.2.1.1 写复位

wrst_n 复位信号拉低,winc 和 wdata 随即拉低,wptr指向0。功能正常。

此测试共发送20笔write transaction,因为复位丢失的数据会在复位释放后,继续发送,比如上述的96,数据准备好了半个周期被复位信号打断,在下个clk的上升沿,并不能写入RAM中。在driver添加flag 实现不丢失包的发送。(不知道是不是多次一举)

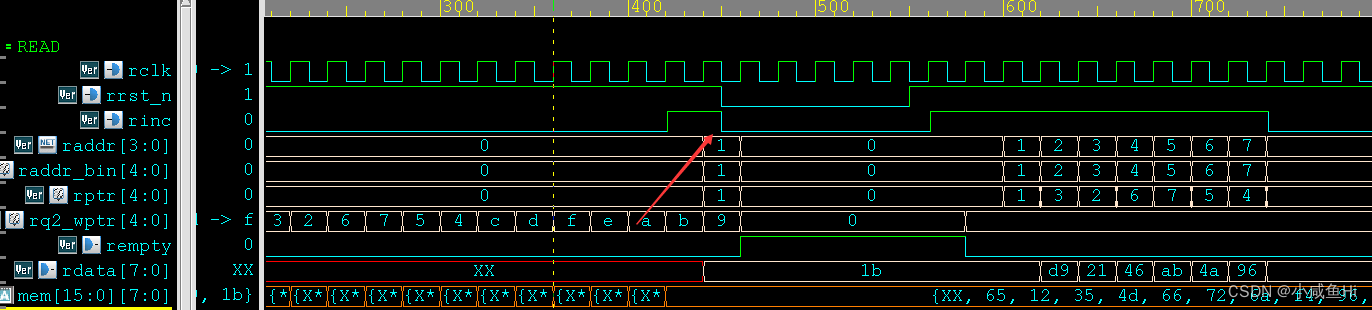

2.2.1.2 读复位

同样,读操作,在读复位信号拉低时,rinc 拉低,共发送10笔,由于复位信号打断的会重新驱动。

2.2.2 读写测试

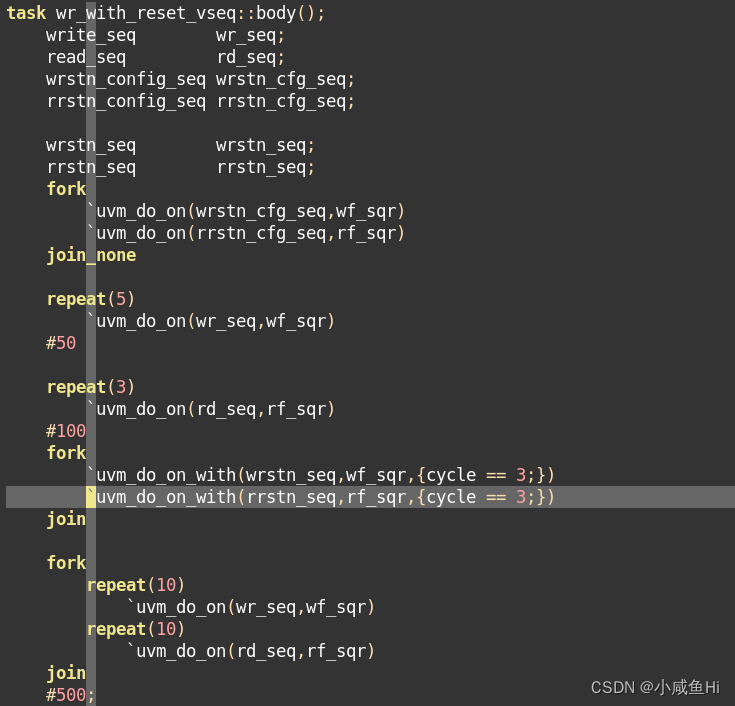

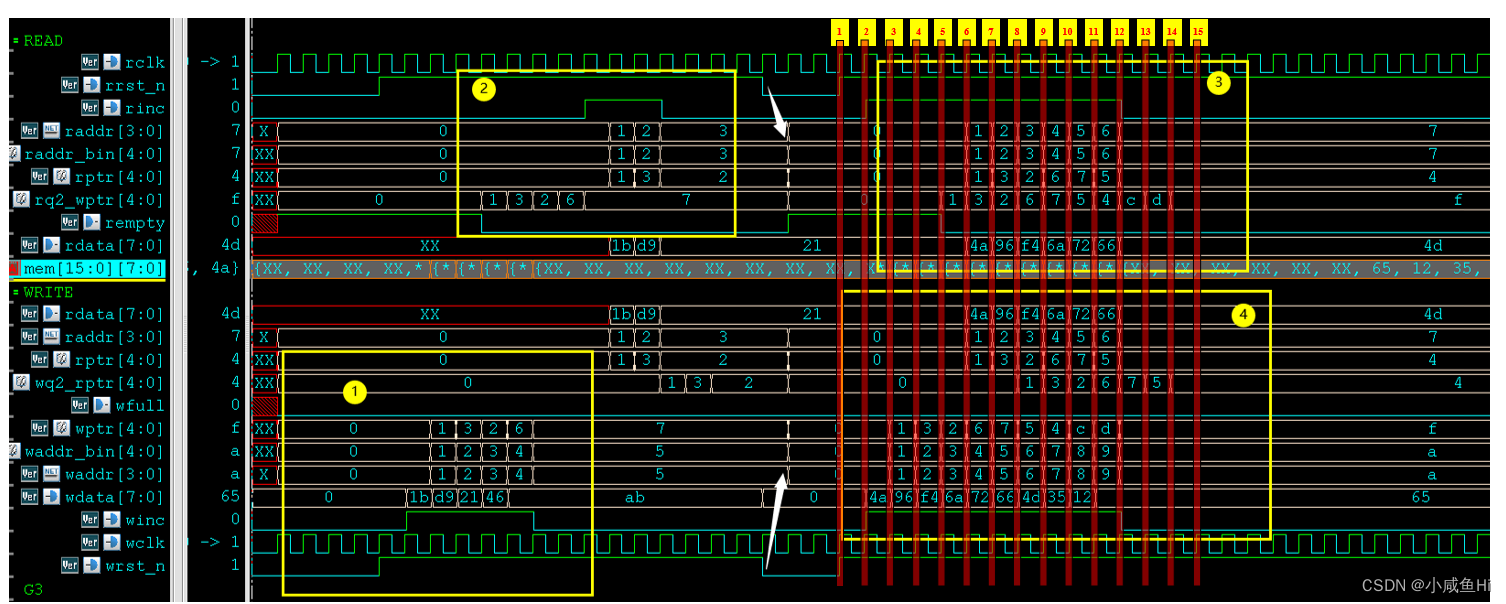

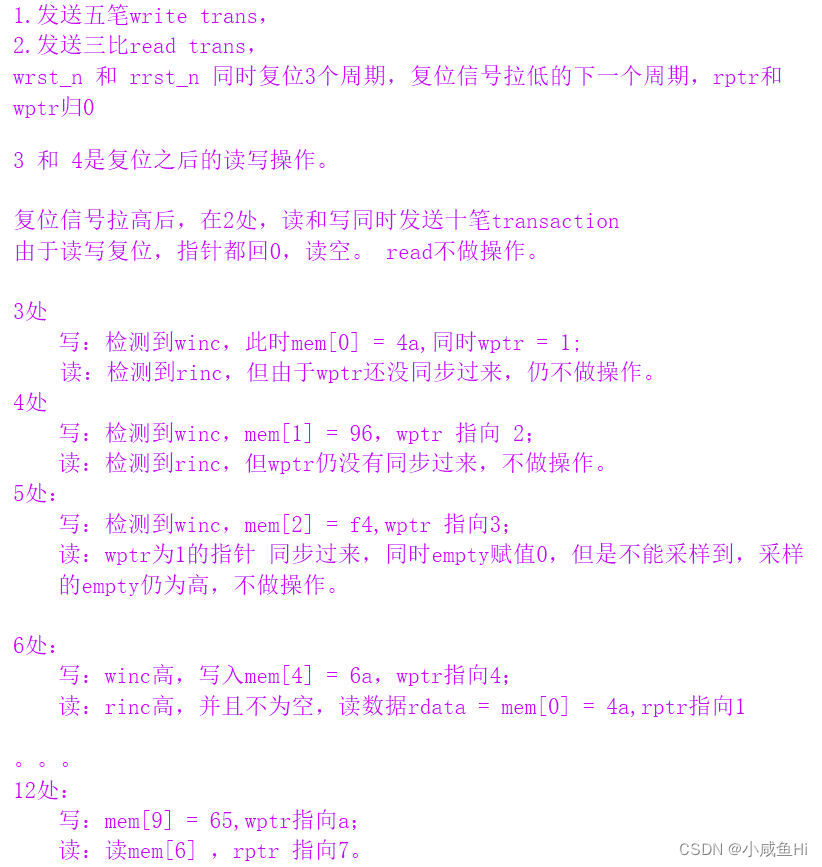

2.2.2.1 带有复位的读写测试

sequence激励代码:

复位之后,仍能正常工作。并且scoreboard中没有报错,共接收到15笔 write transaction,10笔 read transaction(实际发送了3+10),少了三笔 读空时候的invalid read transaction。

2.2.3 写满及读空 异常测试

1 写满

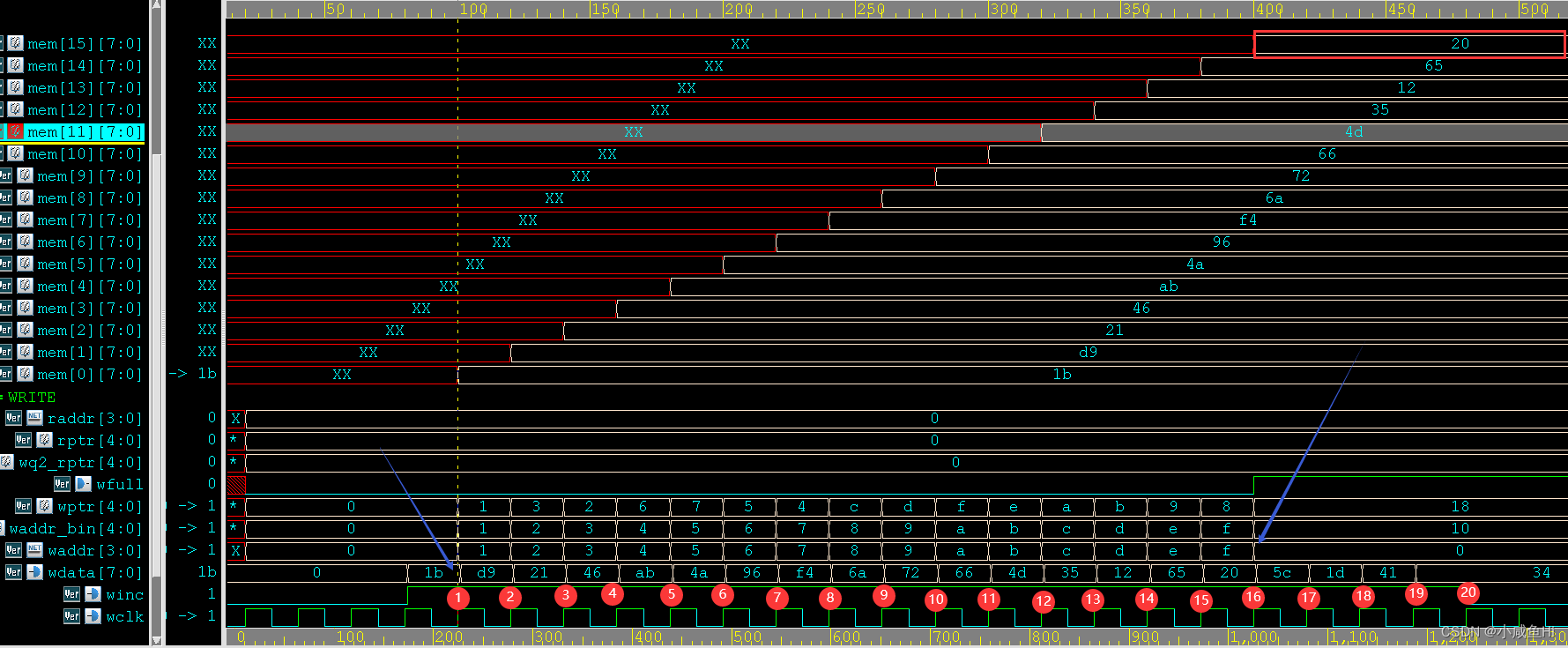

连续发送20笔write transaction。从1处开始,DUT write进去第一个数据,mem[0] = 1b… ,发送完第16个transaction后,wptr指向0x10,wfull立即拉高。指针保持不变。第17 18 19 20笔数据并没有写进去。发送完毕后,winc拉低。符合设计。

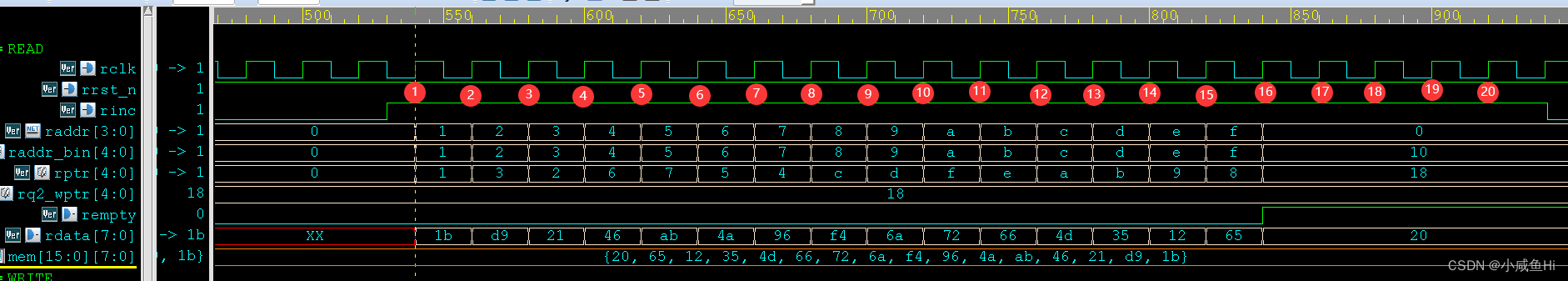

2. 读空

连续读20次。从1处,DUT 开始read,rdata被驱动。读完第16笔之后,rptr指向了0x18,rempty拉高。第17 18 19 20笔,dut没有进行操作,rdata无效。

读出的数据 和 上面写入的数据一致。

2.2.3 时钟测试

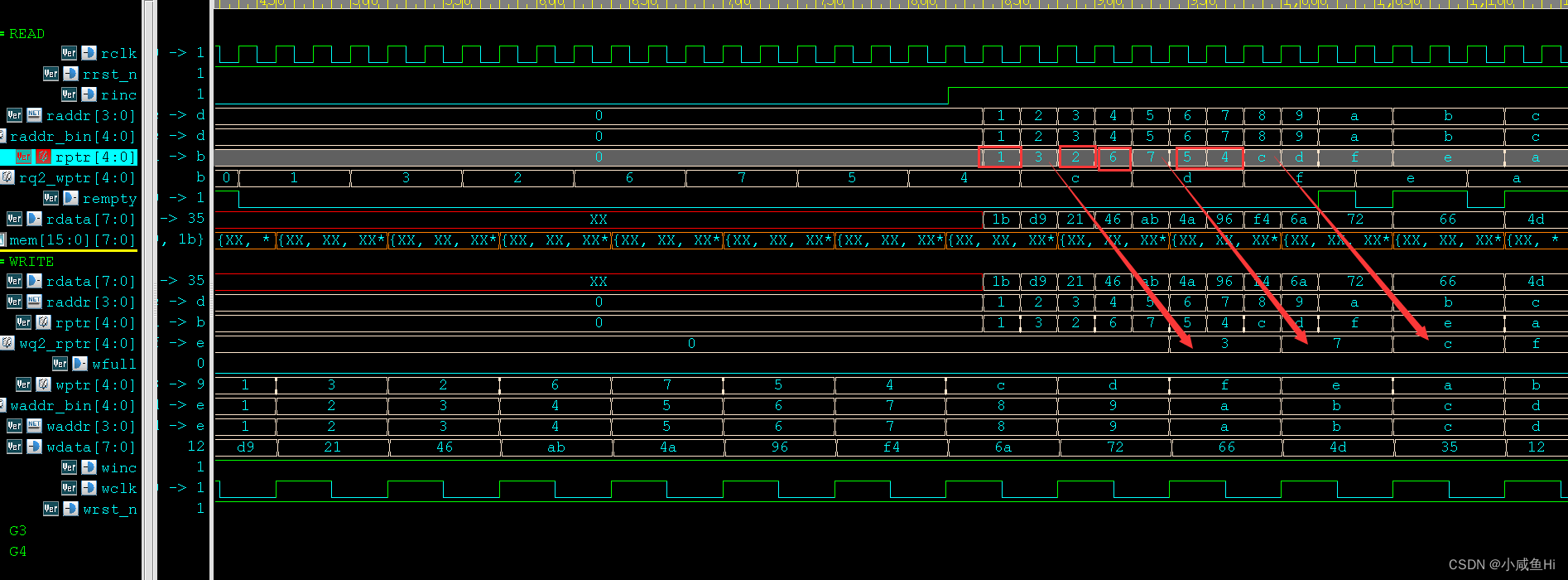

2.2.3.1 写快读满

虚空

2.2.3.2 读快写慢

1691

1691

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?