目录

Relationships between the channels

Dependencies between channel handshake signals

Read transaction handshake dependence

Write transaction handshake dependencies

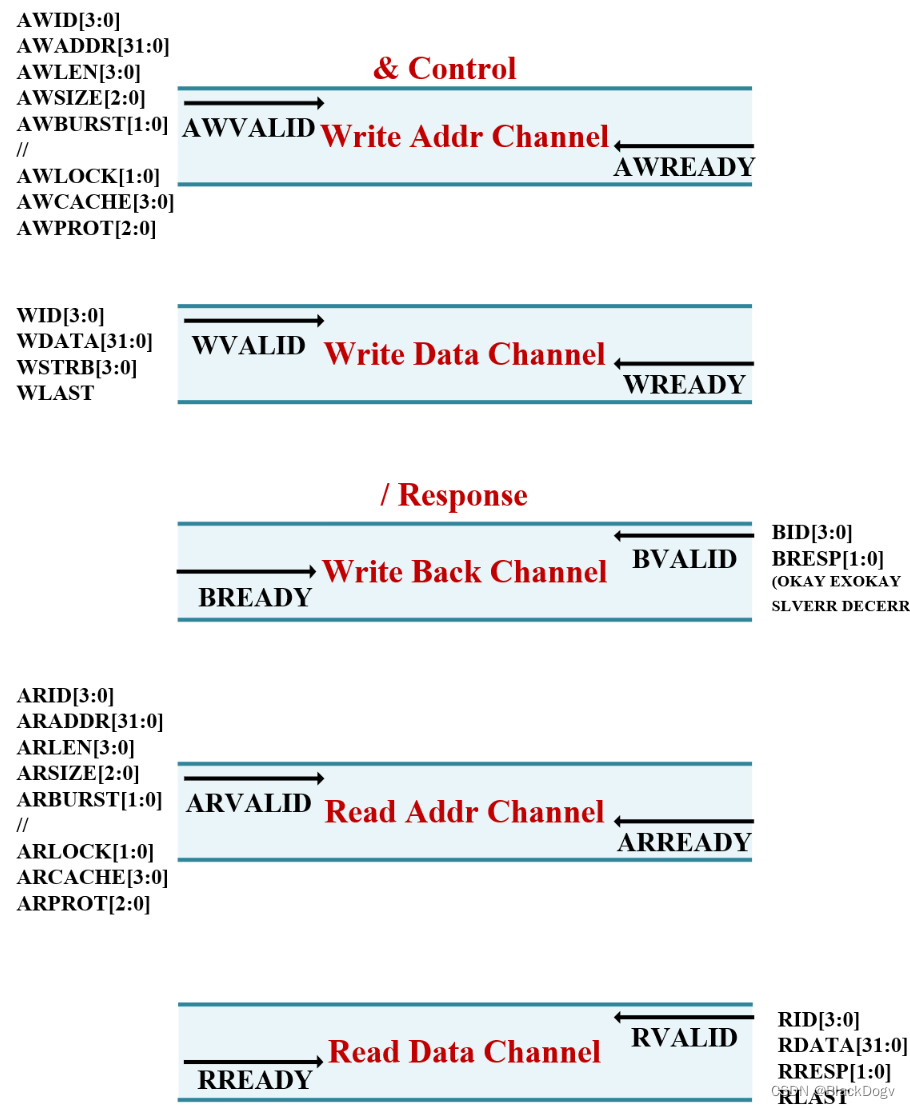

AXI的五个通道及信号:

Handshake process

明确概念:Master与Slave之间的握手信号valid和ready起于Source端和Destination端。Master或Slave既可以是S也可以是D。

Valid和Ready的顺序

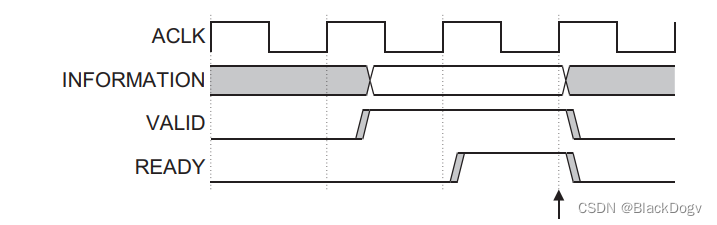

Valid before Ready

Source发送有效的信息,Valid置1,此时,数据与控制信息保持不变,直到S端检测到D端拉高的Ready信号。当D端检测到有拉高的Valid信号时,当D端空闲,可以接受数据时,即拉高Ready。

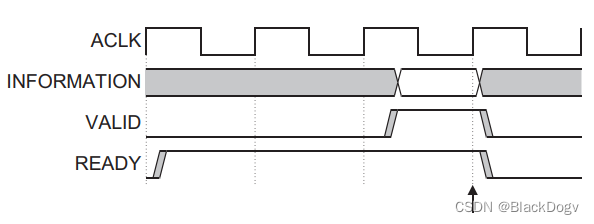

Ready before Valid

复位初始状态,可以保持ready一直置1,当检测到S端的Valid 高电平信号,开始传输数据。

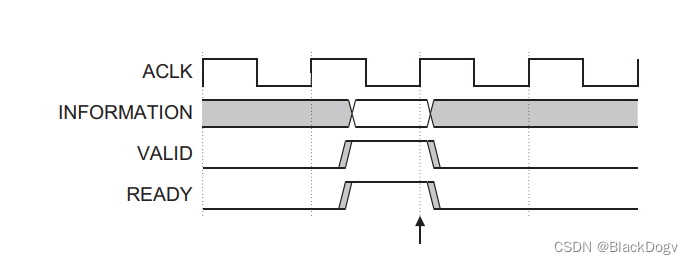

Valid with Ready handshake

S和D端在相同的周期内分别拉高Valid和Ready,可以立即传输。D端是怎么做到和S端同步拉高的?

Write address channel

Master只有当它驱动的地址和控制信息是有效的时候,才可assert AWVALID信号。必须保持拉高直到Slave接受并驱动AWREADY。

推荐AWREADY默认值为高。为低时,需要至少多耗费一个周期。

Write data channel

在一个Write burst期间,Master只有当它驱动的数据信息是有效的时候,才可assert WVALID信号。必须保持拉高直到Slave接受并驱动WREADY。

在一个write transaction完成后,Master必须拉高WLAST。

当WVALID为低时,WSTRB[3:0]可以是任意值,即使推荐保持或置LOW。

Write response channel

The slave can assert the BVALID signal only when it drives a valid write response. BVALID must remain asserted until the master accepts the write response and asserts BREADY.

The default value of BREADY can be HIGH, but only if the master can always accept a write response in a single cycle.

代码实现的情形:当检测WLAST置高时,即断言BVALID和BRESP。

Read address channel

The master can assert the ARVALID signal only when it drives valid address and control information. It must remain asserted until the slave accepts the address and control information and asserts the associated ARREADY signal.

The default value of ARREADY can be either HIGH or LOW. The recommended default value is HIGH, although if ARREADY is HIGH then the slave must be able to accept any valid address that is presented to it.

A default ARREADY value of LOW is possible but not recommended, because it implies that the transfer takes at least two cycles, one to assert ARVALID and another to assert ARREADY.

Read data channel

The slave can assert the RVALID signal only when it drives valid read data. RVALID must remain asserted until the master accepts the data and asserts the RREADY signal. Even if a slave has only one source of read data, it must assert the RVALID signal only in response to a request for the data.

The master interface uses the RREADY signal to indicate that it accepts the data. The default value of RREADY can be HIGH, but only if the master is able to accept read data immediately, whenever it performs a read transaction.

The slave must assert the RLAST signal when it drives the final read transfer in the burst.

Relationships between the channels

The relationship between the address, read, write, and write response channels is flexible.

Write : Data信息可以出现在相应的Address信息之前,或相同周期。

两个强制要求:

1. 读数据必须跟随相应的地址信息之后。

2.写相应必须跟随在相应的最后一笔write transfer之后。

Dependencies between channel handshake signals

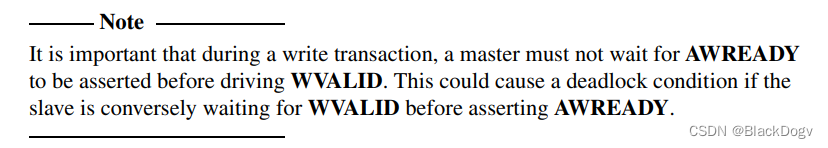

为了防止发生死锁,deadlock,必须有如下依赖关系。

In any transaction:

• the VALID signal of one AXI component must not be dependent on the READY signal of the other component in the transaction

• the READY signal can wait for assertion of the VALID signal.

单箭头表示信号的发出可以发生在指向的信号的之前或之后。双箭头表示信号的发出只能在之后。

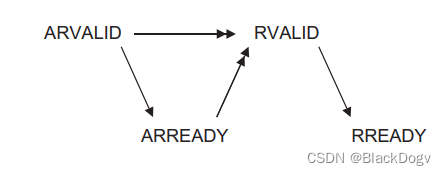

Read transaction handshake dependence

当地址握手完成后,数据的握手信号才开始。

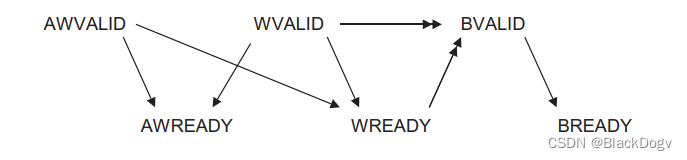

Write transaction handshake dependencies

3186

3186

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?