目录

前言

参考书籍:《Verilog HDL 数字设计与综合》第二版,本文档为第14章的学习笔记。

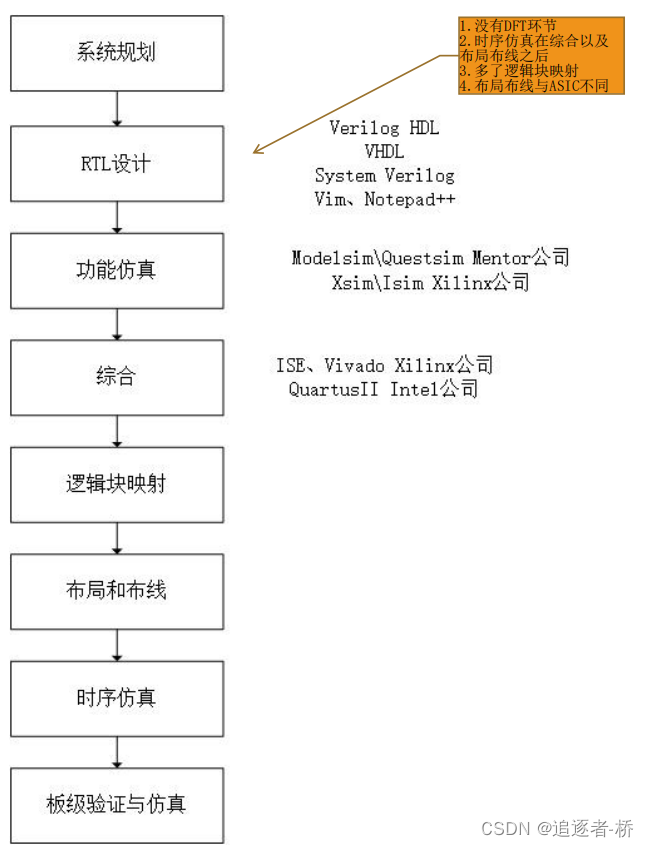

在讲解逻辑综合之前,先了解一下FPGA开发流程:

FPGA开发基本流程:

- 系统规划,系统功能,功能模块划分

- RTL设计,使用Verilog、System Verilog、VHDL进行描述

- 功能仿真,理想情况下的仿真

- 综合、编译、布局布线,FPGA厂商自带工具完成

- 时序仿真,时序分析约束

- 板级验证

由于目前的逻辑综合,大多数都由计算机辅助,深入了解较困难,需要看特定的文档或者参加一些特定公司的培训班,并不是所有都适用。本博文仅仅介绍了逻辑综合方法和问题,而不是全面了解逻辑综合技术。希望大家有一个基本的认识。

一、逻辑综合简介

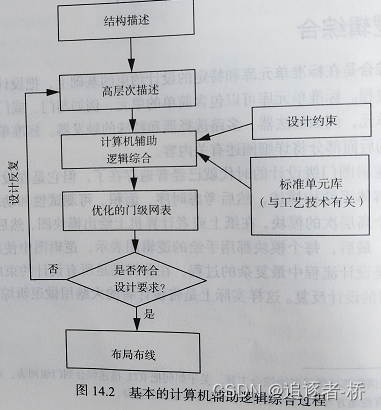

逻辑综合是在标准单元库(工艺库,每个公司可能会有差异)和特定的设计约束(时序、面积、可测试性和功耗)的基础上,把设计的高层次转换成优化后的门级网表的过程。

一开始逻辑综合是由人们自己动手实现的,而这样不仅增加了门槛高度,而且复杂操作时容易出错,开发时间也长。但是由于计算机辅助逻辑综合工具的出现改变的这种状况,并将硬件描述语言(HDL)推到了数字设计技术的最前沿。

二、Verilog HDL综合

这里讨论基于寄存器传输级(RTL)层次的综合。关于RTL级建模请参考:

三、7【Verilog HDL】RTL建模——数据流建模_追逐者-桥的博客-CSDN博客_rtl建模

三、7【Verilog HDL】RTL建模——数据流建模_追逐者-桥的博客-CSDN博客_rtl建模

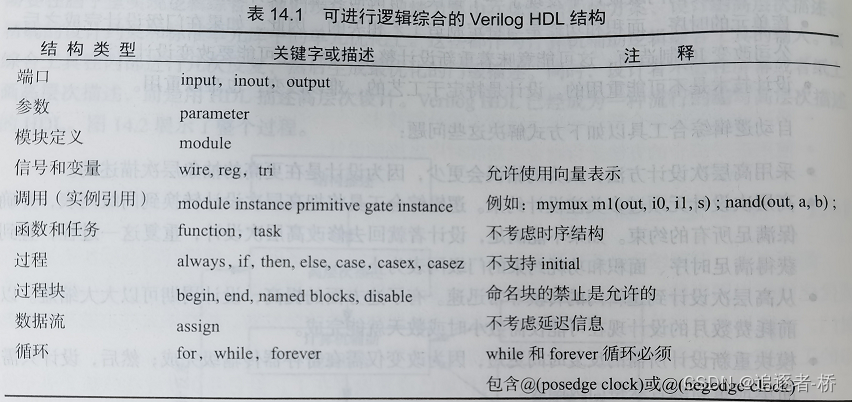

2.1 Verilog结构

提供的时时钟到时钟的RTL级描述,因此一些语句描述会有一些限制

- while和forever的使用需要注意,避免组合反馈。

- #<delay>结构在逻辑综合时会被忽略,因此综合前后会导致仿真的结果不一样。

- 逻辑综合工具不支持initial结构转换,因此设计RTL代码时,需要用复位来初始化电路信号。

- 定义未指定宽度的变量可能产生庞大的门级网表,逻辑综合工具可能根据变量定义生成不必要的逻辑。

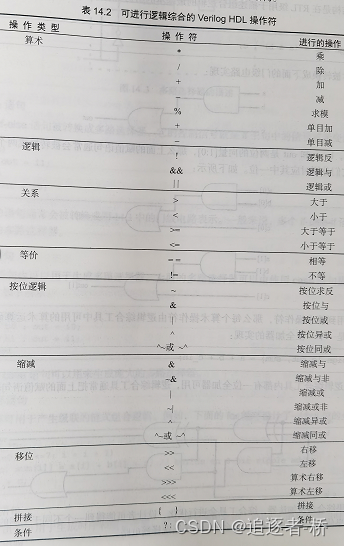

2.2 Verilog操作符

2.3 逻辑综合流程

这里是指RTL级描述转化成门级描述,并讨论下面流程的每一部分。

RTL描述

使用RTL级代码对模块功能和系统功能进行描述,其中包括逻辑和功能仿真。

翻译

RTL描述被逻辑综合工具转换成一个未经优化的内部中间表示。这个过程不考虑面积、时序和功耗等设计约束。本过程逻辑综合工具仅完成简单的内部资源分配。

未经优化的中间表示

逻辑综合工具根据数据结构在内部表示设计,这一部分不需要深入理解。

逻辑优化

优化逻辑,删除冗余逻辑。通过布尔逻辑优化技术,产生该设计优化后的内部表示。

工艺映射和优化

设计被映射到需要的目标工艺。如:ABC公司以0.65微米CMOS工艺生产IC芯片,该工艺称为ABC_100工艺(目标工艺)。工艺映射是将内部设计表示为由单元(目标工艺提供)实现的门逻辑。实现结果需要满足时序、面积和功耗等设计约束。当然在过程中需要进行工艺优化或者工艺相关优化。

- 工艺库

库单元是ABC公司用作IC制造的基本构件模块,单元集合称为工艺库。

-

设计约束

时序(有一个内部的静态时序分析器会检查时序)、面积、功耗

设计约束时,面积和时序约束之间成相反的关系,面积越小时序越长

优化后的门级描述

工艺映射完成后,生成由目标工艺部件所描述的优化后的门级网表。如果该网表满足要求约束,将送到ABC公司制作最终版图,制作IC芯片。否则需要重新进行综合设计以满足约束要求为止。

综合流程三点注意

- 对于微处理器高速电路,制造商的工艺库未必完整,因此可以制造自己的工艺库。

- 翻译、逻辑优化和工艺映射是在逻辑综合工具内部完成,对设计者是不可见的。工艺库确定制作者只能控制输入的RTL描述和设计约束的说明,因此因此RTL的设计准确高效很重要。

- 设计者只能见到RTL描述、工艺库、设计约束和最终优化后的门级设计。

- 亚微米级设计,互连延迟称为延迟中的主要因素

三、门级网表验证

3.1 功能验证

可以加到RTL代码上的功能验证和加到综合后门级网表级代码的验证。但是由于使用到工艺库的原因,如:ABC公司门级描述是基于VAND,VNAND等库单元,而Verilog HDL原语为and、nand。因此ABC公司必须提供一个仿真库,将and等同同于VAND。

典型Verilog仿真器调用如下:

//把激励施加到RTL描述上

>verilog stimulus.v mag_compare.v

//把激励施加到门级描述上

//使用-v选项将模拟库的abc_100.v包含进来

>verilog stimulus.v mag_compare.gv -v abc_100.v3.2 时序验证

通过时序仿真或者静态时序验证工具来检查门级网表的时序。如果违反时序需要重新设计RTL模块描述或者约束。

四、高级验证技术

随着设计平均门数的增加,验证很快称为设计中的瓶颈,设计小组在验证上的时间占了总设计实践的50%——70%,超过了设计所需时间。IC验证已经称为了一个热门的行业,由于数字IC验证内容比较多,且随着时代的发展验证方法和工具也在随时改变,如果想深入学习请单独参考验证的资料进行学习,这里不做过多的讲解。

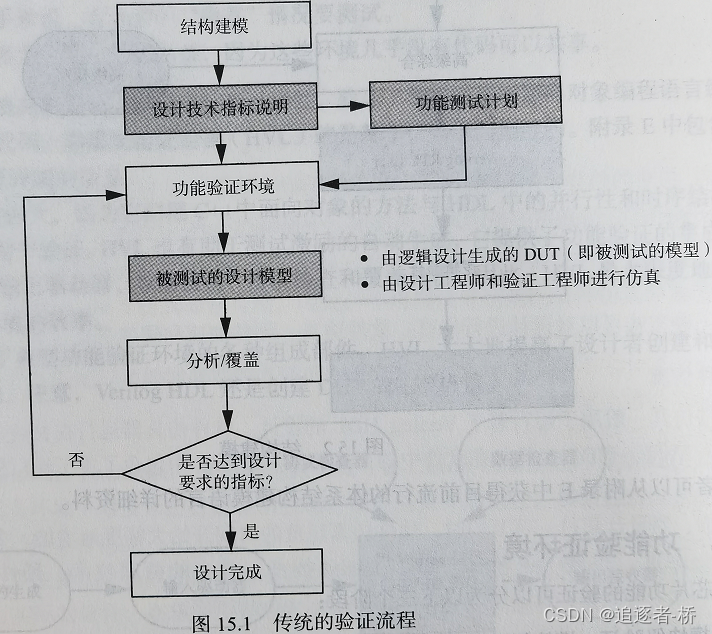

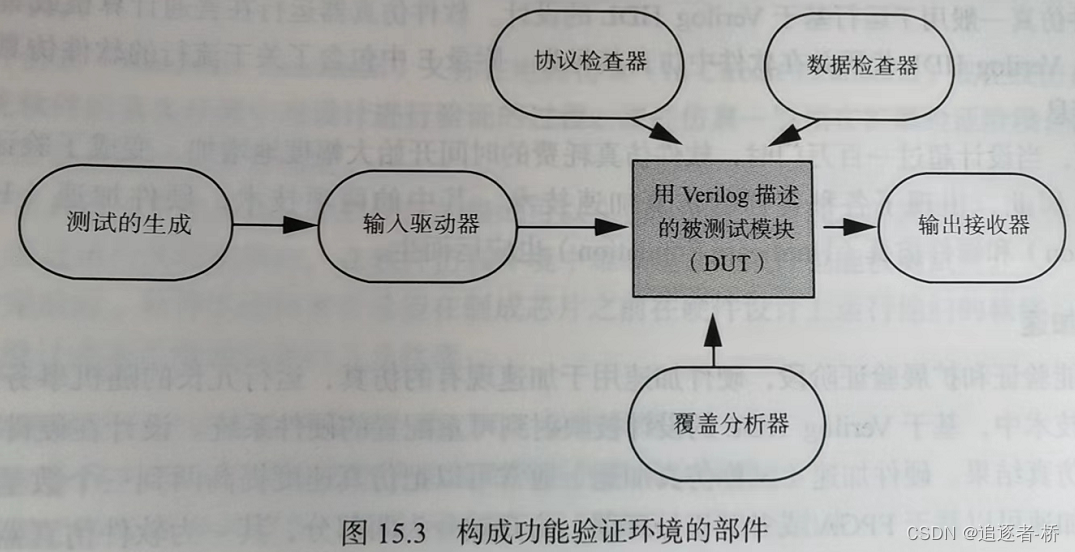

4.1 传统验证

体系结构建模

功能验证环境

可以分为一下三个阶段

- 模块级验证

- 全新片验证

- 扩展验证

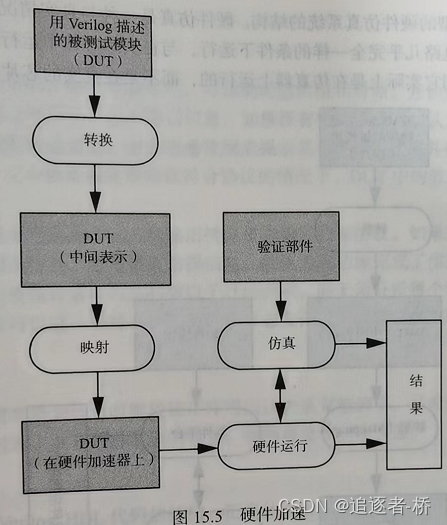

仿真

软件仿真、硬件加速和硬件仿真

分析

波形观察器和日志文件

覆盖

结构覆盖、功能覆盖

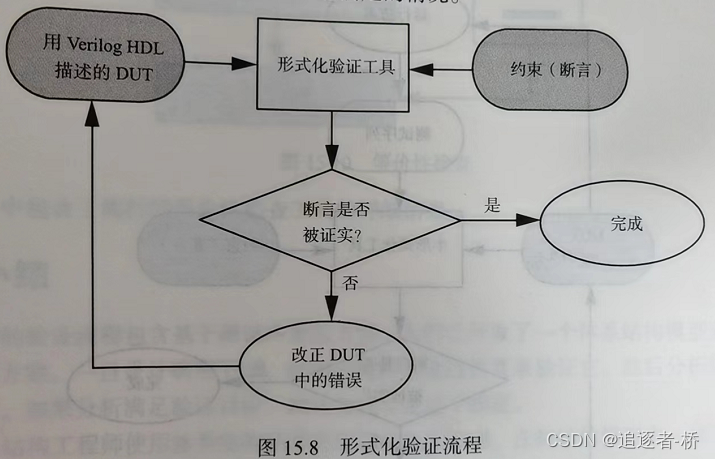

4.2 断言检查

时间断言检查和静态断言检查

4.3 形式化验证

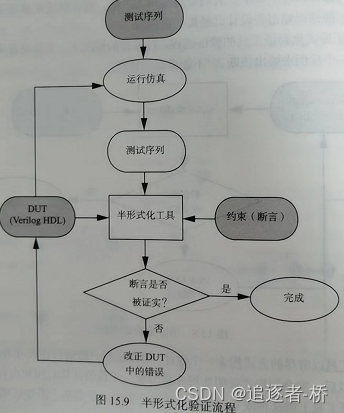

半形式化检验

等价形式检验

五、结业总结

上述只要没问题的话理论上就可以发工厂进行IC制作了。

至此这本书就到此结束了,已经学完。当然这仅仅只是入门,还需要继续学习。

推荐进阶书籍《Verilog 编程艺术》

当然本书的其他内容,都在本专栏里面了,大家可以查看学习

2819

2819

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?