1、工作环境约束

一方面是设置DC的工作环境,也就是DC要从在什么样的环境下对你的设计进行约束;另一方面是为了保证电路的每一条时序路径延时计算的精确性,特别是输入/输出路径的精确性,单单靠外部的输入延时和输出延时的约束是不够,还要提供设计的环境属性。

- 输入管脚:驱动能力,input transition time

- 输出管脚:RC模型,loading模型

- PVT conditions

- parasitic RC:寄生RC

(1)输出管脚loading模型:

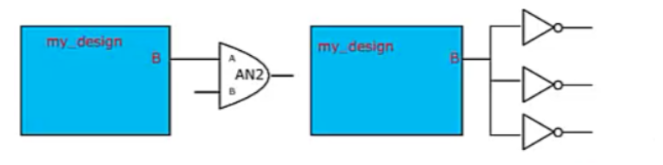

默认情况下,DC假设端口上的外部电容负载为0,我们可以指定电容负载,也可以使用load_of选项明确说明电容负载的值为工艺库中某一单元引脚的负载(一般是选择输入引脚)

左图:set_load [load of my_lib/AN2/A] [get_ports B] ;#采用工艺库my_lib里的AN2,A是cellAN2的pin脚

右图:set_load {expr[load of my_lib/inv1a0/A]*3} [get_ports B] ;#采用工艺库my_lib里的inv1a0,三个并联

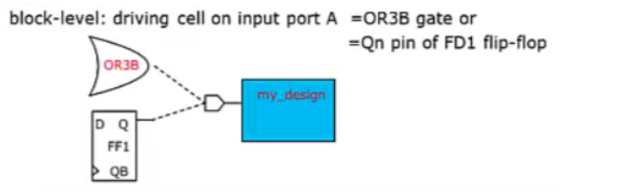

(2)input或者inout端口设置驱动强度

默认情况下,激励是理想的,没有transition;也可以直接设置输入端口的转换时间,set_input_transition 0.12 [get_ports A];当不知道输入转换时间时,可以调用库器件模型

set_driving_cell -lib_cell OR3B [get_ports A] ;#调用库lib_cell里的OR3B

set_driving_cell -lib_cell FD1 -pin Qn [get_ports A] ;#调用库lib_cell里的FD1的管脚Qn

(3)PVT(process,voltage,temperature)

工艺库单元通常用“nominal”电压和温度来描述其

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

9479

9479

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?