创建项目

“新建项目”向导将引导您完成定义项目名称和位置的步骤,添加源文件和约束文件,然后选择目标设备。参见附录B:Vivado命名惯例,了解有关命名文件和项目的信息。

小心!Windows操作系统的路径长度限制为260个字符,这可能会影响Vivado工具。若要避免此问题,请在创建时使用尽可能短的名称和目录位置项目,定义IP或托管IP项目,或创建块设计。

1.在Vivado IDE中,选择“文件” → 项目 → 新

注意:或者,也可以在“入门”页面上选择“创建项目”。

2.在“新建项目”向导中,查看概述,然后单击“下一步”。

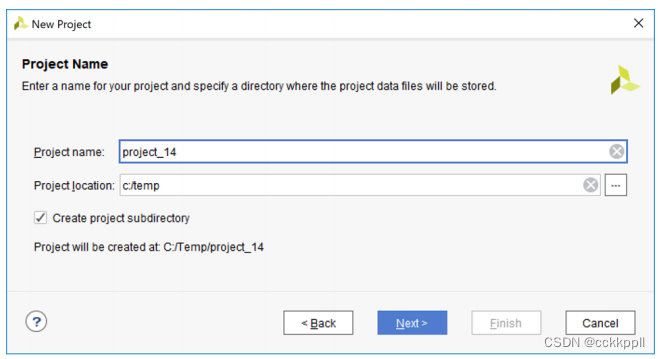

3.在“项目名称”页面中,设置以下选项,然后单击“下一步”。

•项目名称:指定项目的名称(例如,Project_1)。

•项目位置:指定新项目目录的位置。

•创建项目子目录:将与项目同名的子目录添加到指定的项目位置。

注意:默认情况下,此复选框处于启用状态,项目文件(扩展名为.xpr)创建于

<project_location>/<project_name>。为项目创建的所有文件夹和数据文件存储在<project_name>子目录中。如果禁用此复选框,则项目文件(.xpr扩展名)在<project_location>中创建,并为该项目创建所有文件夹和数据文件存储在该项目位置。

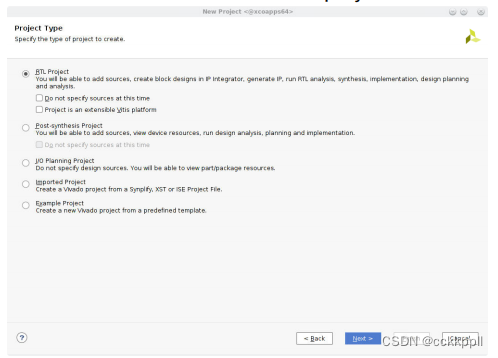

4.在“项目类型”页面中,指定项目类型,该类型决定源的类型与项目关联的文件。

5.根据您正在创建的项目类型,继续执行其中一个中的说明以下各节。向导的其余页面将指导您完成添加项目的适当来源。

•创建RTL项目

•创建合成后项目

•创建I/O规划项目

•导入外部项目

•用于处理项目的Tcl命令

创建RTL项目

RTL项目可以具有RTL、块设计、IP和/或RTL源。此对话框允许您指定在项目创建过程中添加哪些源。添加文件可以稍后在RTL代码期间添加开发、分析以及综合和实施。有关RTL的更多信息开发和分析,见第4章:RTL分析。

1.按照创建项目中的步骤进行操作。

2.在“项目类型”页面中,选择“RTL项目”,然后单击“下一步”。

注意:如有必要,您可以选择此时不指定来源。这将跳过添加的步骤设计源,使您能够选择目标零件并创建项目。

注:AMD Vitis使用可扩展平台™ 结合软件内核的软件平台。

通过设置此项目属性,平台属性可以添加接口,然后可以通过Vitis软件平台进行增强。有关可扩展平台的更多信息,请参阅创建Vitis中的嵌入式平台在Vitis统一软件平台文档中的应用加速开发(UG1393)。

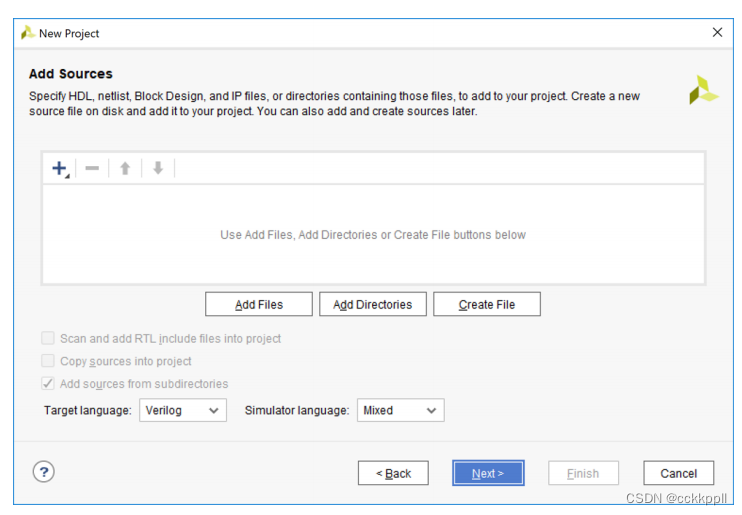

3.在“添加源”页面中,设置以下选项,然后单击“下一步”:

•添加文件:打开文件浏览器,以便选择要添加到项目中的文件。您可以添加RTL项目的以下文件类型:Verilog、VHDL、SystemVerilog、BD、XCI、EDIF,NGC、BMM、ELF和其他文件类型。

注意:在“添加源文件”对话框中,每个文件或目录都由一个图标表示作为文件或文件夹。红色小方块表示它是只读的。

•添加目录:打开目录浏览器,从所选目录添加源文件目录。指定目录中具有有效源文件扩展名的文件将添加到项目。

•从子目录添加源:指定工具应扫描列出的目录的用于其他源的目录树。

•创建文件:打开“创建源文件”对话框,您可以在其中创建新的VHDL,Verilog、Verilog头或SystemVerilog文件。在“创建源文件”对话框中,设置以下选项:

•文件类型:指定以下文件格式之一:Verilog文件(扩展名.v)、Verilog头文件(.vh扩展名)、SystemVerilog文件(.sv扩展名)和VHDL文件(.VHDL扩展名)或内存文件(.mem扩展名)。

•文件名:指定新的HDL源文件的名称。

•文件位置:指定创建文件的位置。

注意:文件的占位符会添加到源列表中。单击时会创建文件完成

•库:指定文件或目录的RTL库。您可以选择库名称,或者通过在库文本字段中键入来指定新的库名称。

注意:此选项仅适用于VHDL文件。默认情况下,HDL源被添加到xil_defaultlib库。您可以根据需要创建或引用其他用户VHDL库。对于Verilog和SystemVerilog文件,将库设置为xil_defaultlib。

•的HDL源:指定要加载的源是否是的RTL源文件合成和模拟或仅用于模拟的RTL测试台。

•删除:从要添加的文件列表中删除选定的源文件。

•上移/下移:按列表顺序上移/下移文件或目录。的顺序在下游过程中,文件会影响详细说明和编译的顺序例如合成和模拟。

•扫描并将RTL Include文件添加到项目中:扫描所有RTL源文件并添加任何被引用的Verilog将文件包括在项目结构中。

•将源复制到项目中:将添加的源文件和include文件复制到本地项目目录,而不是引用原始文件。如果您添加了源的目录使用“添加目录”的文件,复制文件时会维护目录结构本地加入项目。有关详细信息,请参阅使用远程源或复制源到项目。

•从子目录添加源:从目录的子目录中添加源文件使用Add Directories指定。

•目标语言:将设计的目标语言指定为Verilog或VHDL。新的RTL文件默认为指定的目标语言。输出文件是从生成的以指定的目标语言进行设计。

•模拟器语言:指定生成输出产品的语言模拟以及用于第三方模拟脚本的文件类型。了解更多

信息,请参阅Vivado Design Suite用户指南:逻辑仿真(UG900)。

•添加源:调用文件浏览器,以便您可以选择AMD核心实例(XCI)文件,它们是Vivado Design Suite的原生文件,这是一个核心容器(XCIX)文件,是一个IP的文件表示或CORE Generator核心(XCO)文件。您也可以添加块Vivado IP集成商的设计文件(BD),或Mathworks Simulink®项目文件(SLX或MDL)用于DSP子设计。

XCI文件是一个IP-XACT组件实例XML文件,用于记录项目的值用于创建IP的选项、自定义参数和端口参数。XCIX是包含整个IP目录和所有输出产品的压缩二进制文件,包括XCI、合成、仿真和支持文件。请参阅核心容器部分有关更多详细信息,请参阅Vivado Design Suite用户指南:使用IP(UG896)进行设计。

注意:当您添加使用Vivado IP目录创建的XCI或XCIX IP时,Vivado IDE自动将所有可用的生成目标(如HDL源)导入到项目中。什么时候你运行合成,IP和顶层设计被合成在一起。您还可以使用从Vivado IDE中将参数化内核加载到项目中IP目录,如使用IP源中所述。

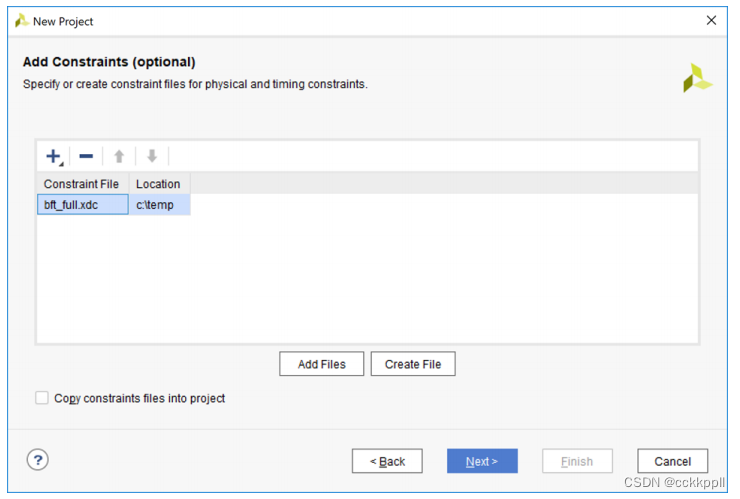

4.可选:在“添加约束”页面中,设置以下选项,然后单击“下一步”:

•添加文件:调用文件浏览器,以便选择Synopsys Design Constraint(SDC)或要添加到项目中的XDC文件。

•创建文件:为项目创建一个新的顶级XDC文件。

•删除:从约束列表中删除选定的文件。

•上移/下移:按列出的顺序向上或向下移动约束文件。命令依赖于订单;约束的最后一个读取命令覆盖的效果早期命令。

•将约束文件复制到项目中:将约束文件拷贝到本地项目目录中而不是引用原始文件。

注意:在与RTL或网表源文件关联的相同目录中找到的任何SDC或XDC文件将自动列为要添加到项目中的约束文件。您可以删除根据需要提供这些文件。

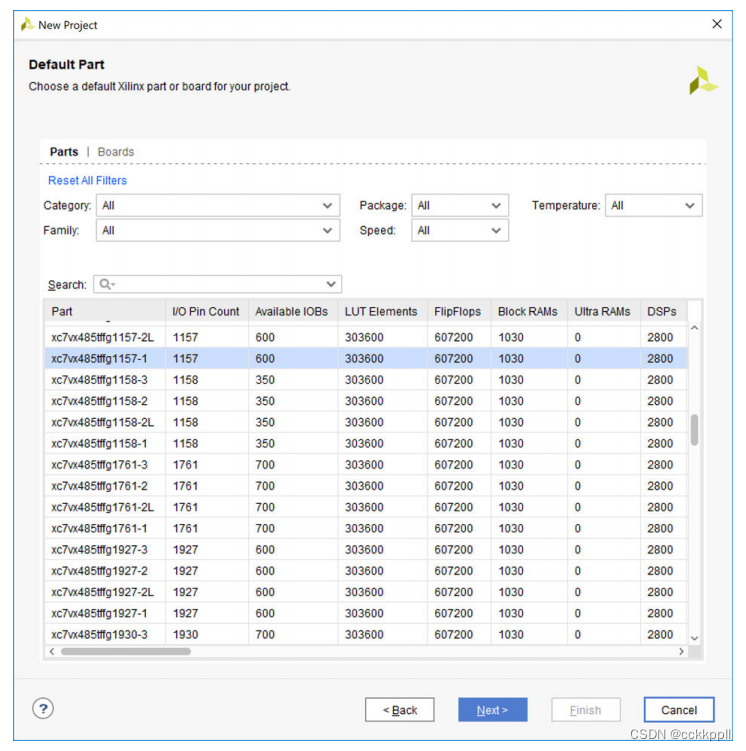

5.在默认部件页面中,选择AMD部件或目标设计平台(TDP)板,然后单击“下一步”:

•部件:列出可用的设备。有关设备资源的信息显示在表中视图,例如I/O引脚计数、查找表(LUT)和触发器(FF)的数量,以及可用块RAM。您可以使用“产品类别”、“族”、“子族”、,

包装、速度等级和温度等级过滤器。您也可以使用“搜索”字段查找特定设备。Vivado Design Suite安装过程允许您选择要安装的AMD设备以减少Vivado工具所需的磁盘空间。如果您需要针对当前未安装在您的系统上,您必须退出该工具并安装其他感兴趣的部分。请参阅《Vivado Design Suite用户指南:发行说明》中的此链接,有关详细信息,请参阅安装和许可(UG973)。

•板:列出可用的开发板或TDP板,以及上使用的AMD部件板有关设备资源的信息显示在与表视图类似的表视图中如零件所示。您可以使用供应商、显示名称和Board Rev过滤列表过滤器。您也可以使用“搜索”字段来查找特定的电路板零件。

建议:当您选择支持Vivado Design Suite平台板的板时流,您可以利用Vivado IP目录和Vivado集成程序中的自动化功能。例如,您可以自动为支持可用接口的IP创建I/O约束在选定的板上。有关更多信息,请参阅使用Vivado Design Suite平台板流。

6.在“新建项目摘要”页面中,查看定义项目的选定选项,以及单击“完成”。单击“完成”时,将创建项目目录结构应使本地项目被复制,并编写项目文件。任何设计必须按照以下步骤所示定义需要创建的源,然后写入磁盘。

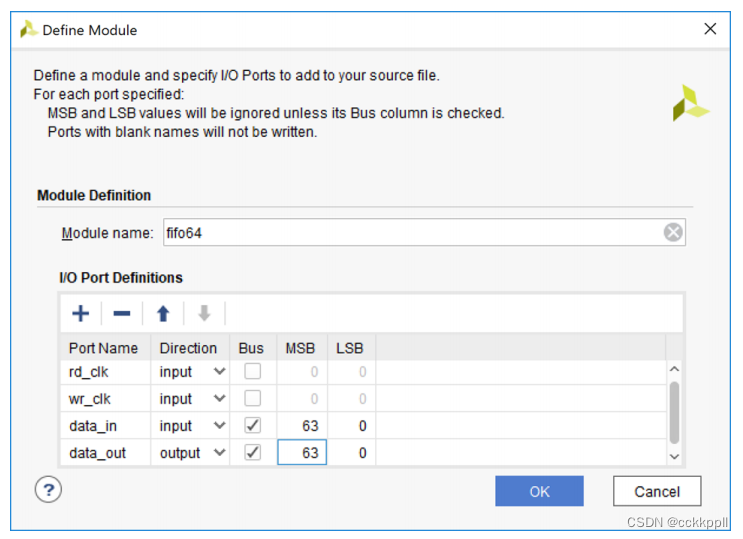

7.可选:如果您在步骤3中使用了创建文件选项,则创建一个新的HDL模块并添加它对于项目,将显示“定义模块”对话框。

RTL源文件将被创建并添加到您的项目中。“源”窗口列出新定义的模块。这些新的源文件定义了Verilog模块或VHDL实体,但是您必须编辑文件来定义这些块的逻辑或体系结构。编辑新的在Vivado IDE文本编辑器中的源文件,双击该文件或从中选择“打开文件”右键单击菜单。有关编辑新创建的文件的信息,请参见编辑源文件。

1202

1202

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?