本文以一个简单工程为例,介绍使用Vivado新建工程、代码的编写、Testbench代码的编写、波形仿真分析、引脚约束、生成bit流文件、通过JTAG将网表下载到开发板、程序的固化与下载全流程。

文章目录

1.新建工程

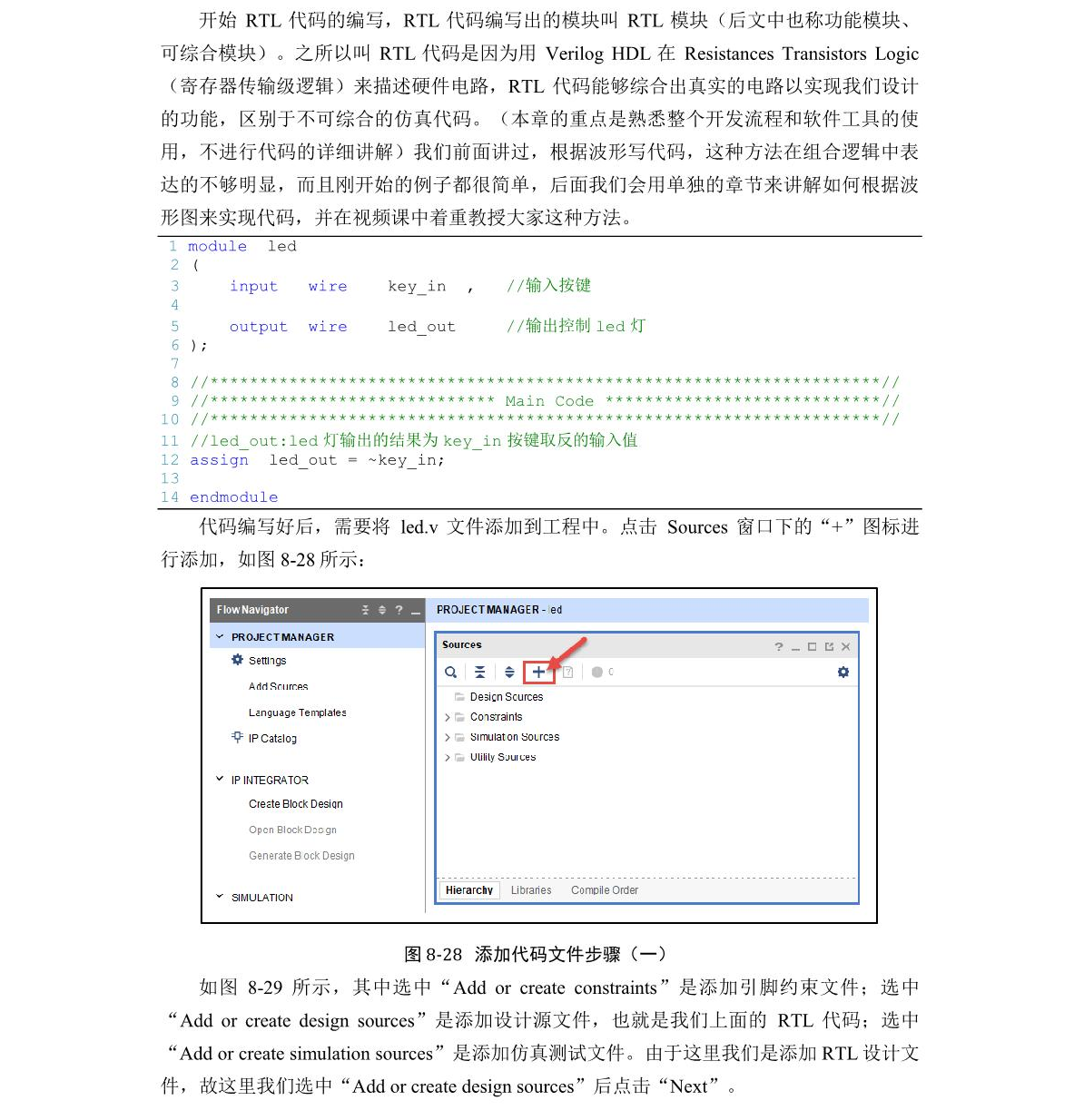

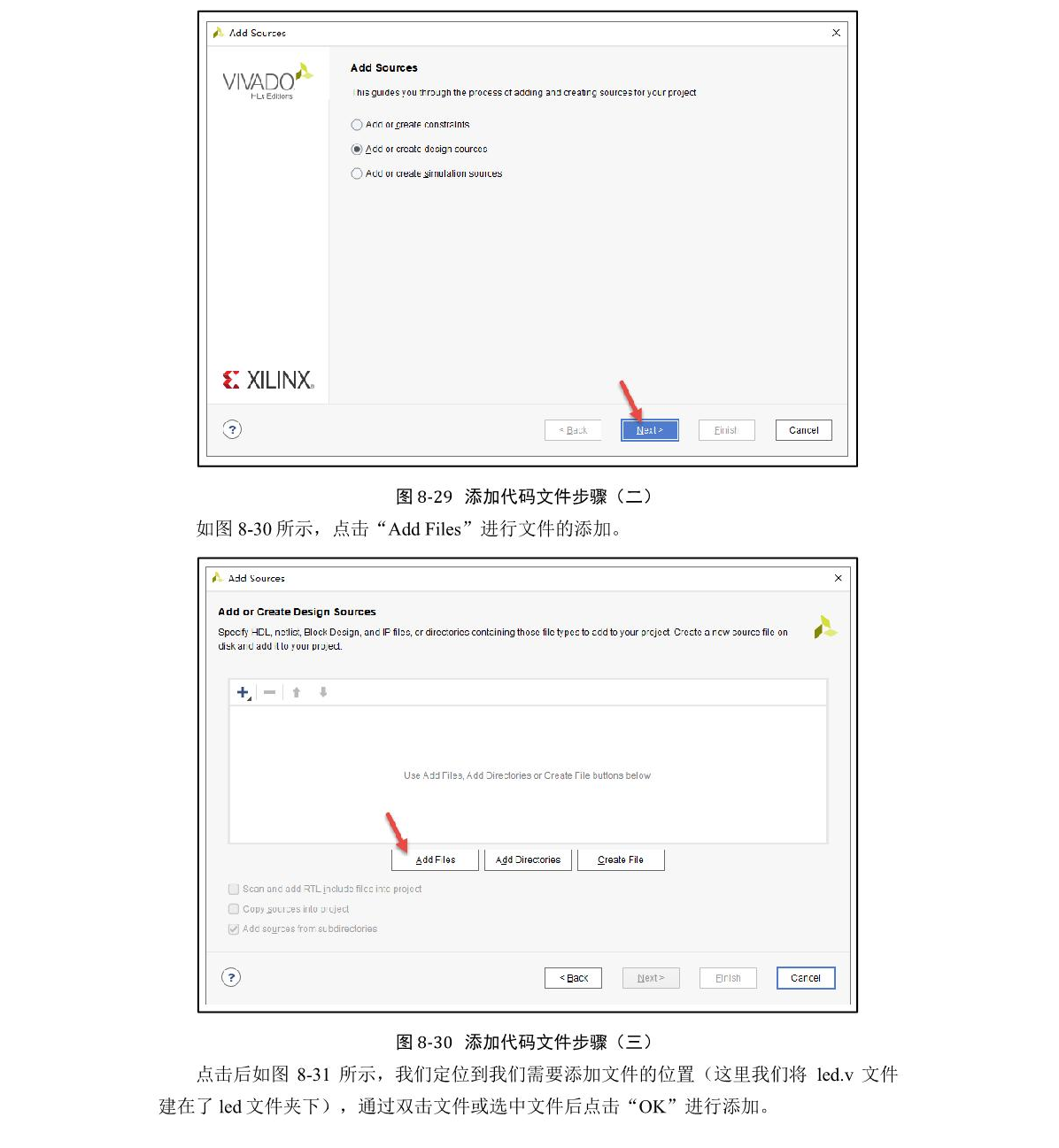

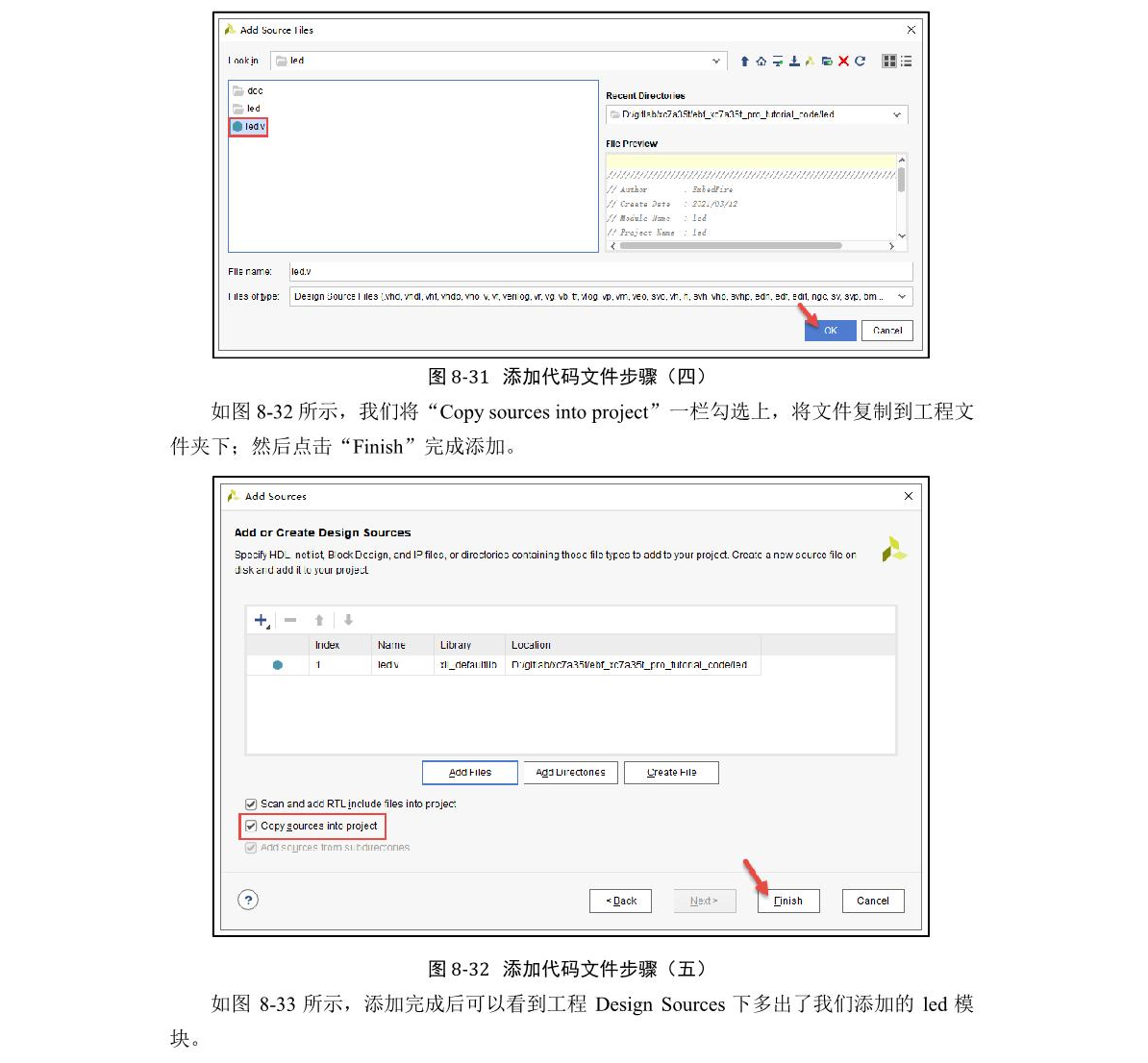

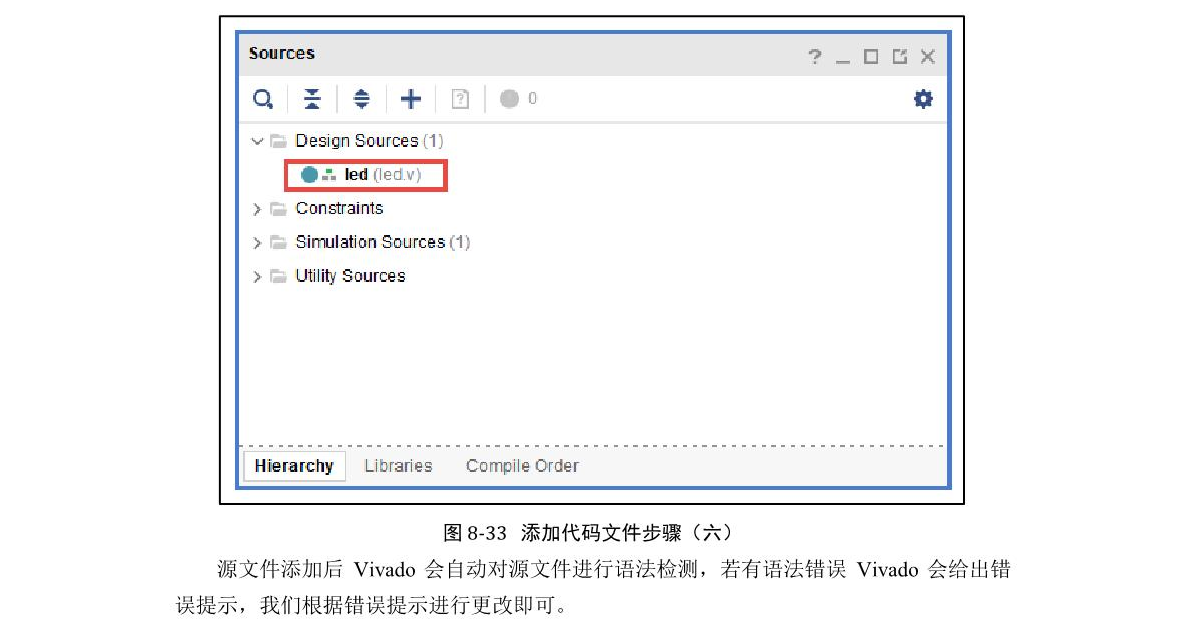

2.RTL代码的编写

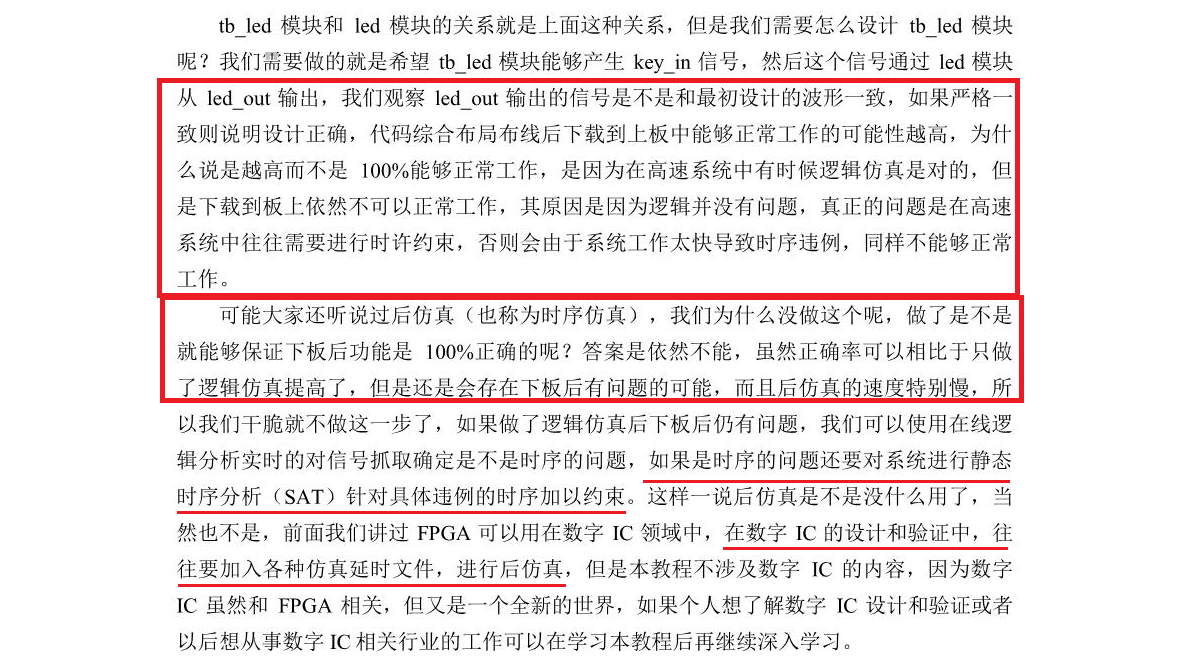

3.Testbench的原理

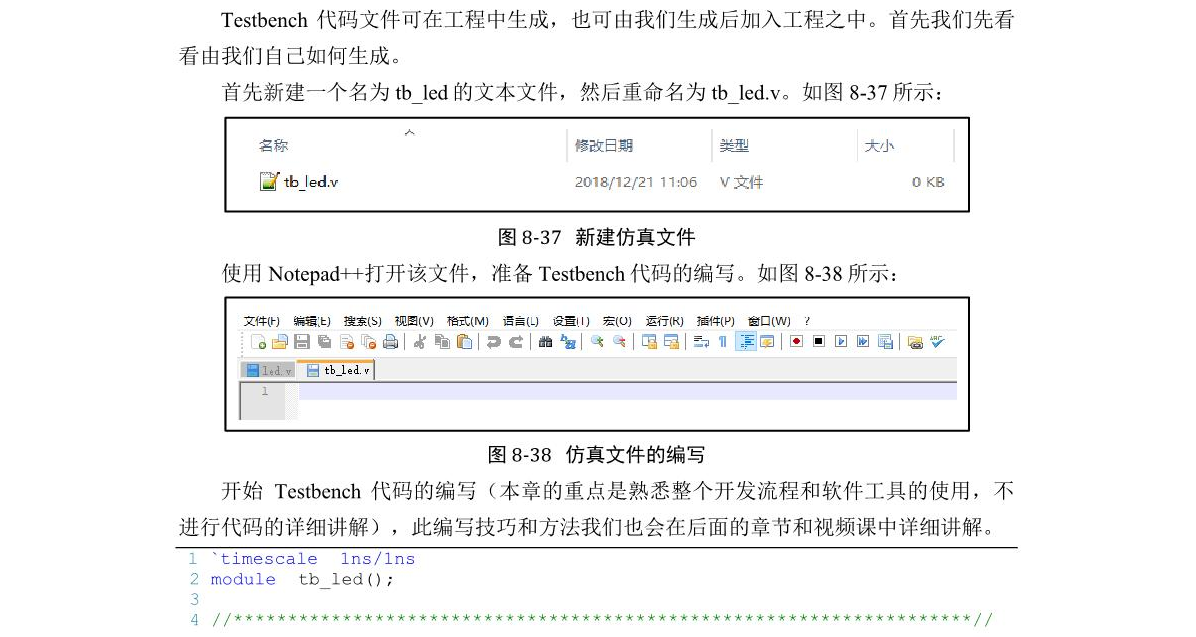

4.Testbench代码的编写

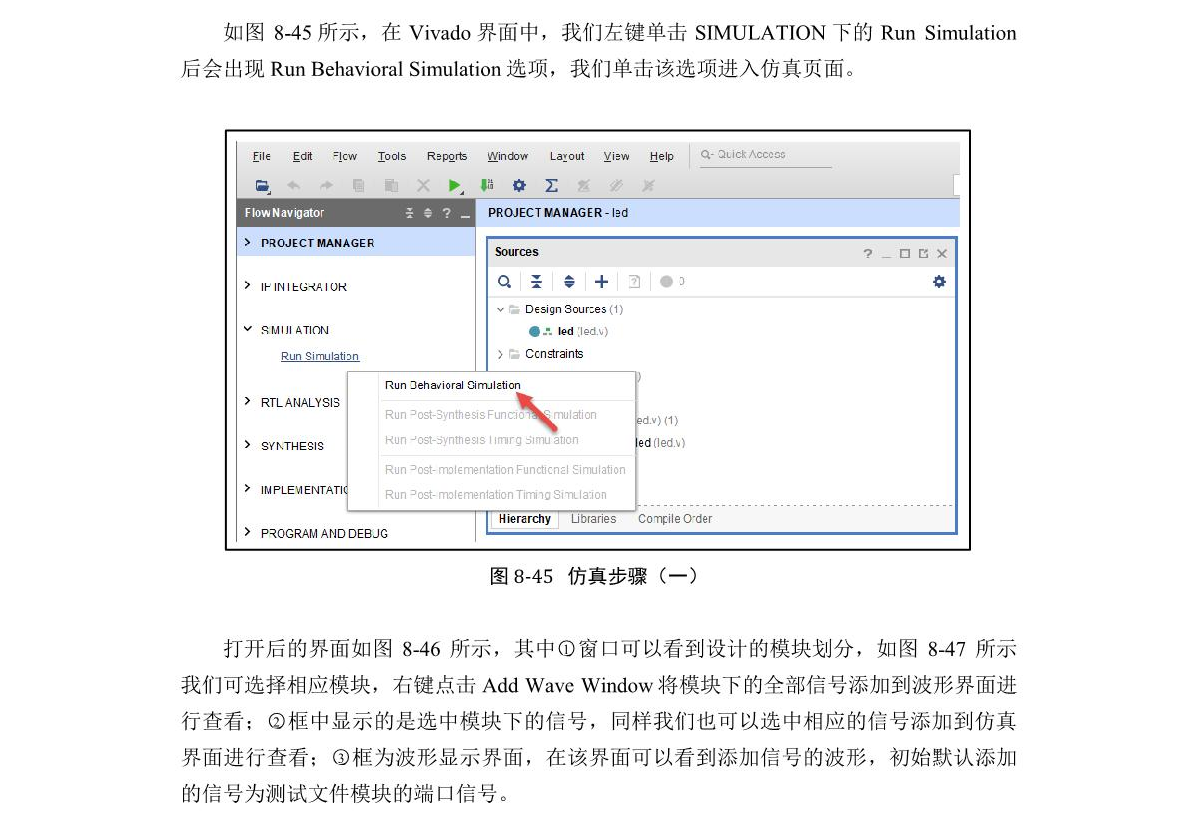

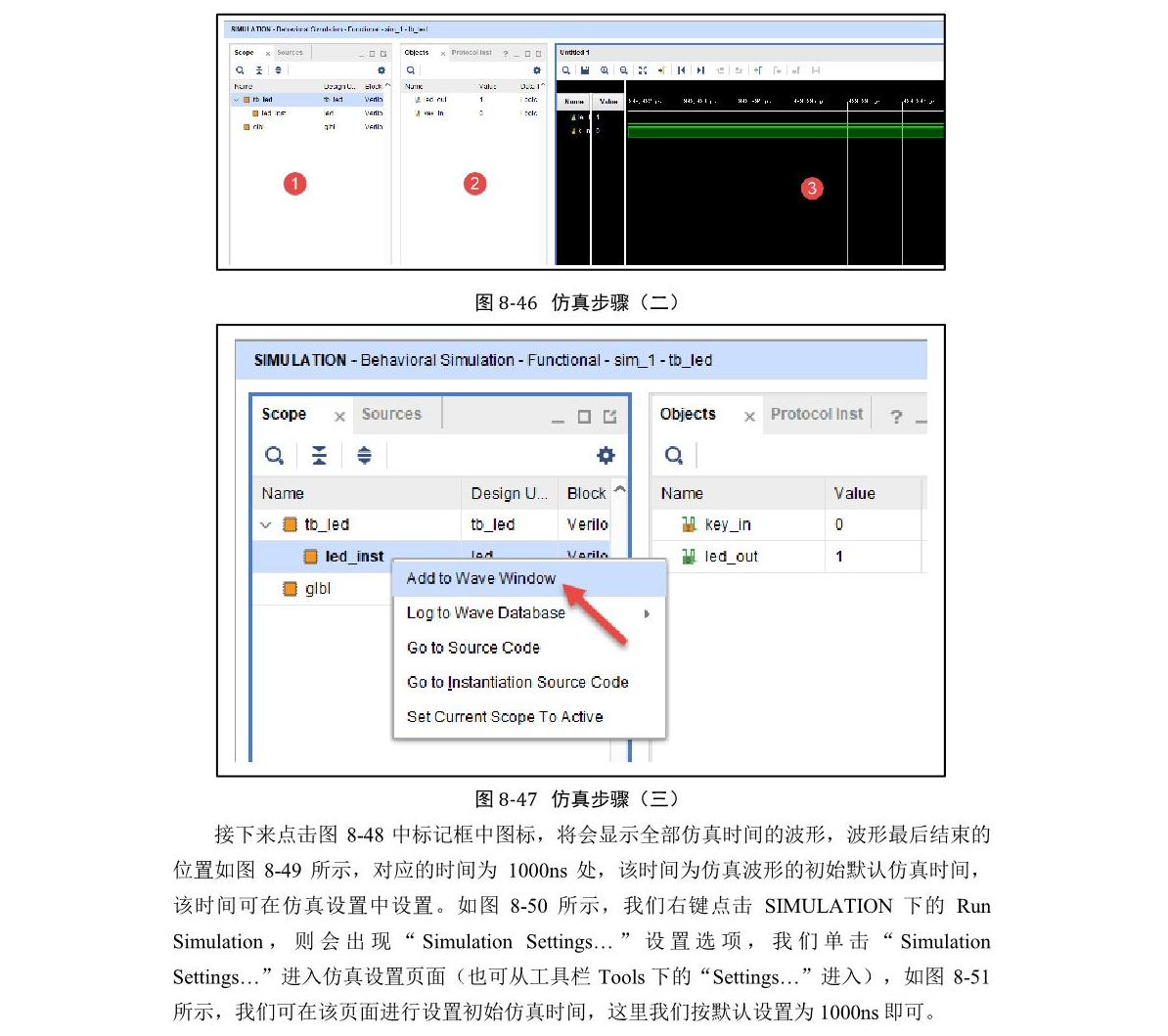

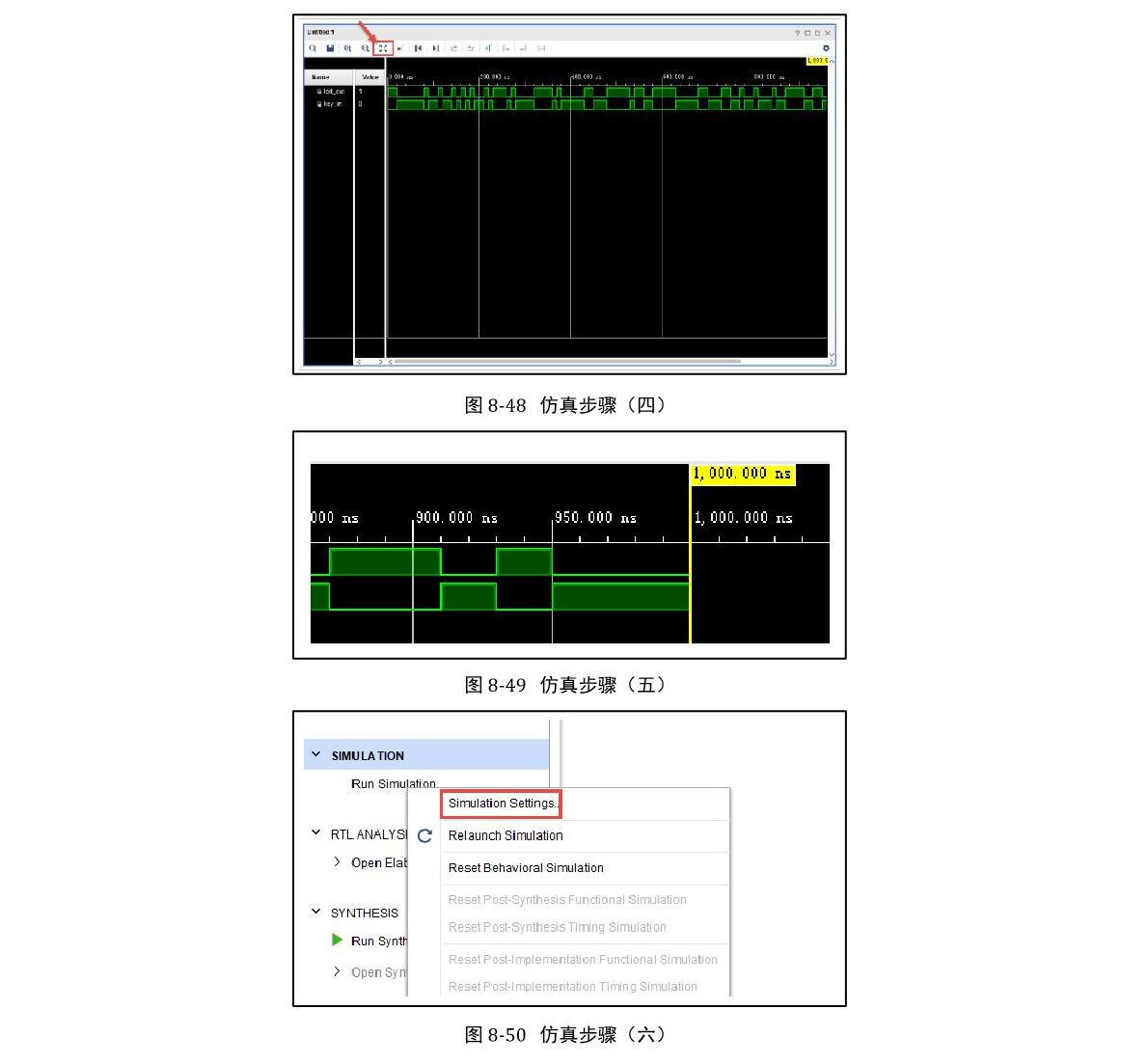

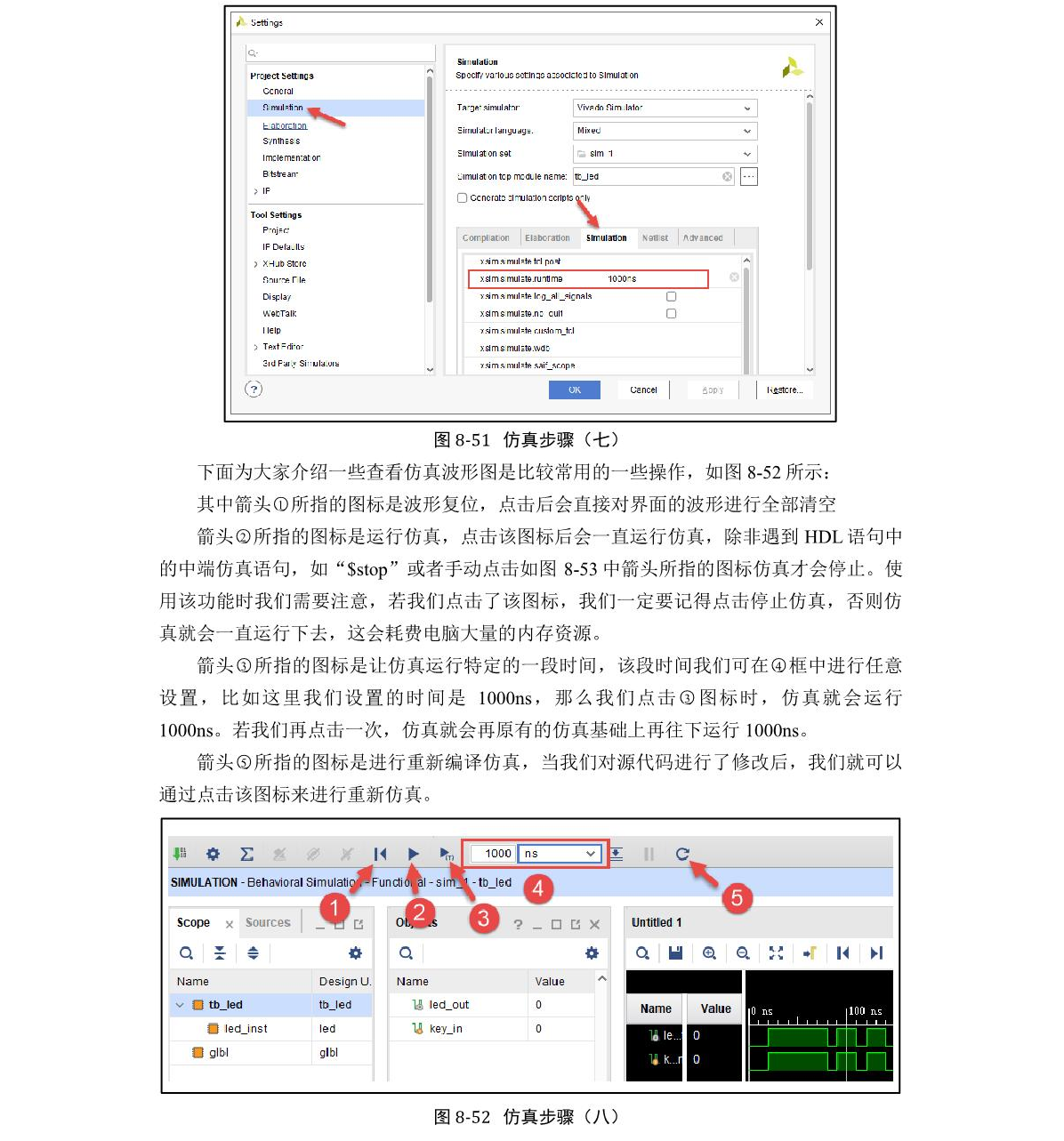

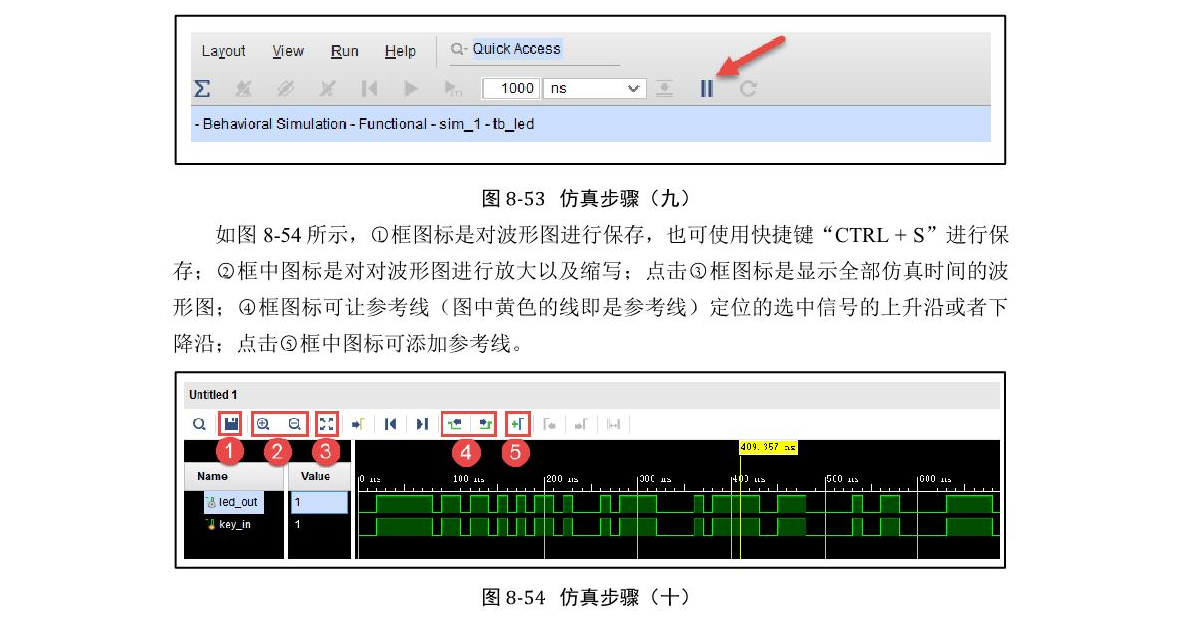

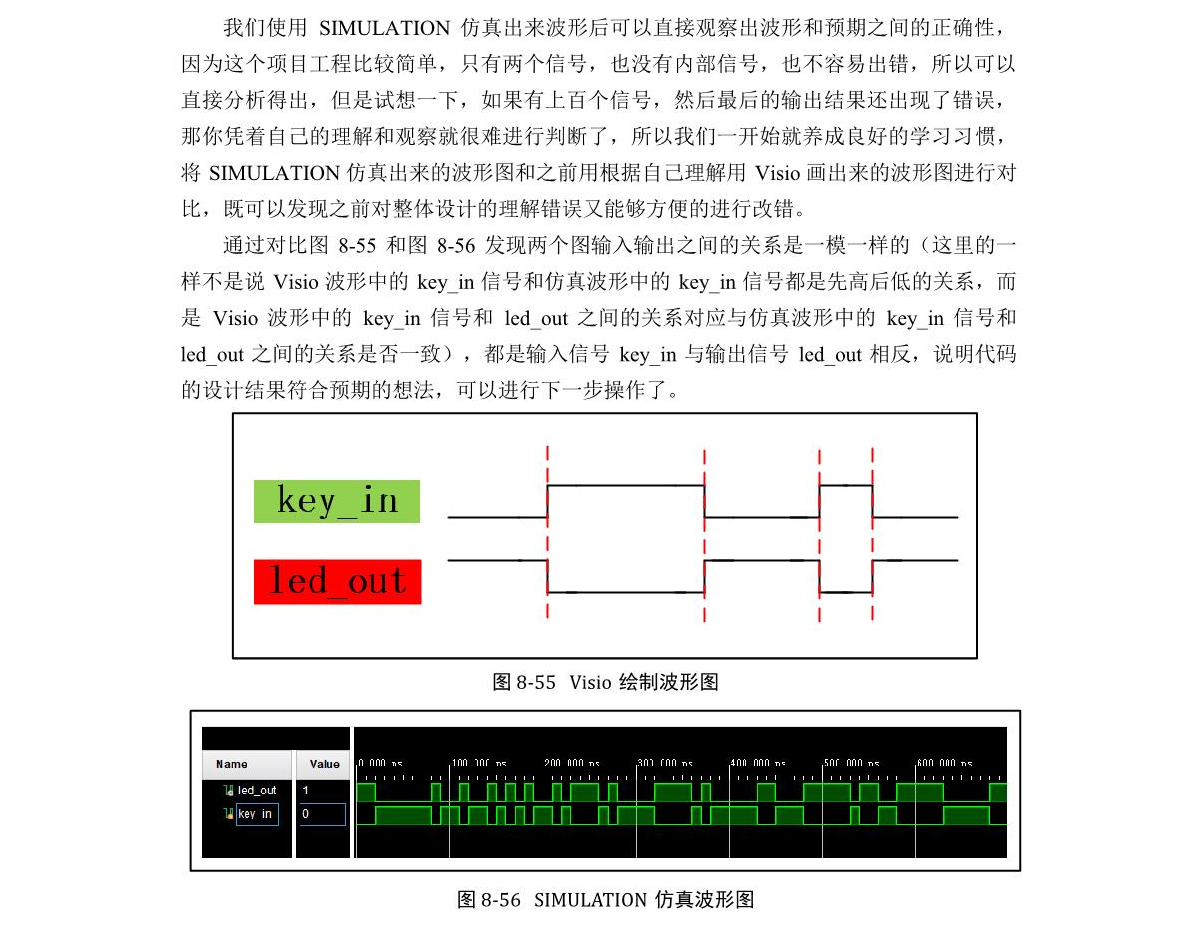

5.打开SIMULATION观察波形

6.仿真波形分析

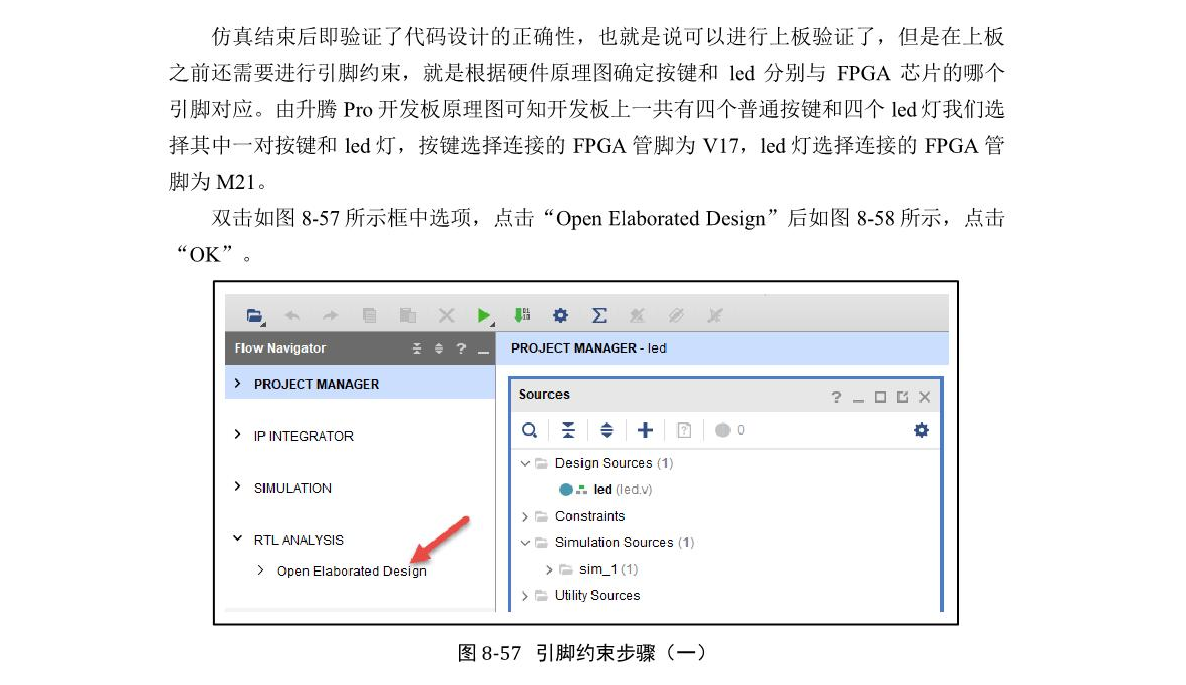

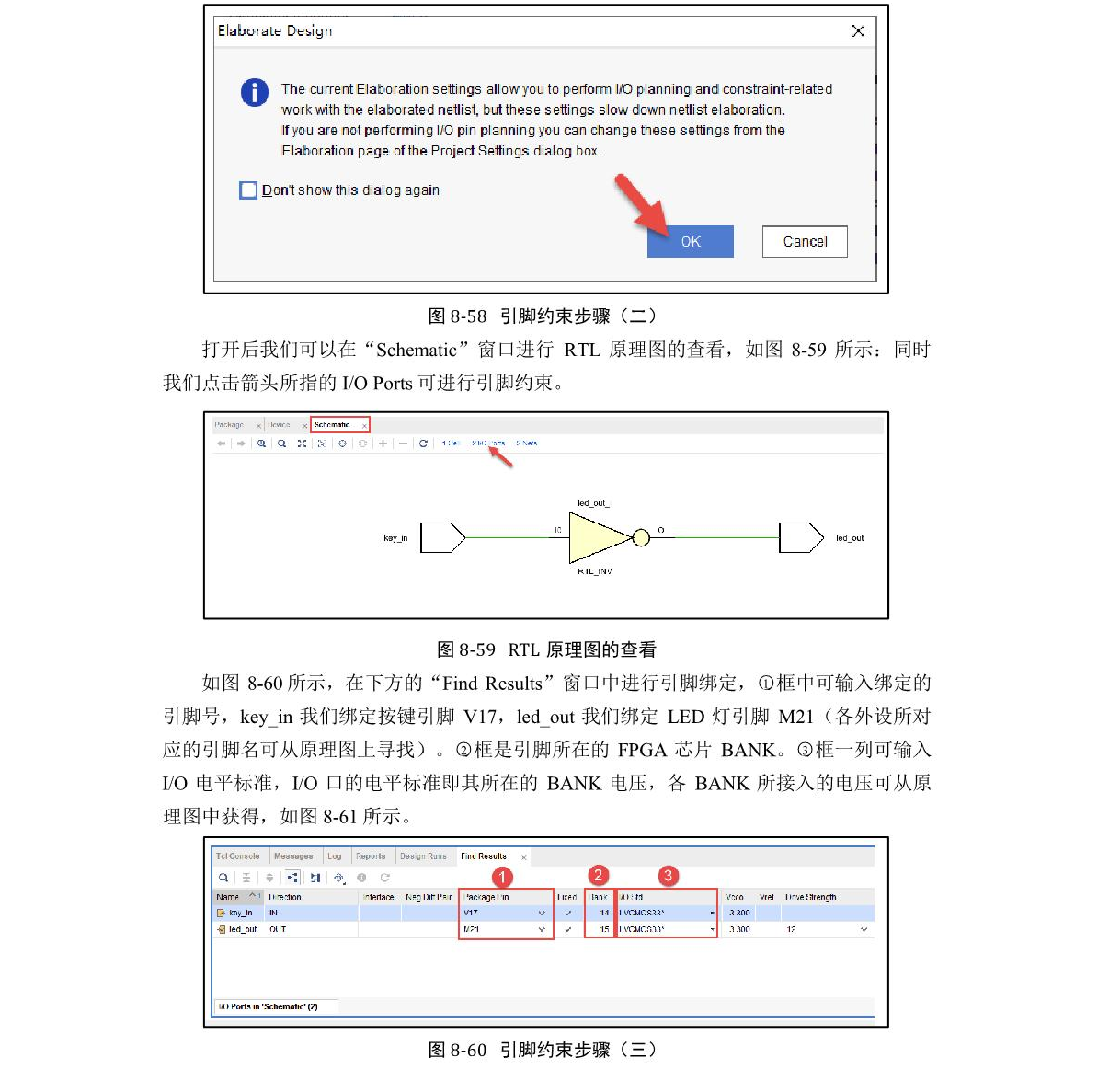

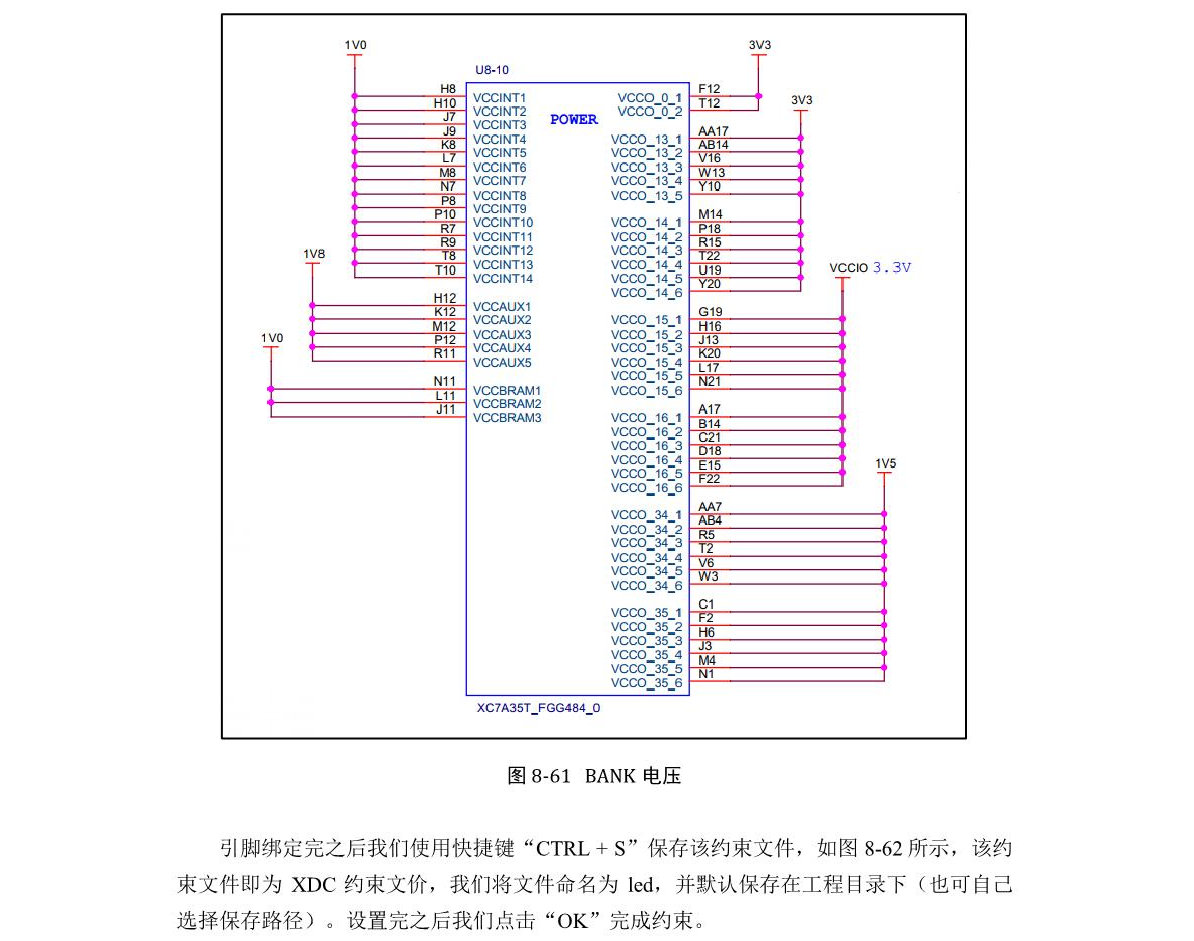

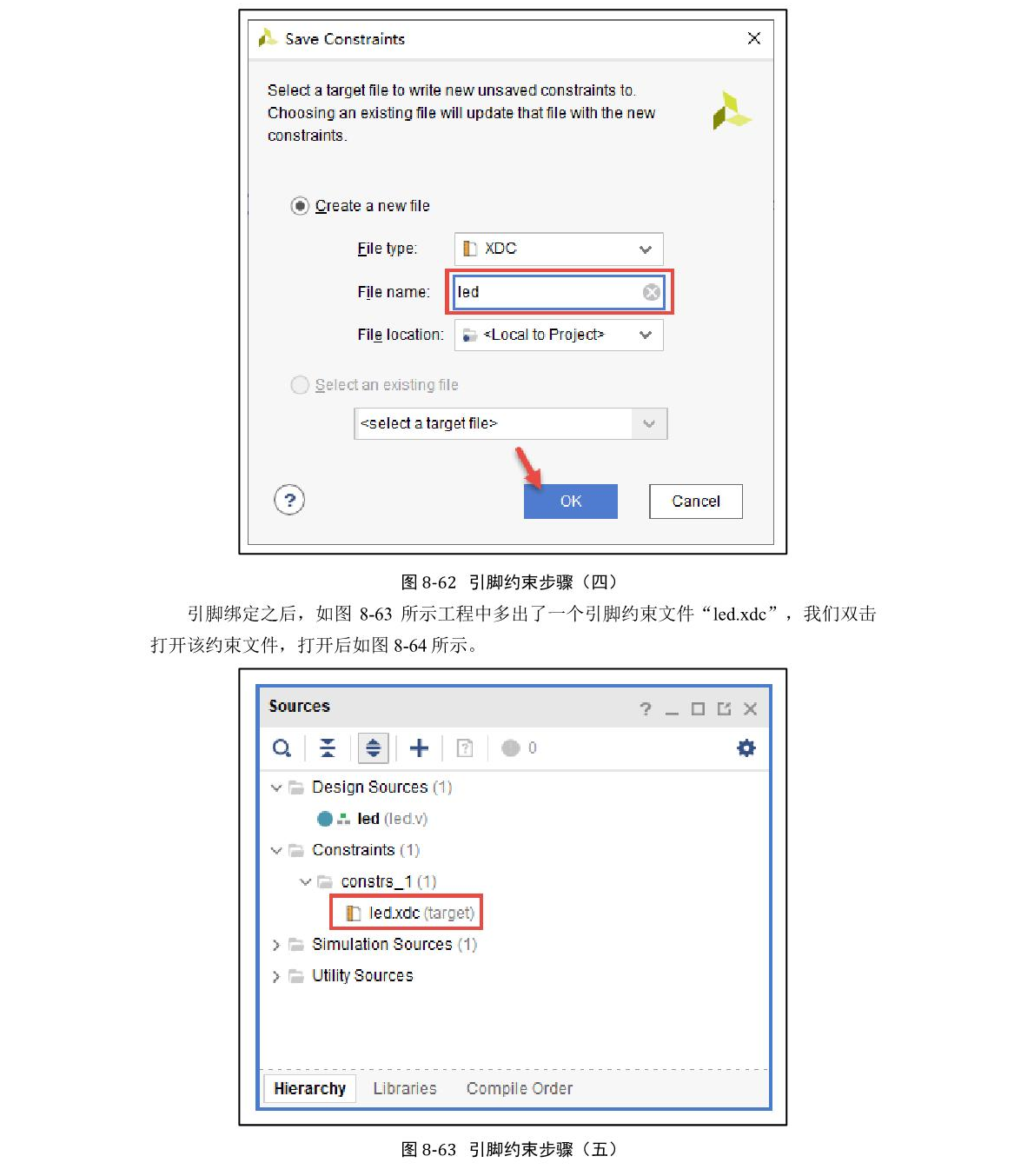

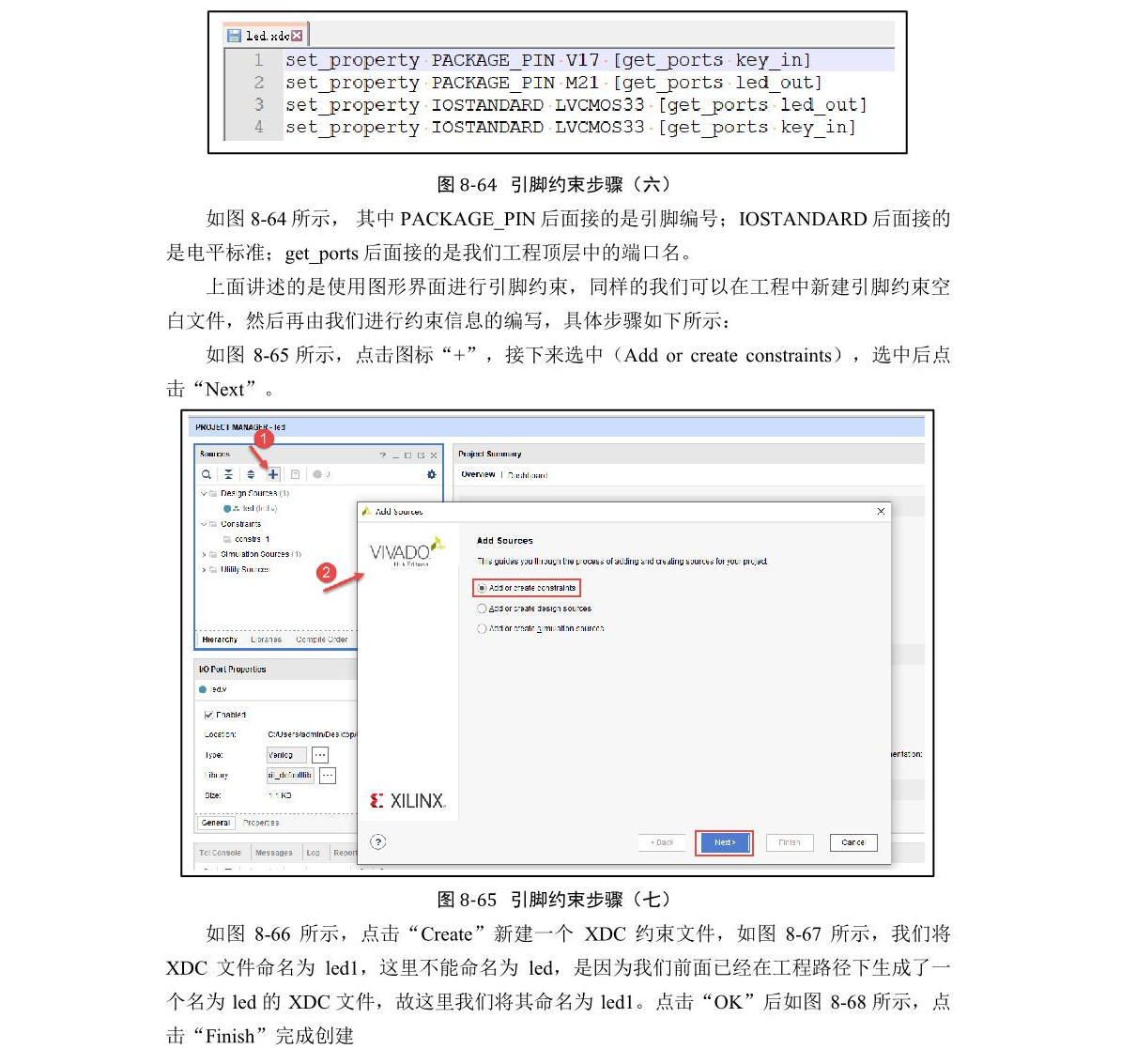

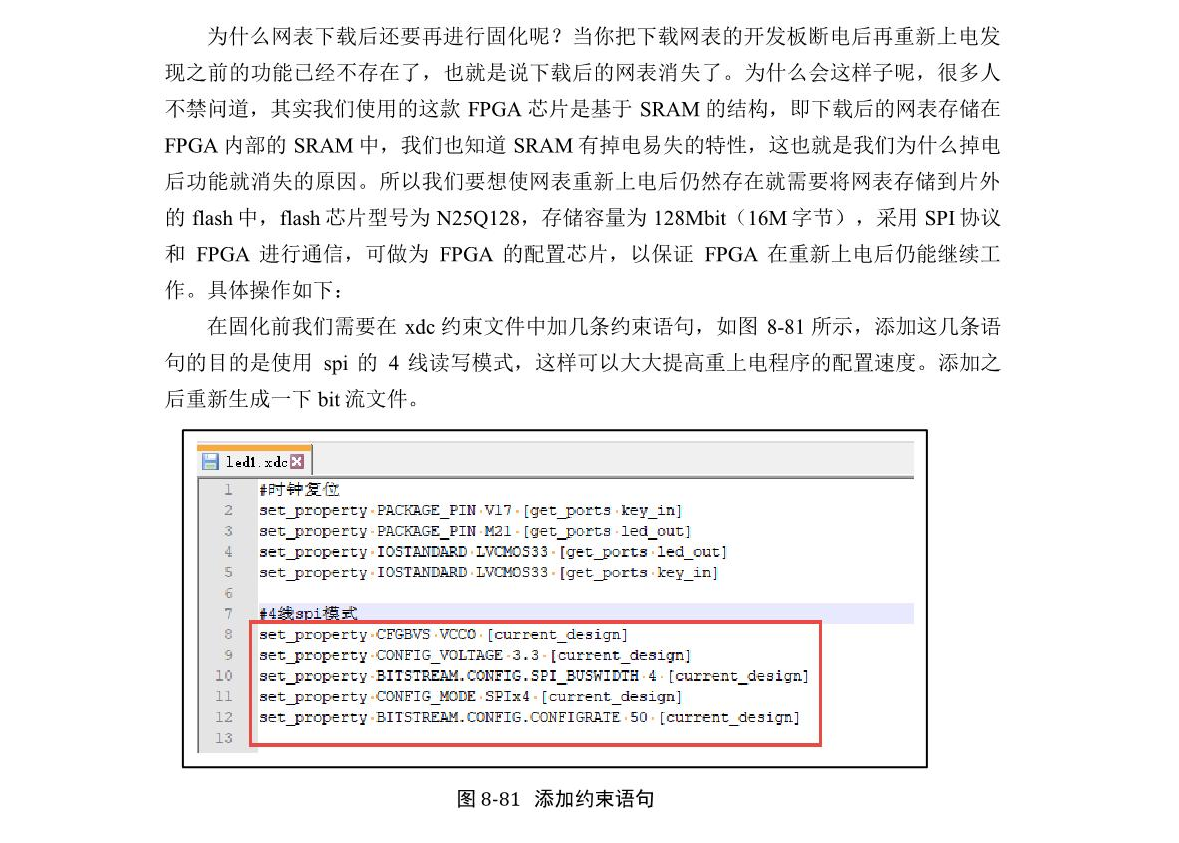

7.引脚约束

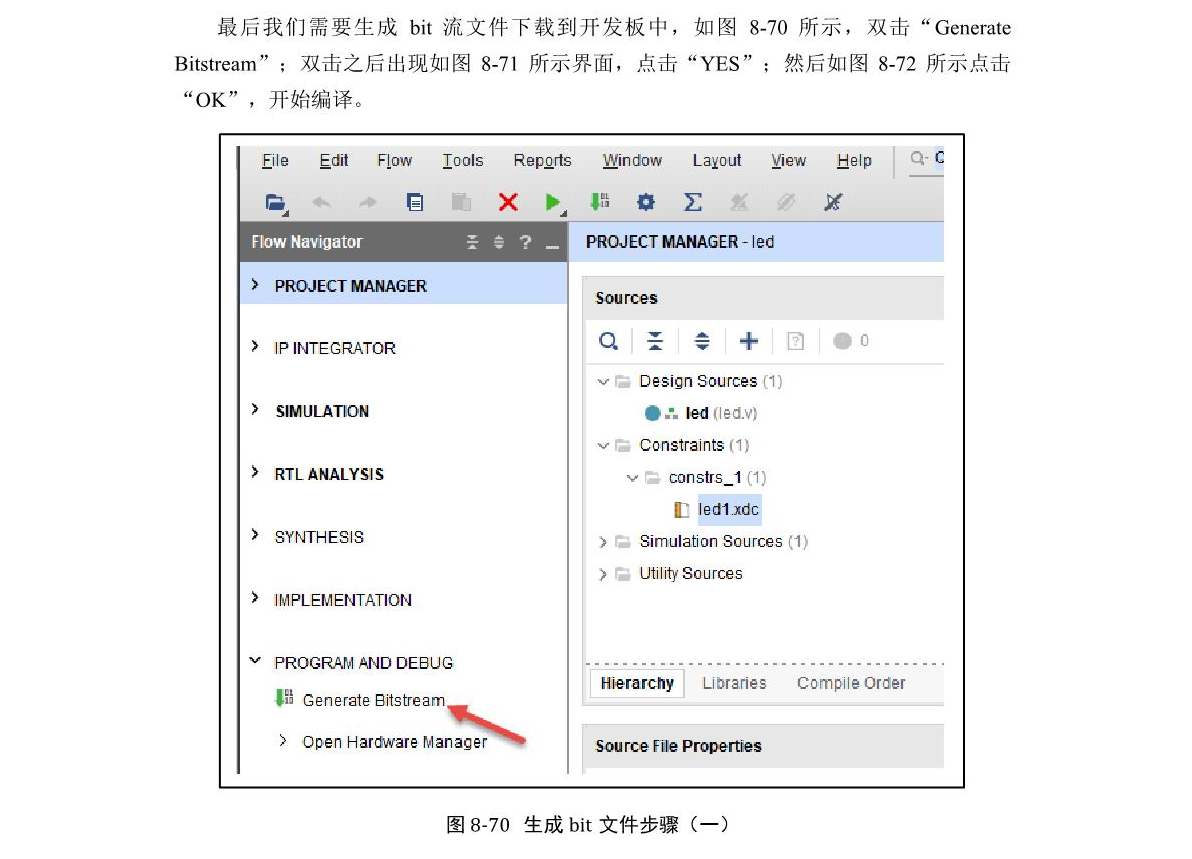

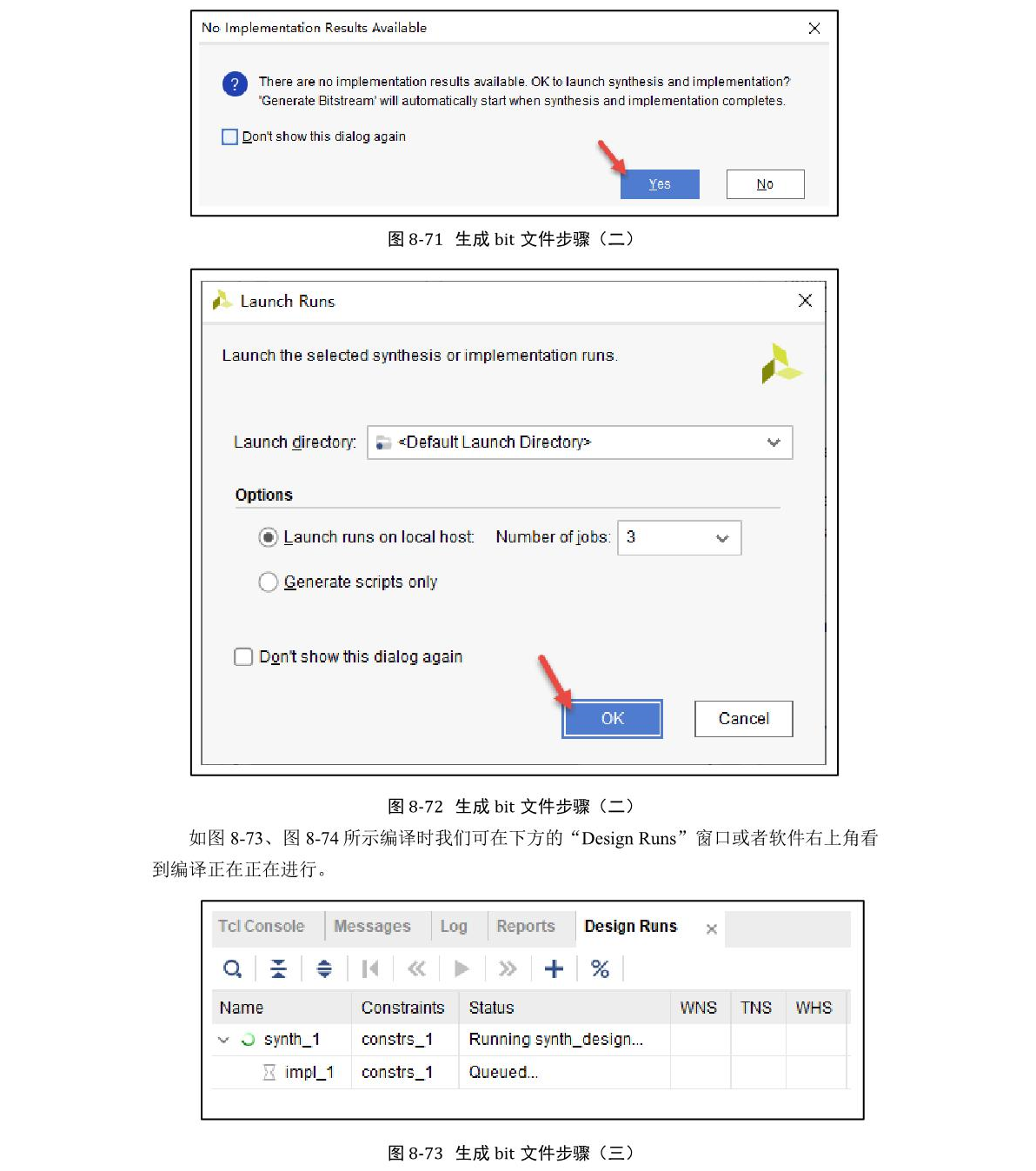

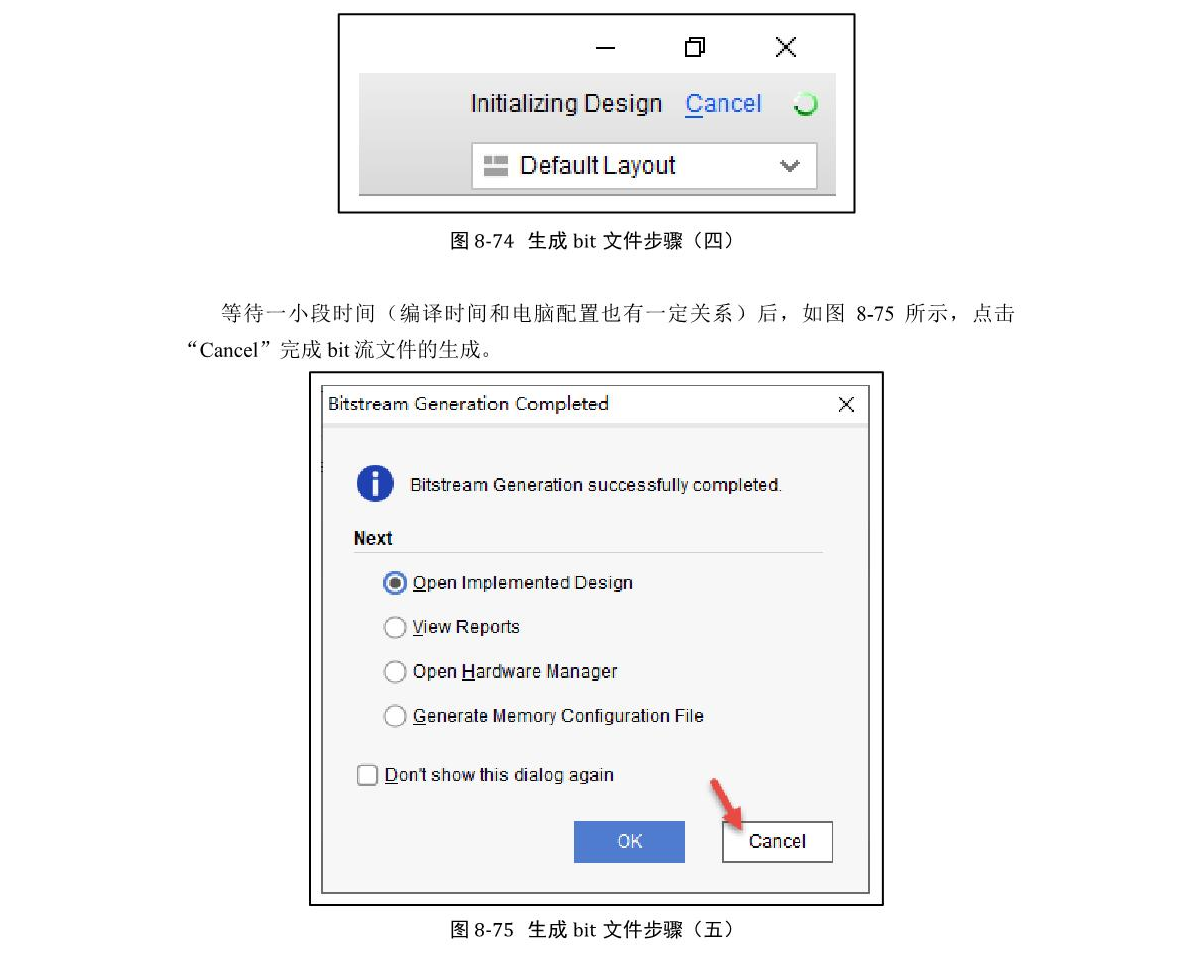

8.生成bit流文件

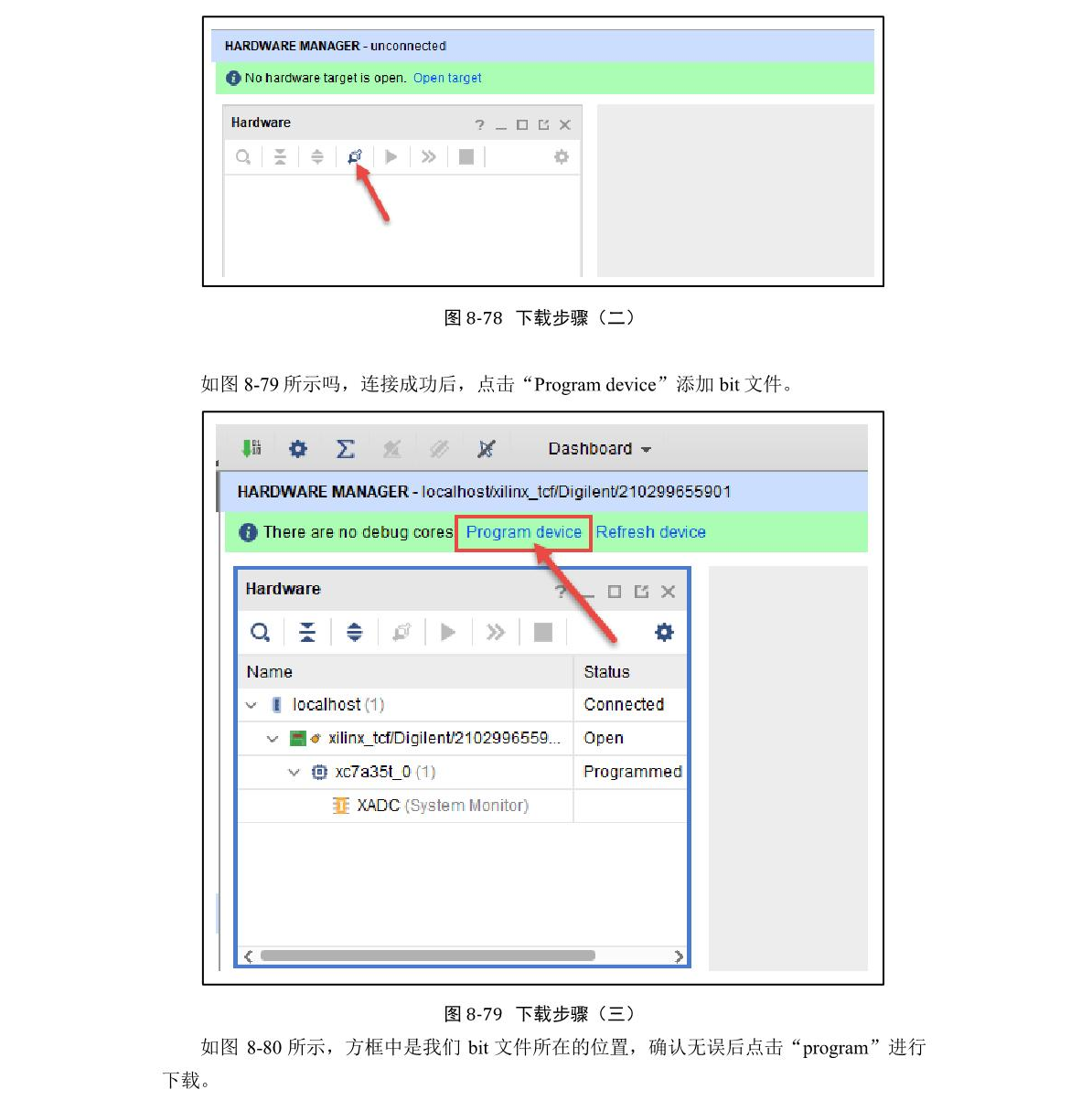

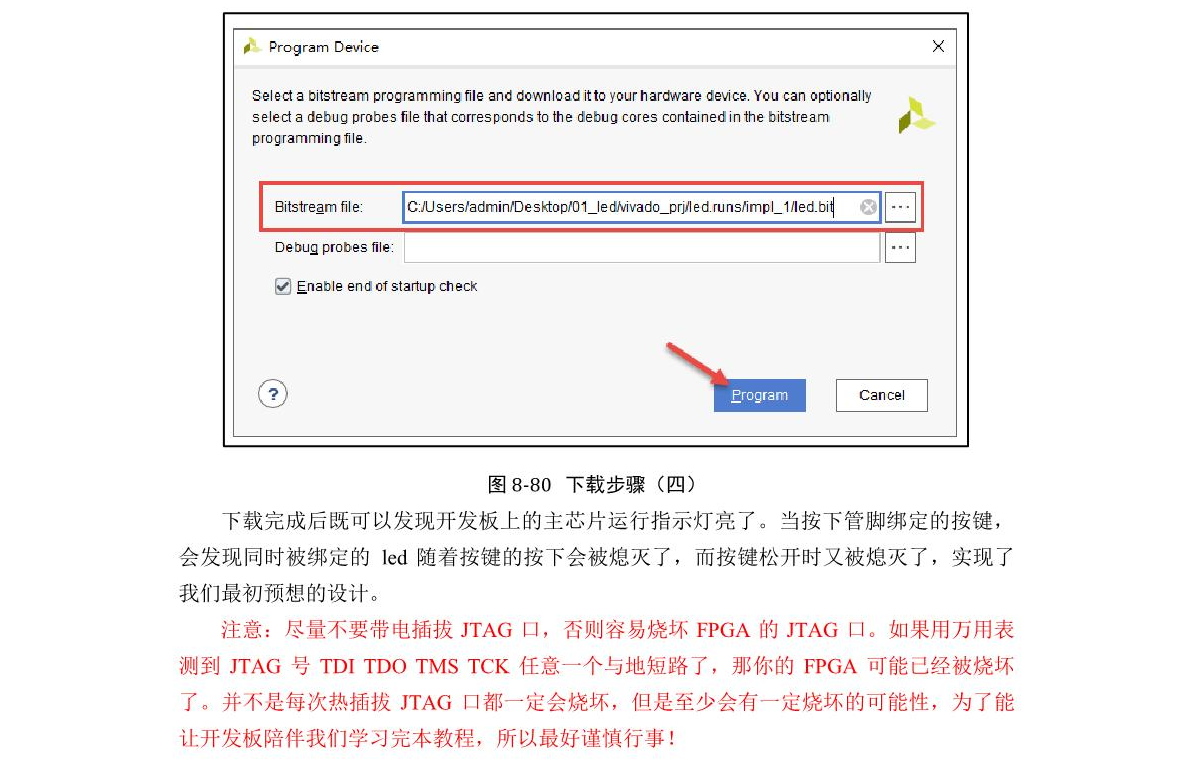

9.通过JTAG将网表下载到开发板

10.程序的固化

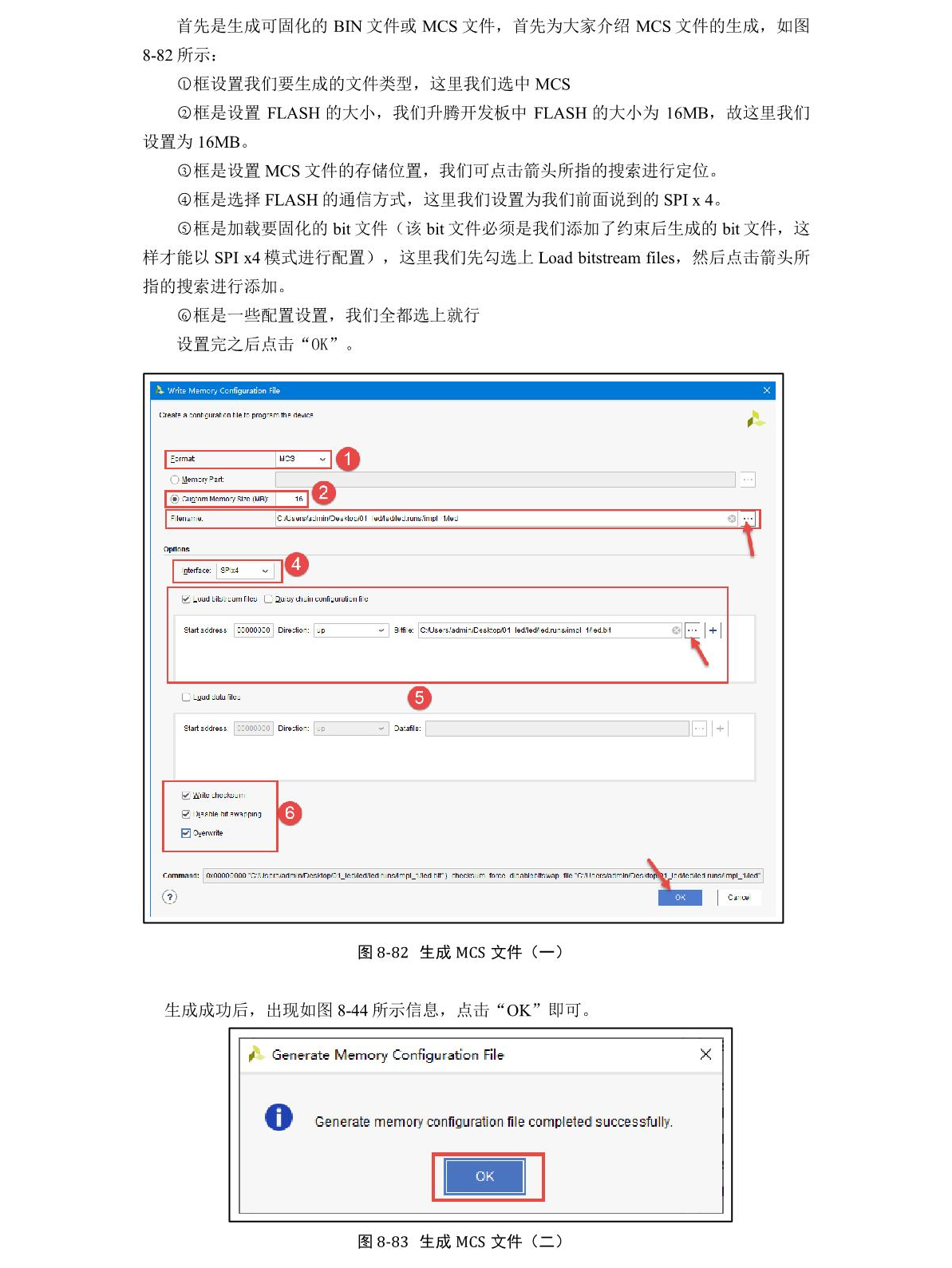

10.1 MCS文件的生成

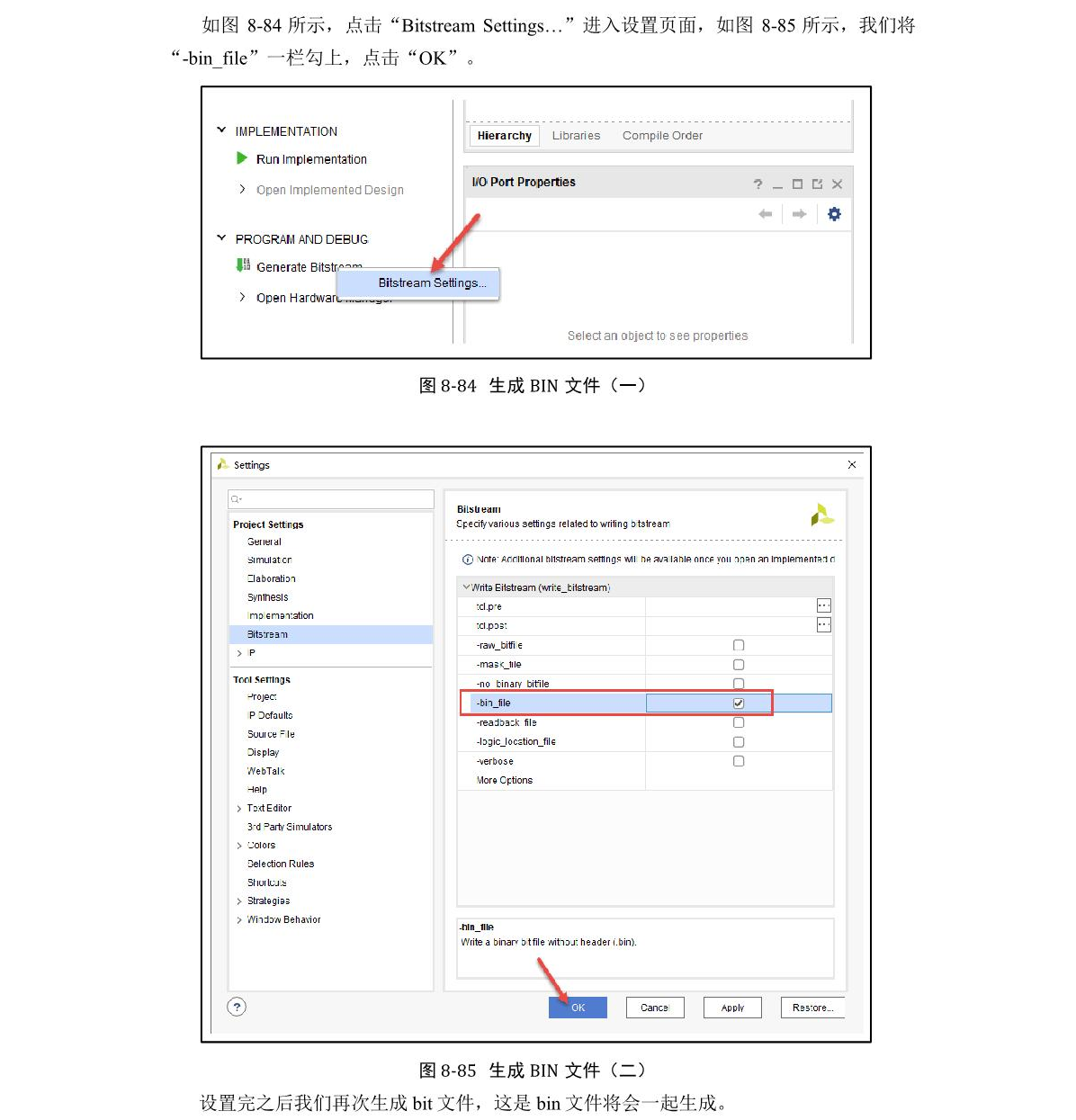

10.2 BIN文件的生成

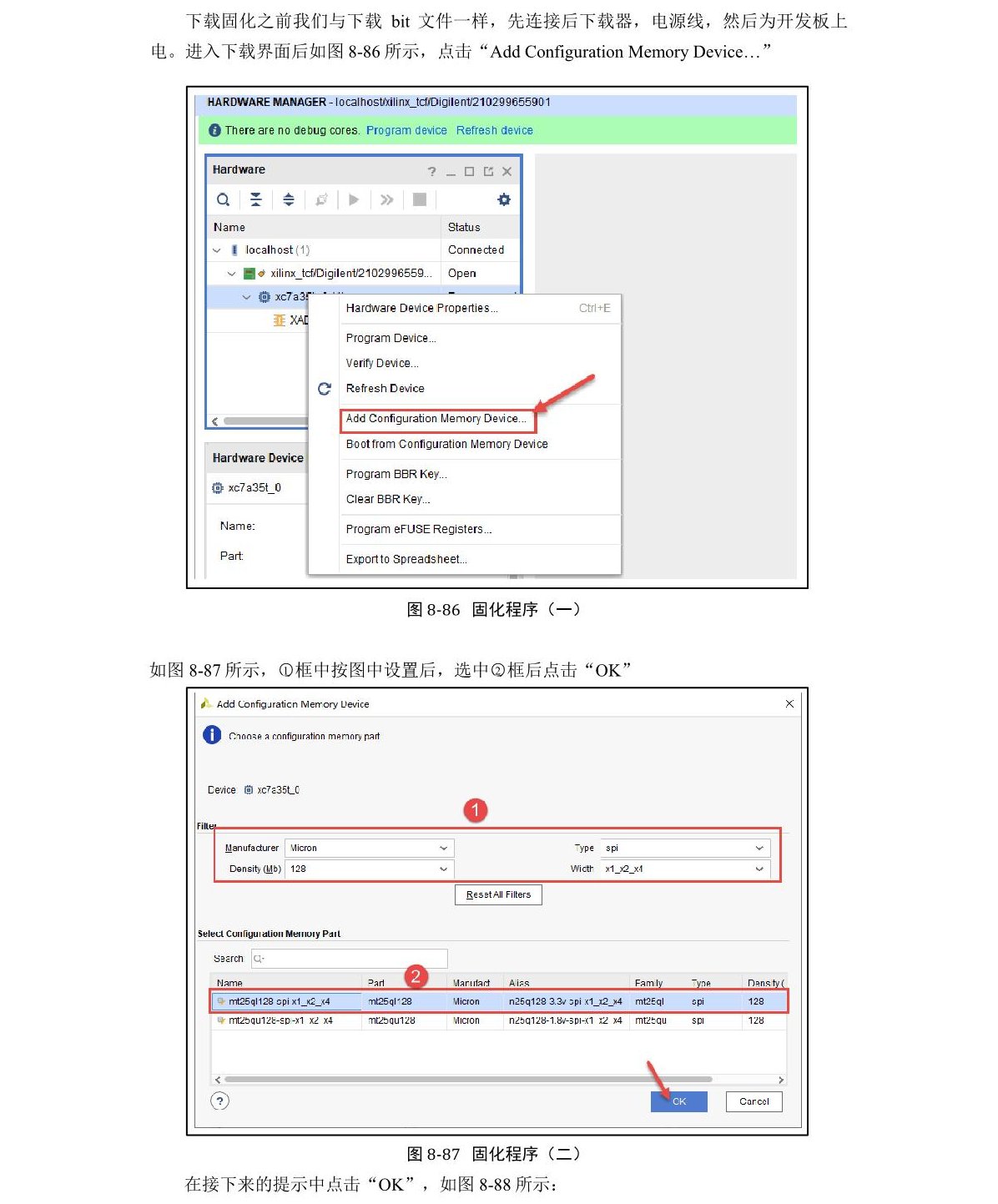

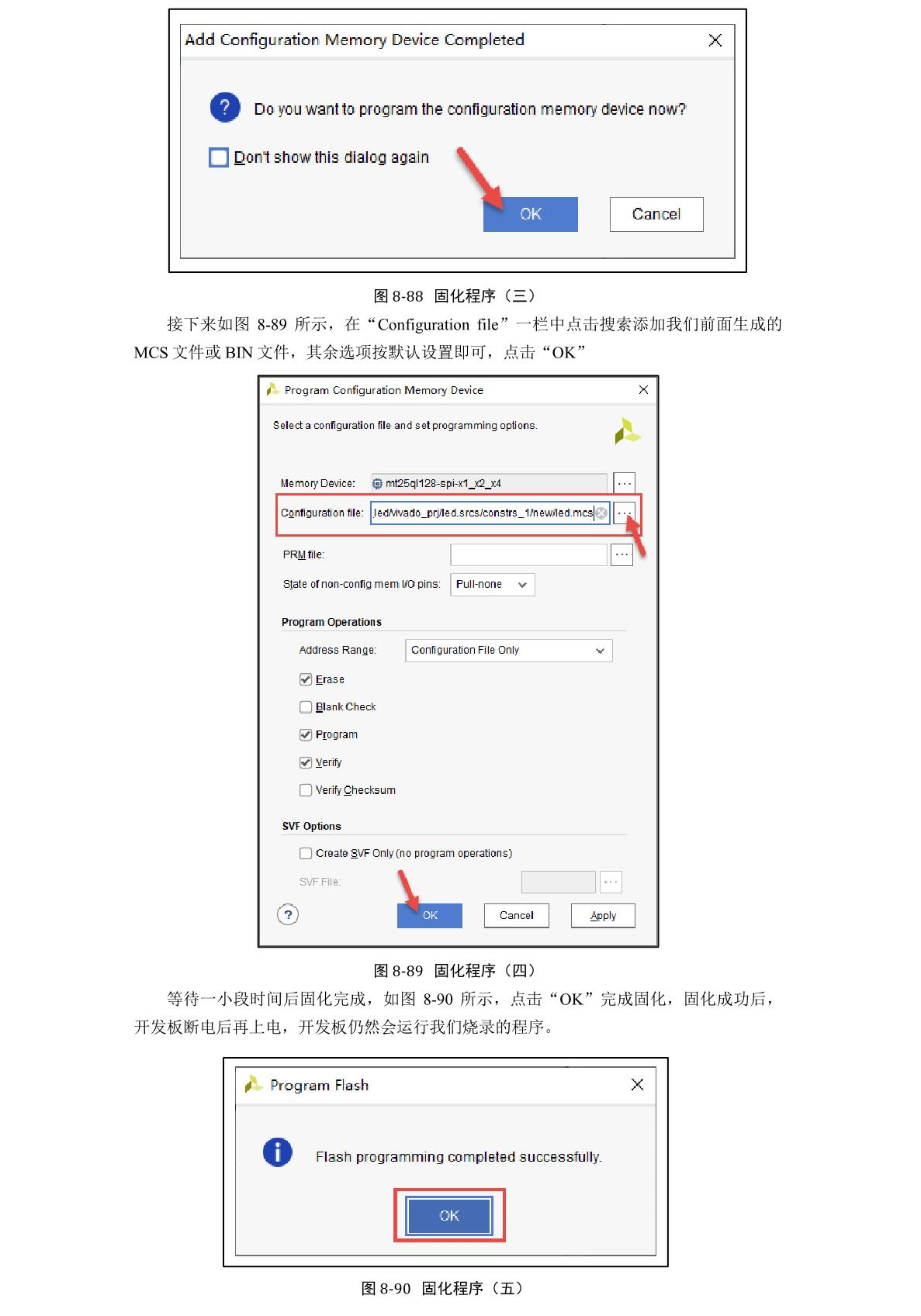

10.3 下载固化文件

参考文献

选自 野火《FPGA Verilog开发实战指南——基于Xilinx Artix7》

本文详细介绍了使用Vivado在XilinxArtix7平台上进行工程新建、RTL代码编写、Testbench设计、波形分析、引脚约束、bit流生成、JTAG下载以及程序固化全过程,是FPGA开发者的实用指南。

本文详细介绍了使用Vivado在XilinxArtix7平台上进行工程新建、RTL代码编写、Testbench设计、波形分析、引脚约束、bit流生成、JTAG下载以及程序固化全过程,是FPGA开发者的实用指南。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?