1.软件版本

MATLAB2019a,ISE14.7

2.本算法理论知识

MPPT,我们采用的是

FPGA的设计结构如下:

这里,

第一,使用MATLAB模拟出光伏设备PV输出的电流和电压数据,尽量贴近实际值

第二,缓冲器这里,我考虑用RAM,双口RAM,因为FIFO的话,没法控制地址,只能先入先出,RAM的话,我可以读取存储器里面任意 为的数据,相当于升级版的FIFO。

3.部分源码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 02:59:07 06/05/2019

// Design Name:

// Module Name: MPPT_module

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module MPPT_module(

i_clk,

i_rst,

i_PV_current,

i_PV_voltage,

o_PV_power,

o_PV_max,

o_PV_current,

o_PV_voltage,

o_state

);

input i_clk;

input i_rst;

input signed[15:0]i_PV_current;

input signed[15:0]i_PV_voltage;

output signed[31:0]o_PV_power;

output signed[31:0]o_PV_max;

output signed[15:0]o_PV_current;

output signed[15:0]o_PV_voltage;

output [1:0]o_state;

//power

multi_core multi_core_u(

.a(i_PV_current), // input [15 : 0] a

.b(i_PV_voltage), // input [15 : 0] b

.p(o_PV_power) // output [31 : 0] p

);

reg signed[31:0]r_PV_k1;

reg signed[31:0]o_PV_max;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

o_PV_max <= 32'd0;

r_PV_k1 <= 32'd0;

end

else begin

r_PV_k1 <= o_PV_power;

if(o_PV_power>o_PV_max)

o_PV_max <= o_PV_power;

else

o_PV_max <= o_PV_max;

end

end

wire signed[31:0]Uk;

wire signed[31:0]Pk;

assign Uk = i_PV_voltage;

assign Pk = o_PV_power;

reg signed[15:0]dU = 16'd1;

reg signed[15:0]dU0= 16'd1;

reg signed[31:0]Pk1;

reg signed[15:0]Uk1;

reg signed[15:0]Uref;

//自适应步长的产生

reg[19:0]cnt;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

cnt <= 20'd0;

end

else begin

if(cnt>=20'd35000)

cnt <= 20'd35000;

else

cnt <= cnt+20'd1;

end

end

reg[1:0]o_state;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

Pk1 <= 32'd0;

Uk1 <= 16'd0;

Uref <= 16'd0;

o_state <= 2'd0;

end

else begin

Pk1 <= Pk;

Uk1 <= Uk;

if(Pk>=Pk1 & Uk>Uk1)

begin

Uref <= Uref + {dU0[15],dU0[15],dU0[15],dU0[15],dU0[15],dU0[15],dU0[15:6]};

o_state <= 2'd0;

end

if(Pk>=Pk1 & Uk<=Uk1)

begin

Uref <= Uref - {dU0[15],dU0[15],dU0[15],dU0[15],dU0[15],dU0[15],dU0[15:6]};

o_state <= 2'd1;

end

if(Pk<Pk1 & Uk>Uk1)

begin

Uref <= Uref - {dU0[15],dU0[15],dU0[15],dU0[15],dU0[15],dU0[15],dU0[15:6]};

o_state <= 2'd2;

end

if(Pk<Pk1 & Uk<=Uk1)

begin

Uref <= Uref + {dU0[15],dU0[15],dU0[15],dU0[15],dU0[15],dU0[15],dU0[15:6]};

o_state <= 2'd3;

end

end

end

assign o_PV_voltage=Uref;

assign o_PV_current=dU0 ;

reg signed[31:0]Power_diffe;

reg signed[7:0] Current_diff;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

dU <= 16'd1;

dU0 <= 16'd1;

Power_diffe <= 32'd0;

Current_diff <= 8'd0;

end

else begin

Power_diffe <= o_PV_max-r_PV_k1;

Current_diff <= i_PV_current[15:8];

if(cnt<20'd4000)

begin

if({Power_diffe[31-4:16-4],4'd0}>16'd10)

dU0<= {16'd16};

else

dU0<= {Power_diffe[31-4:16-4],4'd0};

end

else begin

dU0<= {Power_diffe[31-4:16-4],4'd0};

end

end

end

endmodule

4.仿真分析

可以看到,最大功率pmax会跟踪到每次峰值的最大值

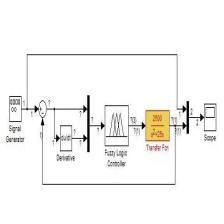

对比MATLAB的仿真结果,就可以得到经典的MPPT性能指标图了,如下所示:

5.参考文献

[1]丁倩. 基于FPGA的MPPT控制技术研究[D]. 西安科技大学.

[1]EB Youssef, P Stephane, E Bruno,等. New P&Amp;O Mppt Algorithm For Fpga Implementation[C]// Conference of the IEEE Industrial Electronics Society. 2010.A02-67

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?