1.定义

设置输入数据端口、输出端口相对于某一个参考时钟的延迟,以达到系统级时序收敛的目的。

之前讨论过,FPGA内部时序路径分为4种:

(1)port-to-port

(2)por-to-reg

(3)reg-to-reg

(4)reg-to-port

set_input_delay、set_output_delay针对的就是port-to-reg、reg-to-port的时序路径的约束,这两种约束也叫做IO约束,另外IO约束也包含了set_max_delay和set_min_delay两种。

例如,输入给FPGA一个数据和一个采样时钟,你需要通过set_input_delay高速时序分析工具,这个采样时钟和数据是一个什么相位关系,FPGA才能根据这个相位关系去分析这条port-to-reg路径。如果没有set_input_delay这个约束,FPGA默认这条路径是没有要求的,也就是requirement无穷大,这是没有意义的,相当于是忽略了这条路径的时序分析,这造成的后果就是ADC你怎么采都不对。举个工程中的例子:

一个外部输入给FPGA的RESET_EXT信号,这个port到内部reg有一条路径,如果没有set_input_delay信号,首先这个路径会出现在Unconstrained Paths里:

其次,这条路径的Requirement是无穷:

如果此时约束一下:

set_input_delay -clock [get_clocks TS_CLK] -max 1.200 [get_ports RESET_EXT]

路径就会分析如下:

可以发现多出来一行Input Delay,slack也不是∞了,而且这个设置的input delay数值,体现在了数据路径中:

这也就引出了input delay值的一个意义:max_value是接口端发起沿(launch edge)到有效数据窗口开始时刻的延迟,min_value是接口端发起沿(launch edge)到有效数据窗口结束时刻的延迟。(这里发起沿特别加了个接口端,意思就是把FPGA输入端口当成时序路径的起点来进行分析)

set_output_delay相反,是为了保证输出端口信号与一个参考时钟的相位关系,而做出的约束,让端口输出的信号和时钟相位关系按照我们设计的来,与上个例子中的工程一样,有个输出端口SIM_DONE,设置output delay如下:

set_output_delay -max 1.3 -clock [get_clocks TS_CLK] [get_ports SIM_DONE]

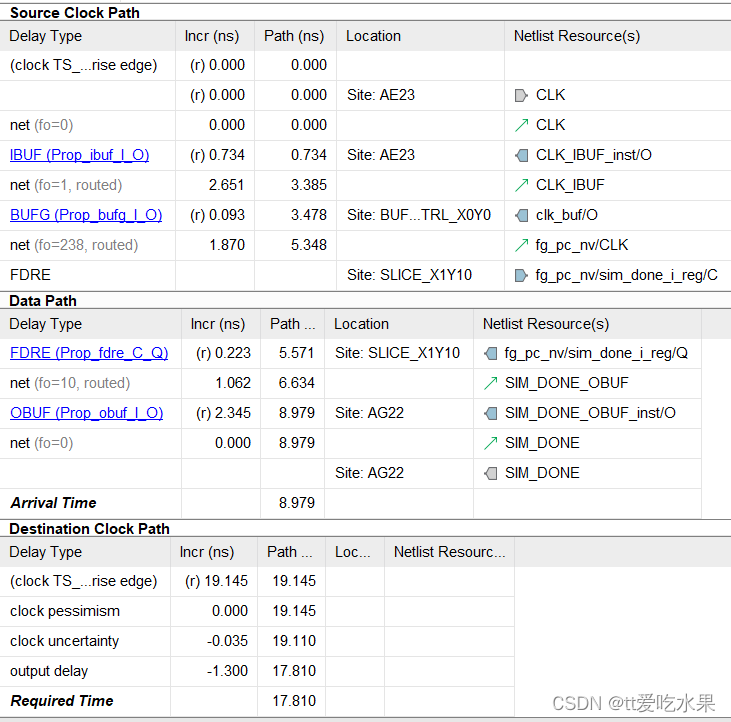

路径如下:

可以看出,这个output delay值算到了Destination Clock Path,这也引出了output delay的一个意义:max_delay是数据有效窗口开始时刻到接口端捕获沿延迟,min_delay是数据有效窗口结束时刻到接口端捕获沿延迟。(这里发起沿特别加了个接口端,意思就是把FPGA输出端口当成时序路径的终点来进行分析)

再总结一下,set_input_delay就是根据实际情况,让FPGA知道数据和时钟相位关系是什么样的。set_output_delay就是告诉FPGA,我想让你输出什么样的数据和时钟相位关系。

2.语法

常用语法如下:

set_input_delay -clock [get_clocks **] -max/-min [get_ports **] delay_value

set_output_delay -clock [get_clocks **] -max/-min [get_ports **] delay_value

其他选项有很多,可以在vivado tcl console中输入help set_input_delay查看

3.delay_value如何确定

最重要的就是这个延迟值如何获取。分两种情况,系统同步接口和源同步接口。

系统同步:上下游期间使用同一个时钟,也就是FPGA用的时钟和产生这个数据的源头的芯片使用的时钟一致,像下图这样的就是系统同步:

源同步:数据跟着时钟一起输入给FPGA。(两种接口的网上资料很多,可自行查)。像这样的就是源同步:

以上图中上游器件不一定是FPGA。

(1)input_delay_value

a. 系统同步

系统同步中比较好理解,发起沿到有效数据沿之间的延迟,由于是系统同步,一般时钟到各个芯片会做等长处理,所以忽略时钟到各个芯片的skew,同时相比于上游芯片到FPGA输入端的trace delay和时钟到各芯片的delay,也忽略上有芯片时钟输入端口到寄存器clk端的延迟,所以可以很容易的得到:

input_delay_value = Tco + Ttrace

所以可以得到:

input_delay_value_min = Tco_min + Ttrace_min

input_delay_value_max = Tco_max + Ttrace_max

其中Tco是上游时序器件内部传输延迟,这个一般都可以查到,Ttrace就是上游器件到FPGA输入端口的延迟,这个在PCB参数中也可以获得。如果是DDR传输,就是上升沿和下降沿都发数的话,Tco就又可以分为Trco和Tfco来区分上游器件上升沿和下降沿分别对应的传输延迟,这里需要注意的是,约束发起沿为下降沿的时候需要加上-clock_fall和-add_delay,-clock_fall可以理解,相对于时钟的下降沿来约束这个port,-add_delay是为了保留之前的上升沿的约束,在此基础上加一个下降沿的约束。

b. 源同步

对于源同步接口,这里又分为以下几种情况:中心对齐,边沿对齐,SDR,DDR。因为vivado的language Templates中都有详细的计算公式,具体打开方式是

点Flow Navigator中的Project Manager中的language,在搜索框中输入input delay,在XDC目录中就会看到上图中的显示内容。右侧会出现这种情况下的port端时钟与数据的对应时序图,地下会有约束的具体语句,按照你输入的端口类型进行对号入座就可以了。这里就说明一点,这个计算过程就是按照我上面所说的,input delay值的一个意义:max_value是接口端发起沿(launch edge)到有效数据窗口开始时刻的延迟,min_value是接口端发起沿(launch edge)到有效数据窗口结束时刻的延迟,来进行计算的。

另外再说明一下,图中的这些参数,例如dv_bre等,都是可以从上游芯片的手册中找到的,比如你上游是一个ADC,那么它输出数据和随路时钟的相位关系它必须体现在芯片手册中。

(2)output_delay_value

a. 系统同步

根据之前的定义,output_delay_value是在端口上,捕获沿之前的数据窗口长度,所以在保证图中下游器件reg2的建立时间满足的情况下,output_delay_value_max = Ttrace_max + Tsu,为了保证reg2的保持时间满足,output_delay_value_min = Ttrace_min - Thd,vivado官方的language templates里也有相同的说明:

b. 源同步

源同步的output_delay有两种设置方式,一种是skew,也就是已知数据采样沿前后数据的skew,如下图所示:

另一种是已经下游器件的Tsu和Thd:

vivado的language template中的计算都是和以上定义相符的,大家可以自行查看。另外DDR接口的设置也是同样的道理。

4.总结

所以理解set_input_delay和set_output_delay的关键还是理解其实际意义,也可以说是定义:

input_delay:max_value是接口端发起沿(launch edge)到有效数据窗口开始时刻的延迟,min_value是接口端发起沿(launch edge)到有效数据窗口结束时刻的延迟

output_delay:max_delay是数据有效窗口开始时刻到接口端捕获沿延迟,min_delay是数据有效窗口结束时刻到接口端捕获沿延迟

这里的接口端发起沿和接口端捕获沿都是FPGA port约束参考的时钟沿,一般就是输入给FPGA port的或从port输出的时钟。

1547

1547

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?