转自:https://blog.csdn.net/zhouml_msn/article/details/105056034

一、电源线

宽度:最大工作电流要求宽度 X 3倍

以树枝状铺开, 不要环状铺开

压降: 宽度\长度\温度三个要素, 有计算工具.

二、地线

模、数单独接地

路线:无限循环。以减少不同地的压差

三、信号线

3W原则: 线中至线中3倍线宽

50mil以上距离平行电源线

3种元件远离:晶振、电感、电磁

上下层垂直

四、晶振

失败案例:

线宽 > 8mil, 越宽越好

线长 尽量相等,频率越高越重要;

和芯片同层尽靠,

远离电感、电磁;

电容布在芯片、晶振之间;

底面不布线,底面不布线,底面不布线,干扰大!

电路底层挖穿1到2层, 不履铜,不履地,因为:1_防寄生电容(相近的层状金属层寄生电容大, 2_防热传递致偏频。

电路用粗地线包围,导线也被包围,且地线多打过孔。

- 晶振:晶振周围要包地,有条件打一圈地过孔。晶振不能离板边过近,注意应力要求。敏感信号远离晶振,内层走线也要避开晶振投影区域。

贴一个网上的正确示例:

晶振电路的PCB设计

位置要选对:晶振内部是石英晶体,如果不慎掉落或受不明撞击,石英晶体易断裂破损,所以晶振的放置远离板边,靠近MCU的位置布局。

两靠近:耦合电容应尽量靠近晶振的电源管脚,如果多个耦合电容,按照电源流入方向,依次容值从大到小摆放;晶振则要尽量的靠近MCU。

走线短:所有连接晶振输入/输出端的导线尽量短,以减少噪声干扰及分布电容对晶振的影响。

高独立:尽可能保证晶振周围的没有其他元件。防止器件之间的互相干扰,影响时钟和其他信号的质量。晶振周围 1mm 禁布器件,0.5mm 禁布过孔走线,所有晶振下不打过孔(包括地过孔)。

外壳要接地:晶振的外壳必须要接地,除了防止晶振向外辐射,也可以屏蔽外来的干扰。

www.21micro-grid.com

原理图设计要点:

(1)、晶振电源去耦非常重要,建议加磁珠,去耦电容选两到三个,容值递减。

(2)、时钟输出管脚加匹配,具体匹配阻值,可根据测试结果而定。

(3)、预留的电容C1,容值要小,构成了一级低通滤波,电阻、电容的选择,根据具体测试结果而定。

PCB设计要点:

(1)、在PCB设计是,晶振的外壳必须接地,可以防止晶振的向往辐射,也可以屏蔽外来的干扰。

(2)、晶振下面要铺地,可以防止干扰其他层。因为有些人在布多层板的时候,顶层和底层不铺地,但是建议晶振所在那一块铺上地。

(3)、晶振底下不要布线,周围5mm的范围内不要布线和其他元器件(有的书是建议300mil范围内,大家可以参考),主要是防止晶振干扰其他布线和器件。

(4)、晶振不要布在板子的边缘,因为为了安全考虑,板卡的地和金属外壳或者机械结构常常是连在一起的,这个地我们暂且叫做参考接地板,如果晶振布在板卡的边缘,晶振与参考接地板会形成电场分布,而板卡的边缘常常是有很多线缆,当线缆穿过晶振和参考接地板的电场是,线缆被干扰了。而晶振布在离边缘远的地方,晶振与参考接地板的电场分布被PCB板的GND分割了,分布到参考接地板电场大大减小了。

(5)、当然时钟线尽量要短。如果你不想让时钟线走一路干扰一路,那就布短吧。还有一点,关于晶振的选择,如果你的系统能工作在25M,就尽量不要选50M的晶振。时钟频率高,是高速电路,时钟上升沿陡也是高速电路,需要考虑信号完整性。

补充:

1、晶振下方不要走线,晶振出线包地,走线过程不能隔断,不要过孔换层;

2、晶振引出的两根时钟线也要短,防止形成发射天线;

3、晶振输出脚串电阻,加22或33PF等滤波电容, 电容到地路径要短;

4、可以使用扩频、展频等手段,但需要硬件支持,同时也可能会影响高速信号质量;

5、屏蔽晶振,金属外壳检查接地,必要时可贴吸波材料进行防护。

原文链接:https://blog.csdn.net/weixin_39534759/article/details/112146212

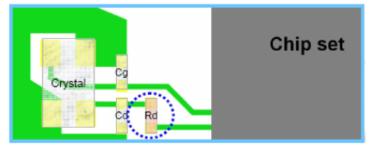

01 晶体振荡单元(无源晶振)的布线规则

1、振荡电路(振荡单元、振荡电容)应配置在振荡IC附近;

2、晶振电路下面的各层都需要铺地,不能放置器件和走线,尤其是高频信号线路;

3、晶振电路做包地处理时需要打大量地孔,否则包地无意义;

4、四脚晶振,建议晶振走线从内部走,减小晶振的环路,如下图所示。

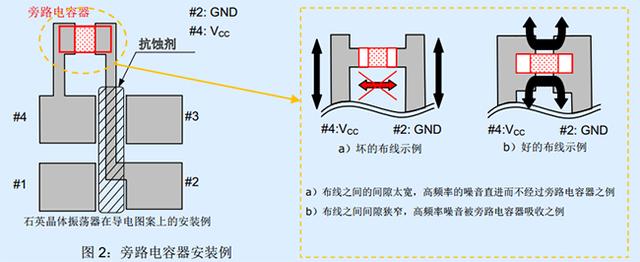

02 石英晶体振荡器(有源晶振)的布线规则

1、振荡电路(振荡单元、振荡电容)应配置在振荡IC附近;

2、晶振电路下面的各层都需要铺地,不能放置器件和走线,尤其是高频信号线路;

3、晶振电路做包地处理时需要打大量地孔,否则包地无意义;

4、电源先经过旁路电容,然后再进入晶振,如下图所示(高频噪声通常直线前进)。

晶振起振的可靠性

单片机晶振不起振是常见现象,那么引起晶振不起振的原因有哪些呢?如何解决?

01 晶振不起振的原因

1、PCB布线错误,现在的PCB不再是单一功能电路(数字或模拟电路),而是由数字电路和模拟电路混合组成的。因此,PCB布线的时候可能出现问题导致晶振不起振;

2、单片机或晶振的质量问题;

3、负载二极管或匹配电容与晶振不匹配或者电容质量有问题;

4、PCB板受潮,导致阻抗失配而不能起振;

5、晶振电路的走线过长或两脚之间有走线导致晶振不起振,通常我们在PCB布线时晶振电路的走线应尽量短且尽可能靠近振荡器,严禁在晶振两脚间走线;

6、晶振受外围电路的影响而不起振。

02 晶振不起振的解决方案

1、排除电路错误的可能性,因此你可以用相应型号单片机的推荐电路进行比较。

2、排除外围元件不良的可能性,因为外围零件无非为电阻,电容,你很容易鉴别是否为良品。

3、排除晶振为停振品的可能性,因为你不会只试了一二个晶振。

4、试着改换晶体两端的电容,也许晶振就能起振了,电容的大小请参考晶振的使用说明。

5、在 PCB 布线时晶振电路的走线应尽量短且尽可能靠近 IC,杜绝在晶振两脚间走线。

(图文内容由快点PCB整理自网络)

相关资源:40个单片机晶振问题及解决方法小结

————————————————

原文链接:https://blog.csdn.net/weixin_39622521/article/details/112223228

PCB上晶振布局很难?5分钟教你掌握!

问题描述

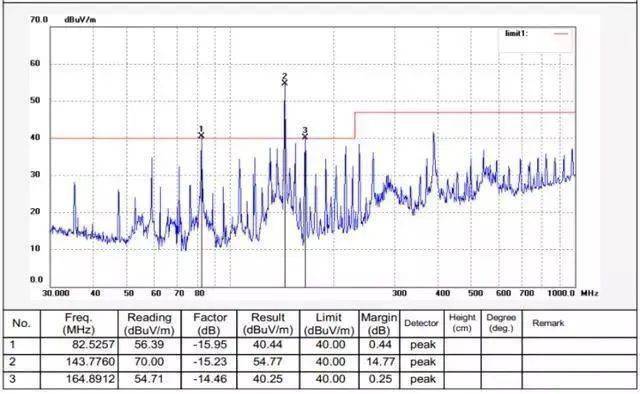

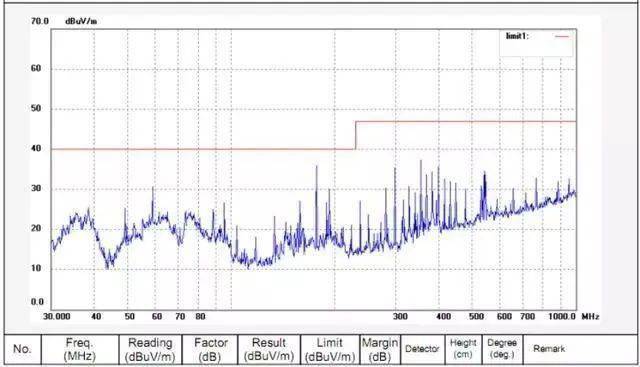

某行车记录仪,测试的时候要加一个外接适配器,在机器上电运行测试时发现超标,具体频点是84MHZ、144MH、168MHZ,需要分析其辐射超标产生的原因,并给出相应的对策。辐射测试数据如下:

2 辐射源头分析

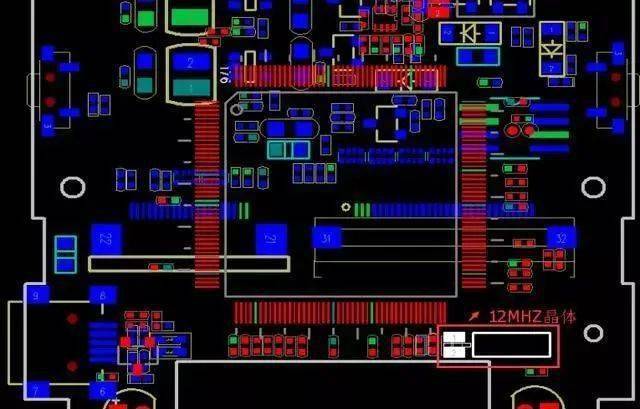

该产品只有一块PCB,其上有一个12MHZ的晶体。其中超标频点恰好都是12MHZ的倍频,而分析该机器容易EMI辐射超标的屏和摄像头,发现LCD-CLK是33MHZ,而摄像头MCLK是24MHZ;

通过排除发现去掉摄像头后,超标点依然存在,而通过屏蔽12MZH晶体,超标点有降低,由此判断144MHZ超标点与晶体有关,PCB布局如下:

3 辐射产生的原理

从PCB布局可以看出,12MHZ的晶体正好布置在了PCB边缘,当产品放置与辐射发射的测试环境中时,被测产品的高速器件与实验室中参考接地会形成一定的容性耦合,产生寄生电容,导致出现共模辐射,寄生电容越大,共模辐射越强;

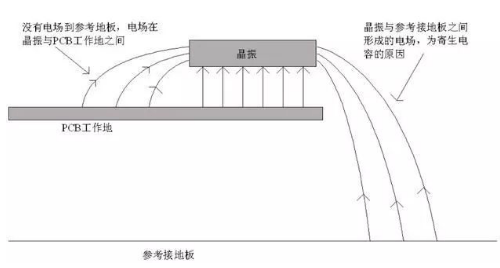

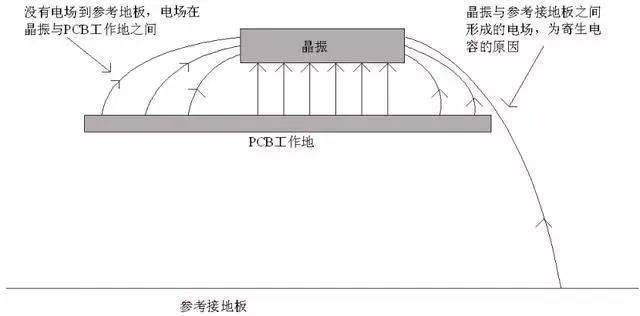

而寄生电容实质就是晶体与参考地之间的电场分布,当两者之间电压恒定时,两者之间电场分布越多,两者之间电场强度就越大,寄生电容也会越大,晶体在PCB边缘与在PCB中间时电场分布如下:

(PCB边缘的晶振与参考接地板之间的电场分布示意图)

(PCB中间的晶振与参考接地板之间的电场分布示意图)

从图中可以看出,当晶振布置在PCB中间,或离PCB边缘较远时,由于PCB中工作地(GND)平面的存在,使大部分的电场控制在晶振与工作地之间,即在PCB内部,分布到参考接地板去的电场大大减小,导致辐射发射就降低了。

4 处理措施

将晶振内移,使其离PCB边缘至少1cm以上的距离,并在PCB表层离晶振1cm的范围内敷铜,同时把表层的铜通过过孔与PCB地平面相连。经过修改后的测试结果频谱图如下,从图可以看出,辐射发射有了明显改善。

5 思考与启示

高速的印制线或器件与参考接地板之间的容性耦合,会产生EMI问题,敏感印制线或器件布置在PCB边缘会产生抗扰度问题。

如果设计中由于其他一些原因一定要布置在PCB边缘,那么可以在印制线边上再布一根工作地线,并多增加过孔将此工作地线与工作地平面相连

246

246

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?