文章目录

概述

笔者曾在ise14.7环境下使用spartan6系列FPGA,通过时序逻辑控制传感器18B20进行测温,因项目研制需要,现将该功能模块移植到ZYNQ系列FPGA平台上,在使用VIVADO开发环境调用原时序逻辑过程中出现了很多问题,笔者最终将问题解决,为此笔者对inout类型端口,在两种开发环境下的应用进行了总结,为后续开发者提供相关开发经验。

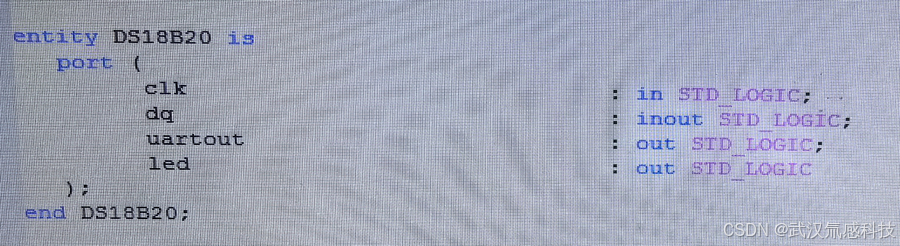

一、se14.7环境下使用inout端口

ise14.7环境下可以直接定义inout端口,并按照inout端口三态的方式编写相关代码,部分软件代码如图一所示。

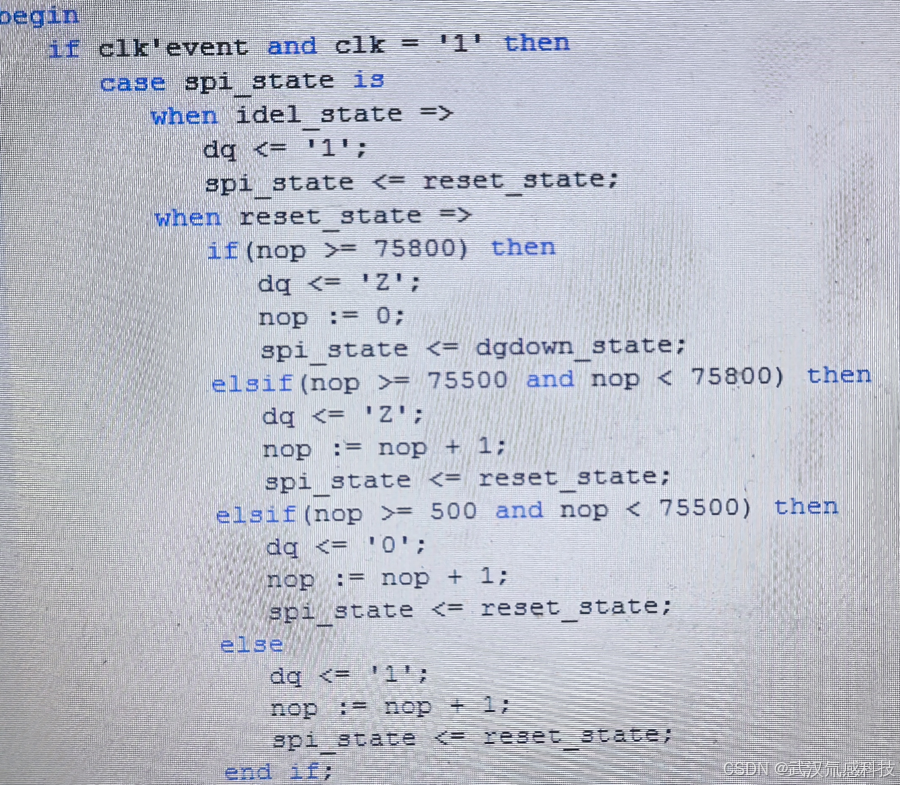

二、VIVADO环境使用上述时序逻辑遇到的问题一

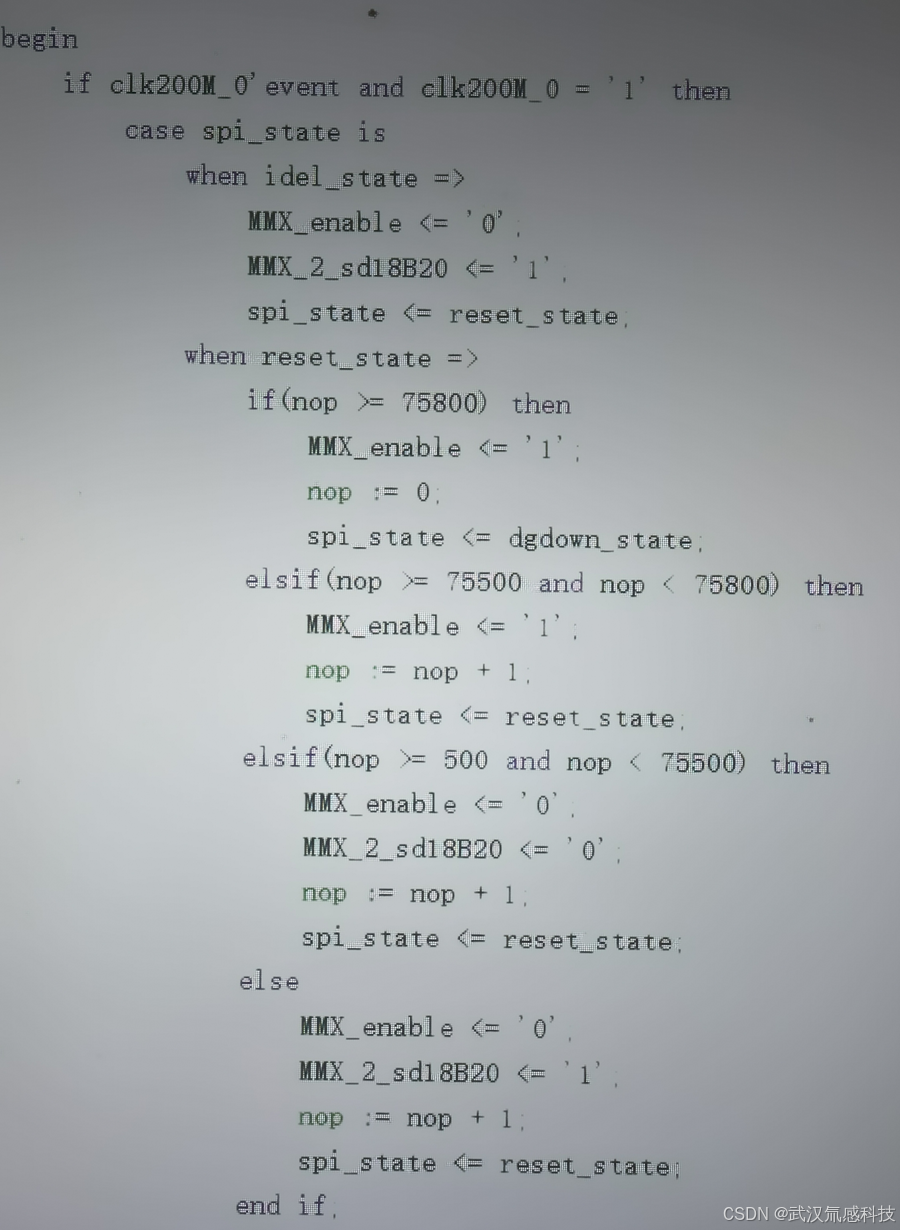

使用VIVADO2018.3环境将移植过来的上述代码进行编译,下载到FPGA中始终无法测量并获取有效的温度信息,温度信息一直为“0”,使用示波器测量inout端口,发现inout端口的数据绝大多数时间为“0”电平,同时笔者也查看了RTL原理图,发现VIVADO环境下开发工具并没有实现三态控制,端口信号只是简单的综合成了一个输出信号。查阅了很多资料信息后,笔者确定在VIVADO环境下需要调用IOBUF原语实现inout端口功能,笔者并对相关的时序代码进行了修改,最终成功完成代码编译。VIVADO环境下inout端口控制时序代码如下图二所示。

图2 VIVADO环境下inout端口控制时序代码

三、VIVADO环境中编译器布局布线过程中遇到的问题二

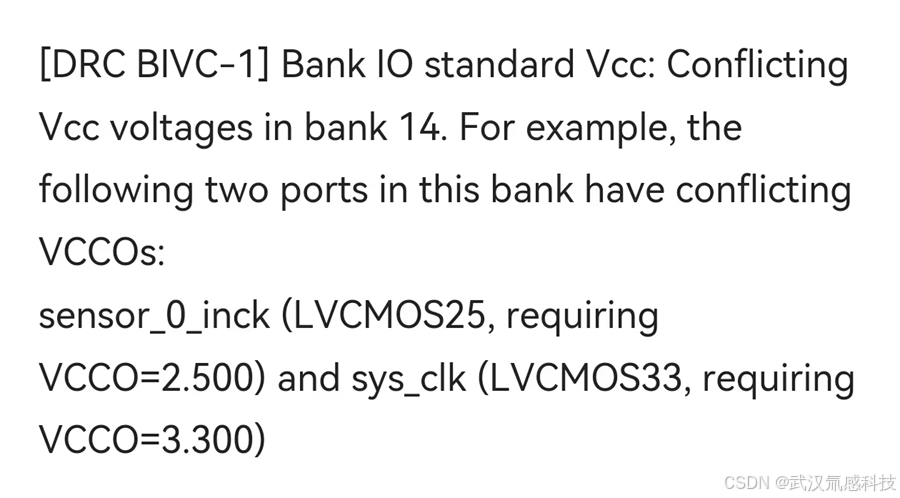

在使用VIVADO环境中编译器编译生成bitstream文件过程中一直提示报错;报错内容如下:

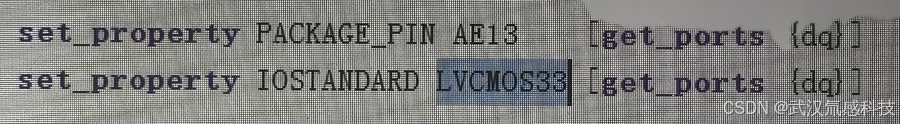

笔者对xdc文件中各个使用引脚的工作电平进行检查,确定inout端口所在的HR bank内其它端口均配置为LVCMOS33,但是编译器在布局布线过程中始终报inout端的电平与其它端口的电平冲突,笔者也在网上查阅了一些关于此问题的处理方法,大多是建议更改端口的电平标准,笔者也尝试将inout端口更改为LVCMOS18,且需要将该inout端口更换至HP bank,虽然可以轻松绕过此问题,但是1.8V电平无法驱动18B20测温传感器,所以更改端口的电平标准并不能从根本上解决该问题。

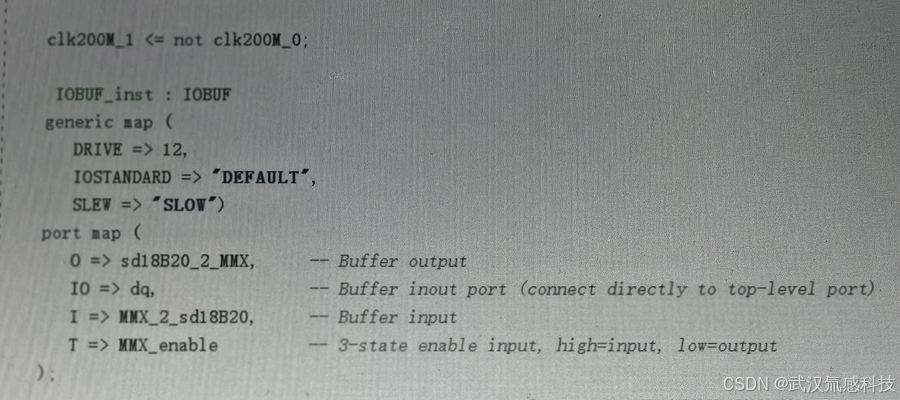

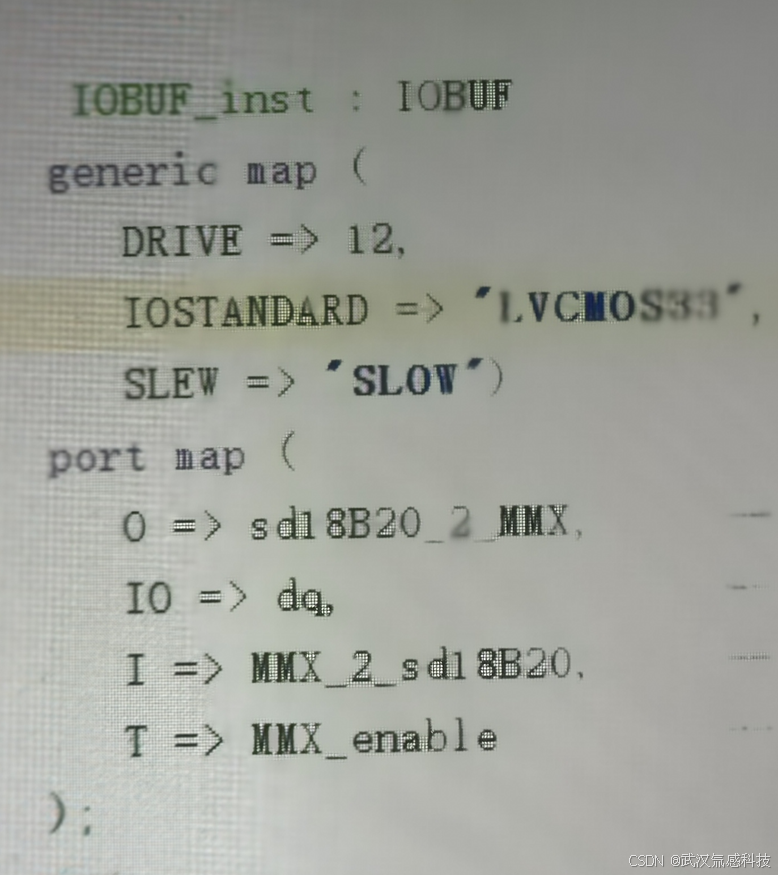

笔者细致的对整个工程文件各部分代码进行了分析,怀疑程序在调用IOBUF原语时IOBUF顶层的IOSTANDARD设置为“DEFAULT”与xdc文件对inout端口设定为LVCMOS33矛盾,最终导致编译过程中报错,最后笔者将源程序中IOSTANDARD更改为LVCMOS33,编译再未出现inout端口电平与其它端口电平冲突的错误。修改后的代码如下图三所示:

图三 修改后的代码

总结

在VIVADO环境下使用inout类型双向端口时,必须调用IOBUF原语实现端口的三态控制;在使用原语调用IOBUF过程中,程序顶层对双向端口的电平定义一定要与xdc文件中关于双向端口的配置部分保持一致。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?