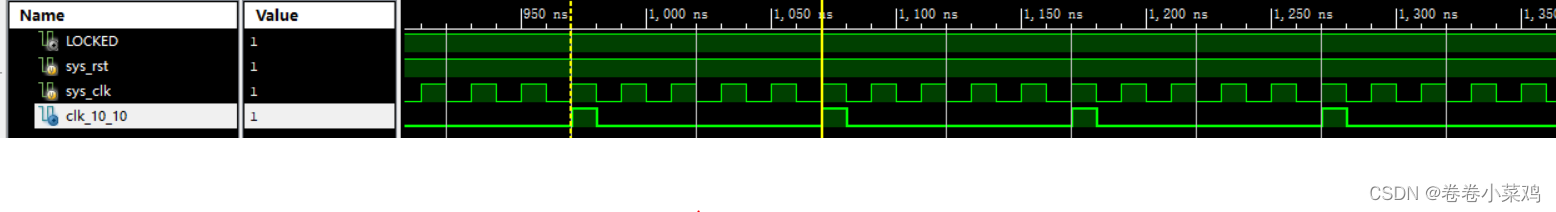

要求:利用锁相环IP核将系统的50MHz进行分频,同时也可以改变占空比(具体数值不重要)

为什么要用ODDR2?

如果不用,PLL_ip核得到的时钟信号在BUFG,直接连接到OBUF上,在编译map时会出现错误,为了避免错误可以在约束文件加一条约束,让编译器忽略时序约束的要求,直接通过普通逻辑资源连接,但是这样CLOCK输出的时延和JITTER都会变差(这种方式不好) (该解释来源于开发板数据手册)

IP核调用的时候,注意复位信号有取反哦。

问题:锁相环IP核可以输出4个时钟数据,但是使用ODDR2只能输出一路,还没找到解决方式,先把这问题留着,有解决方法也请大佬告诉我一下。

module clk_div(

input wire sys_clk ,

input wire sys_rst ,

// output wire clk_100_50 ,

// output wire clk_25_25 ,

output wire clk_10_10 ,

output wire LOCKED

);

pll_div instance_name

(// Clock in ports

.CLK_IN1(sys_clk), // IN

// Clock out ports

.CLK_OUT1(CLK_OUT1), // OUT

.CLK_OUT2(CLK_OUT2), // OUT

.CLK_OUT3(CLK_OUT3), // OUT

// Status and control signals

.RESET(~sys_rst),// IN 注意取反哦

.LOCKED(LOCKED)); // OUT

///调用 ODDR2 使时钟信号通过普通 IO 输出//

ODDR2

#(

.DDR_ALIGNMENT("NONE"), // Sets output alignment to "NONE", "C0" or "C1"

.INIT(1'b0), // Sets initial state of the Q output to 1'b0 or 1'b1

.SRTYPE("SYNC") // Specifies "SYNC" or "ASYNC" set/reset

)

ODDR2_inst (

.Q(clk_10_10), // 1-bit DDR output data 输出信号

.C0(CLK_OUT2), // 1-bit clock input 锁相环输出

.C1(~CLK_OUT2), // 1-bit clock input 锁相环输出取反

.CE(1'b1), // 1-bit clock enable input

.D0(1'b1), // 1-bit data input (associated with C0)

.D1(1'b0), // 1-bit data input (associated with C1)

.R(1'b0), // 1-bit reset input

.S(1'b0) // 1-bit set input

);

endmodulemodule vtf_clk_div;

// Inputs

reg sys_clk;

reg sys_rst;

// Outputs

wire clk_10_10;

wire LOCKED;

// Instantiate the Unit Under Test (UUT)

clk_div uut (

.sys_clk(sys_clk),

.sys_rst(sys_rst),

.clk_10_10(clk_10_10),

.LOCKED(LOCKED)

);

initial begin

// Initialize Inputs

sys_clk = 0;

sys_rst = 0;

// Wait 100 ns for global reset to finish

#100;

sys_rst <= 1'b1;

// Add stimulus here

end

always # 10 sys_clk = ~sys_clk;

endmodule

该文介绍了如何利用锁相环IP核对50MHz系统时钟进行分频,并改变占空比。由于直接使用PLL_ip核输出到OBUF会导致编译错误,因此推荐使用ODDR2来输出时钟信号。在模块设计中,需要注意复位信号的取反。然而,目前遇到的问题是ODDR2只能输出一路时钟,而锁相环IP核可以输出多个时钟,这个问题尚未解决。

该文介绍了如何利用锁相环IP核对50MHz系统时钟进行分频,并改变占空比。由于直接使用PLL_ip核输出到OBUF会导致编译错误,因此推荐使用ODDR2来输出时钟信号。在模块设计中,需要注意复位信号的取反。然而,目前遇到的问题是ODDR2只能输出一路时钟,而锁相环IP核可以输出多个时钟,这个问题尚未解决。

767

767

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?