PCB设计学习笔记

一. PCB的层叠设计

1.多层板有一层完整的地平面,给信号提供阻抗最低的回路。

2.PCB层叠设计规则(f>10MHz)

信号层应总与平面相邻

信号层应与相邻的平面层紧密耦合

电源与接地平面应紧密耦合

高速信号布内层

多个接地平面

关键信号线必须换参考时,应该在同一平面相邻的2层上换参考。

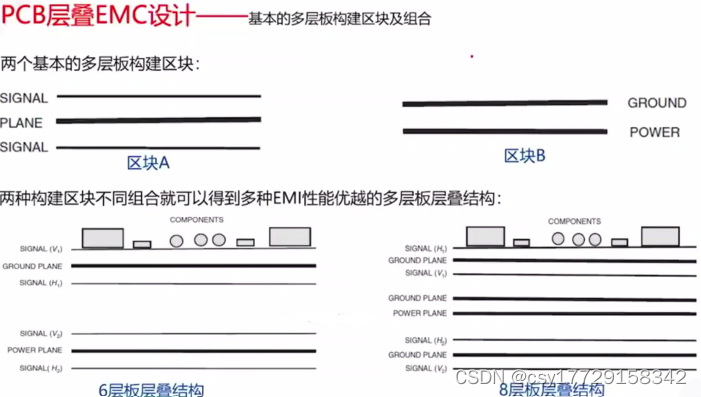

3.PCB层叠EMC设计

A.分割层用电容桥接

B.散的VCC在其中掏一个GND区域,保证重要信号在这个区域中

C.PCB边缘屏蔽:在PCB边缘加地过孔,形成法拉电容原理(远场辐射)可建立模型仿真;VCC地平面超过地过孔会导致屏蔽效能显著下降,所以电源平面必须内缩到周边的地过孔以内。

二.去耦电容设计

1.电源/地平面间去耦目的:

1)当IC状态转换需要额外的电流时,附近的去耦电容通过一个低电感的路径提供这个电流,使IC电源管脚上的电压保持稳定

2)EMI上的要求,降低注入到电源/地平面间的噪声,从而降低电路板边缘辐射

用示波器探电源电流与电压波形-经过傅里叶变换可查看干扰,若有频谱仪,可用探头直接查看各pin脚的情况

查看滤波效果:电压波动的改变 高低频谱

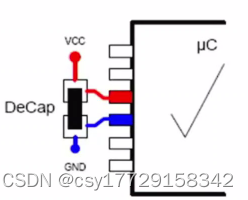

2.去耦电容回路模型

过孔与引线对电感的影响:端过孔,三过孔

3.电容滤波

不同容量的电容阻抗不同,可根据电容谐振频率来选择

- 大小电容并联起来,能在较宽的频段范围内有效(CLC)

- LC优选滤波方案:磁珠+电容

4.去耦电容的PCB布局布线要求:

A.电容与芯片距离(1G以内建议50mil)

B.去耦电容布线:

5.电源去耦案例:观察CE超标频点,找规律,频点多,考虑电源地问题,单一频点过高,设计走线是否走表层;去耦电容对EMI与EMS都有影响。

三.PCB布局设计

1.PCB布局核心原则:就是从空间、传导因素考虑,避免不同电路之间相互干扰!

2.PCB的EMC布局设计着重关注点:

1)模拟器件区域(模拟信号采样电路、传感器电路等)――敏感电路

2)功率模块区域(DC-DC电源模块、功率电感、MOS、IGBT等)――强干扰源

3)高频强干扰器件(晶振、时钟驱动、射频电路)――敏感电路

4)噪声敏感器件(MCU、存储IC、音视频、看门狗等复位电路)――敏感电路

5)滤波防护与器件隔离(防护器件、滤波电容、滤波电感、光耦、变压器)――路径

6)对外接口区域器件(接口连接器、接口滤波器)――路径

3.PCB布局设计——PCB分区布局

1)信号流向“一”字布局原则——沿信号流向直线放置,避免U、Z型

2)电源模块布局:电源部分必须安装在单板电源入口——电源电路要靠近电源连接器,同时,注意电源部分放置方向主要是考虑输入输出线的顺畅,避免交叉,相互之间耦合

3)芯片去耦电容布局原则:就近放置,考虑电容的滤波半径——存在较大电流变化的单元电路或器件(如电源模块的输入输出端、风扇及继电器)附近应放置储能和高频滤波电容。储能电容的存在可以减小大电流回路的环路面积。电容禽管脚越近,高频回路面积越小,从而辐射越小

4)强辐射器件布局规则:晶振、晶体、继电器、开关电源等强辐射器件远离单板接口连接器至少1000mil。否则会将干扰直接向外辐射或在外出电缆上耦合出电流来向外辐射

5)敏感电路射频电路布局:RF电路需要放置在单板的远端角,一般需加屏蔽罩;敏感电路需远离板边,避免噪声与ESD问题

6)匹配电阻布局原则:对于始端串联匹配电阻,应靠近其信号输出端放置,始端串联匹配电阻设计原理是Zs+Rs=Z0,若RS远离其输出端就起不到匹配结果

7)接口电路设计:可做净地处理 8)DC-DC电源:环路面积尽可能小

9)BUCK电源布局设计:环路面积要小

10)晶振布局:不能放在PCB板I/O连接器的走线区域,I/O电缆耦合时钟信号会导致EMI辐射超标

四.高速信号跨分割上设计

1.时钟走线跨分割辐射机理

A.信号回流绕过分割形成大的环路,环形天线效应使差模辐射增加

B.回流u环路大,净电感量增大,从而在回流路径上产生噪声电压降增大,这个噪声电压使得流过I/O电缆的共模电流增大从而共模辐射也增加

2.高速信号回流:先扩散再收敛,远近两端为高阻特征值,信号总线过孔处的地增加GND过孔以减小回流路径

3.高速信号跨分割:

1)关键信号跨分割可以在30M-1GHz范围内引起 30dB以上的辐射增加,应尽量避免跨分割;

2)在跨分割处增加2个缝补电容与增加一个相比30M-1GHz内大部分频段有3-8dB的辐射发射改善;

3) 縫补电容封装越小,EMI抑制效果越好;缝补电容推荐0402;

4) 缝补电容在同样封装的情况下选用尽量大的容值,推荐100nF;

5) 缝补电容离跨分割处距离越近辐射越小,建议不超过250mil。

4.易忽视跨分割问题:集中地过孔;连接器之间

五.高速信号换参考设计

1.PCB关键走线换参考层缓解措施:加地过孔 加缝补电容

2.关键走线换参考设计总结

1)关键信号无论在两个相同性质的参考面之间或不同性质的参考面间换参考,对EMI辐射的影响都非常大,会导致20dB左右的辐射增加,应尽量避免关键信号换参考

2)关键信号在两个相同性质的参考面之间换参考时,建议在离换参考过孔50mil的距离内增加2个对称的缝补过孔;关键信号在两个不同性质的参考面之间换参考时,建议在离换参考过孔50mil的距离内增加2个对称的100nF、0402封装的缝补电容

3)在与同一参考平面相邻的2个信号层上换参考对辐射的影响非常小,是可接受的

六.底层叠结构PCB板EMC设计

双面板的接地设计:梳状接地-网格地

1.单层板:电源走线附近必须与其紧邻、平行走线,减小电源电路回流面积,减小差模环路辐射

2.双层板:需注意电源走线与GND走线之间可能构成的环路

3.布线设计规则:

关键信号两侧地“包地线”

关键信号地投影平面局部掏空再铺地

时钟回流加伴地走线打过孔或加缝补电容

单板空余区域表底层铺GND碎铜再打过孔

七.PCB接口区域EMC设计

1.I/O连接器的PCB布局:

尽可能减小裸露线的长度

净地区域划分(GND、E-GED、PE)保证接口净地

接口先防护后滤波,同时隔离器件一定要放在隔离带上

接地柱尽可能靠近I/O接口PCB的地平面应通过铜柱多点接机壳

2.IO端口的“干净地”――保证至少两个接地螺钉与外壳连接

3.共模滤波与差模滤波区别:电感器件不同、电容的接地方法不同

差模滤波:差模电感,X电容接地

共模滤波:共模电感,Y电容接机壳

当信号地与机壳连接时,共模滤波电容也是差模滤波电容,会对差模信号产生影响

共模电容的大小会影响信号质量,共模电容需要好的接地效果,线路板的两面都有较大面积的地

八.PCB之分地设计

1.分地来源于功能电流,硬件电路需求

2.数字地与模拟地问题

数模地分割――单点连接 滤波电容 滤波磁珠(放分割带位置)

3.功率地:高压隔离 低压单点连接

4.Π型滤波电路分地设计——共阻抗,左右分地

5.共模电感分地设计——共模电感下边掏空处理(否则影响高频)

九.Pin Map的EMC设计

1.定义:电子产品设计中,对接口连接器、PCB连接器等连接器的Pin针电气网络属性进行定义、确保产品的电气性能达成。

2.Pin Map与EMC问题

a.信号回流绕分割,形成环形天线,差模辐射增加

b.信号环路大,净电感增大,噪声电压增大,共模辐射增加

C.连接器位置时钟等关键信号走线回流阻抗变化,与跨分割问题原理一致

3.连接器Pin Map的EMI设计规则

1)连接器中Pin周围的GND Pin数量尽量多,地Pin数量越多,辐射越小

2)信号针临近的2个GND Pin优先采用180度分布

3)不用的信号pin不能悬空,要做匹配设计

3098

3098

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?