名称:任意进制计数器12进制计数数码管显示verilog代码

软件:VIVADO

语言:Verilog

代码功能:

设计一个12进制计数器,计数值00-11需要在数码管上显示,

时钟脉冲通过按键开关设计。

电路的输入信号en进行清零。

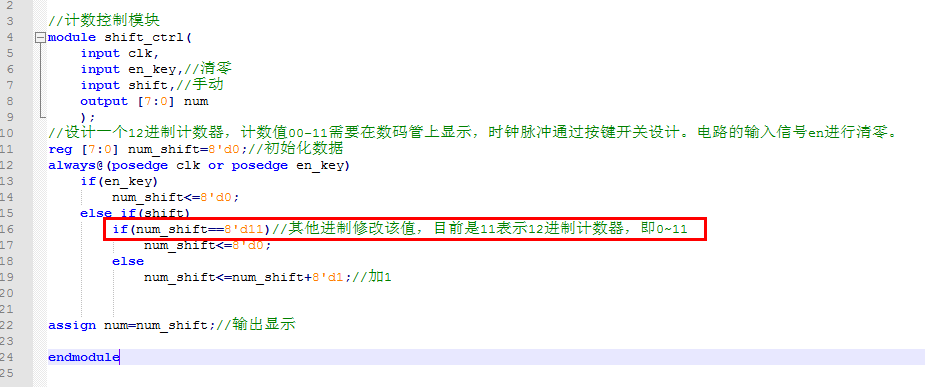

本代码可以修改为任意进制计数器,即修改计数控制模块的红框内代码,如下所示:

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

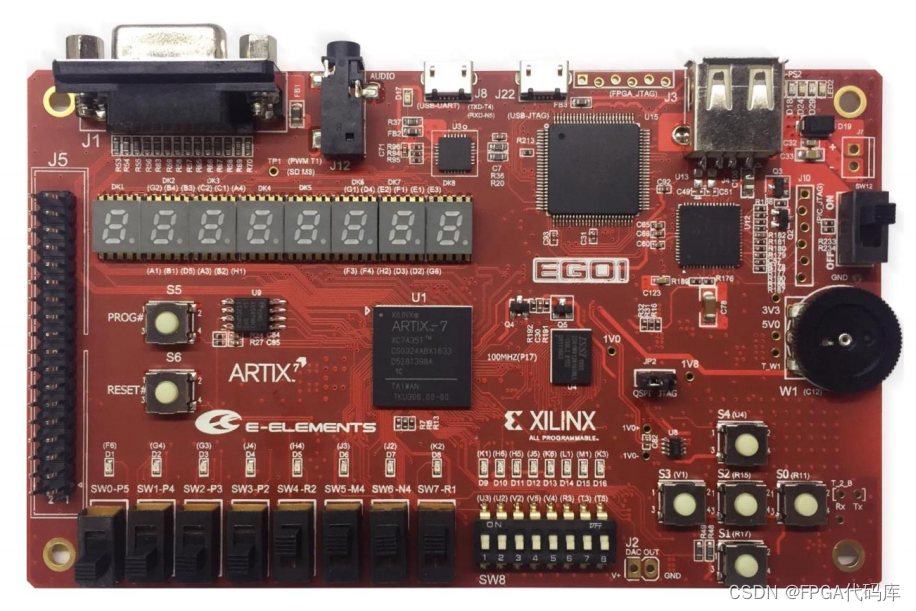

本代码已在ego1开发板验证,开发板如下,其他开发板可以修改管脚适配:

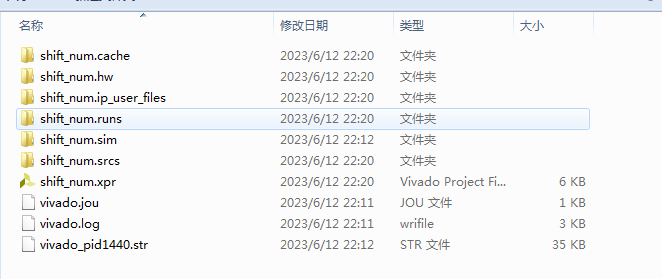

1. 工程文件

2. 程序文件

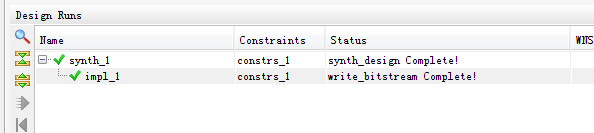

3. 程序编译

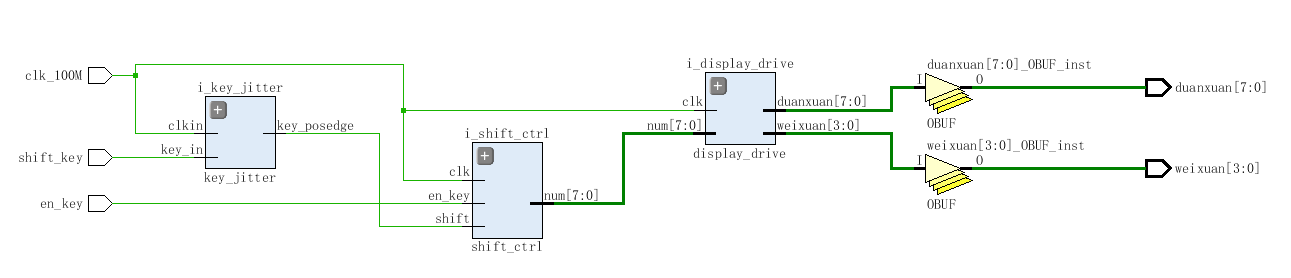

4. RTL图

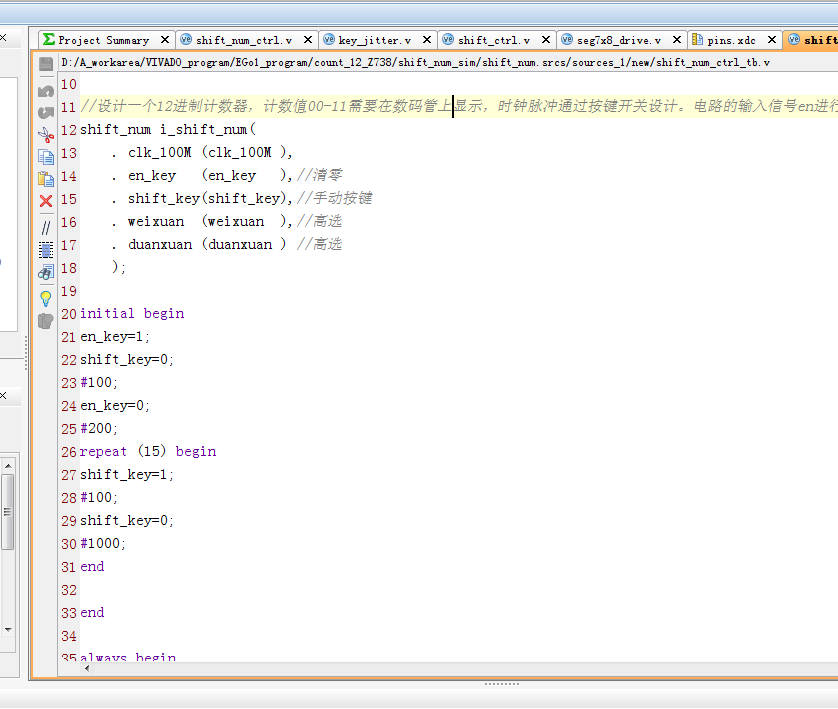

6. Testbench

7. 仿真图

整体仿真图

按键模块

控制模块

显示模块

部分代码展示:

`timescale 1ns / 1ps //设计一个计数器 module shift_num( input clk_100M, input en_key,//清零 input shift_key,//手动按键 output [3:0] weixuan,//高选 output [7:0] duanxuan//高选 ); wire [7:0] num; wire shift_key_en; //按键消抖 key_jitter i_key_jitter( . clkin(clk_100M), . key_in(shift_key),//输入 . key_posedge(shift_key_en)//消抖后按键上升沿 ); //计数控制模块 shift_ctrl i_shift_ctrl( . clk(clk_100M), . en_key(en_key),//清零 . shift(shift_key_en),//手动按键 . num(num)//数 ); //数码管显示模块 display_drive i_display_drive( . clk(clk_100M), . num(num),//数 . weixuan(weixuan),//高选 . duanxuan(duanxuan)//高选 ); endmodule

本文介绍了一款使用Verilog语言设计的12进制计数器,通过VIVADO软件在ego1开发板上实现,支持按键控制和数码管显示。代码包括按键消抖、计数控制和显示模块,可灵活修改为任意进制计数器。

本文介绍了一款使用Verilog语言设计的12进制计数器,通过VIVADO软件在ego1开发板上实现,支持按键控制和数码管显示。代码包括按键消抖、计数控制和显示模块,可灵活修改为任意进制计数器。

9252

9252

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?