名称:洗衣机控制器设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

洗衣机控制器

1)设计一个电子定时器,控制洗衣机作如下运转:定时启动正转20秒暂停10秒反转20秒暂停10秒定时未到回到“正转20秒暂停10秒....,定时到则停止

2)若定时到,则停机发出音响信号;

3)用两个数码管显示洗涤的预置时间(分钟数),按倒计时方式对洗涤过程作计时显示,直到时间到停机;洗涤过程由“开始”信号开始;

4)、三只LED灯表示“正转”、“反转”、“暂停”三个状态

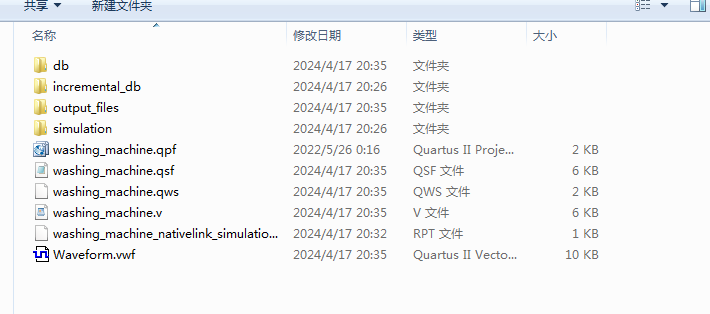

1. 工程文件

2. 程序文件

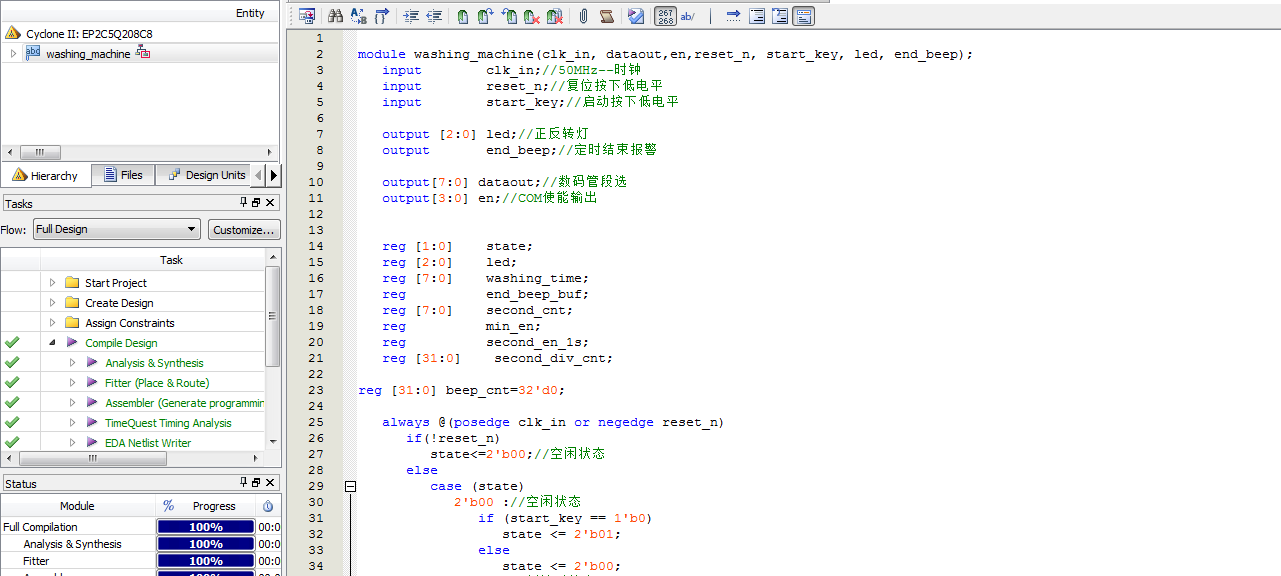

3. 程序编译

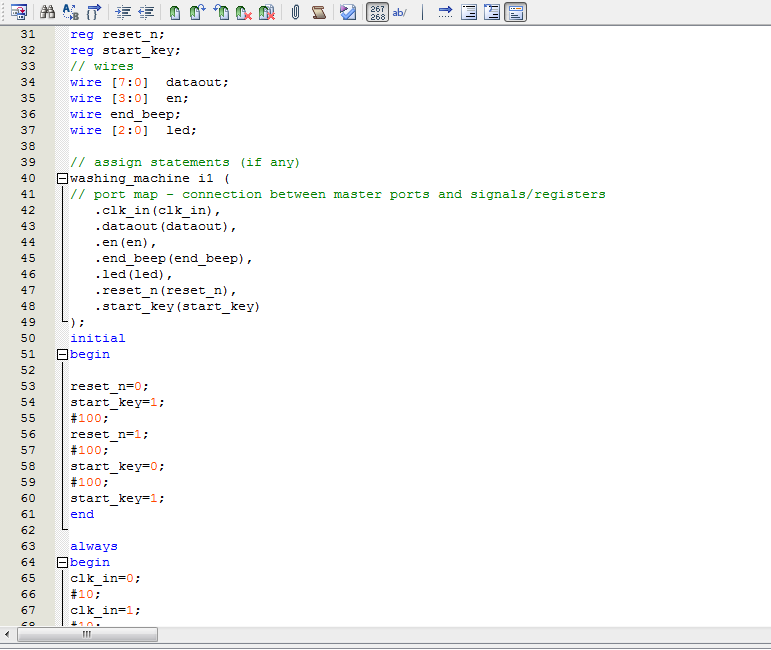

4. Testbench

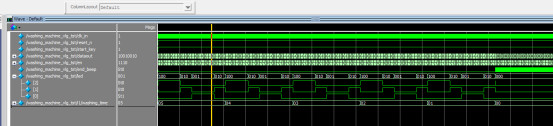

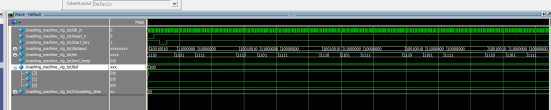

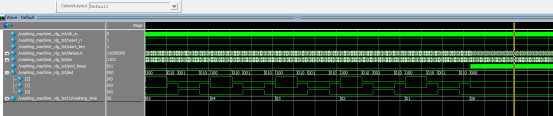

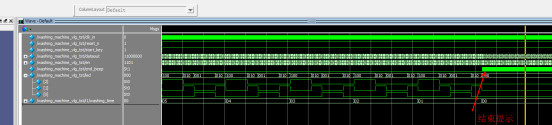

5. 仿真图

部分代码展示:

module washing_machine(clk_in, dataout,en,reset_n, start_key, led, end_beep); input clk_in;//50MHz--时钟 input reset_n;//复位按下低电平 input start_key;//启动按下低电平 output [2:0] led;//正反转灯 output end_beep;//定时结束报警 output[7:0] dataout;//数码管段选 output[3:0] en;//COM使能输出 reg [1:0] state; reg [2:0] led; reg [7:0] washing_time; reg end_beep_buf; reg [7:0] second_cnt; reg min_en; reg second_en_1s; reg [31:0] second_div_cnt; reg [31:0] beep_cnt=32'd0; always @(posedge clk_in or negedge reset_n) if(!reset_n) state<=2'b00;//空闲状态 else case (state) 2'b00 ://空闲状态 if (start_key == 1'b0) state <= 2'b01; else state <= 2'b00; 2'b01 ://倒计时状态 if (washing_time > 8'b00000000) state <= 2'b01; else state <= 2'b10; 2'b10 ://结束 state <= 2'b10; default : state <= 2'b00; endcase always @(posedge clk_in) begin if (state == 2'b10)//结束计数 beep_cnt <=beep_cnt+ 1'b1; end always @(posedge clk_in) begin if (state == 2'b10)//结束 end_beep_buf <= 1'b1; else end_beep_buf <= 1'b0; end reg [31:0] beepclk_cnt=32'd0; reg beepclk=0; always @(posedge clk_in) begin if(beepclk_cnt>=32'd10)begin//仿真时将25_000改小为10 beepclk_cnt<=0; beepclk<=~beepclk; end else begin beepclk_cnt<=beepclk_cnt+1; beepclk<=beepclk; end end assign end_beep = end_beep_buf & beepclk; always @(posedge clk_in) if(state!=2'b01)//非倒计时状态清零 begin second_div_cnt <= 32'd0; second_en_1s <= 1'b0; end else//倒计时状态计时 begin if (second_div_cnt >= 32'd50)//50_000_000--50M计数50000000为1s,仿真将计数器改小为50 begin second_div_cnt <= 32'd0; second_en_1s <= 1'b1;//50MHz分频为1Hz end else begin second_div_cnt <= second_div_cnt + 32'd1; second_en_1s <= 1'b0; end end always @(posedge clk_in) begin if (state!=2'b01)//非倒计时状态清零 second_cnt <= 8'b00000000; else if (second_en_1s == 1'b1)//倒计时状态计时 begin if (second_cnt >= 8'd59)//59s second_cnt <= 8'd0; else second_cnt <= second_cnt + 8'd1; end else second_cnt <= second_cnt; end always @(posedge clk_in) begin if (second_en_1s == 1'b1 && second_cnt == 8'd59) min_en <= 1'b1;//分钟信号 else min_en <= 1'b0; end

源代码

点击下方的公众号卡片获取

3095

3095

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?