名称:正弦波方波三角波信号发生器设计VHDL代码Quartus仿真(文末获取)

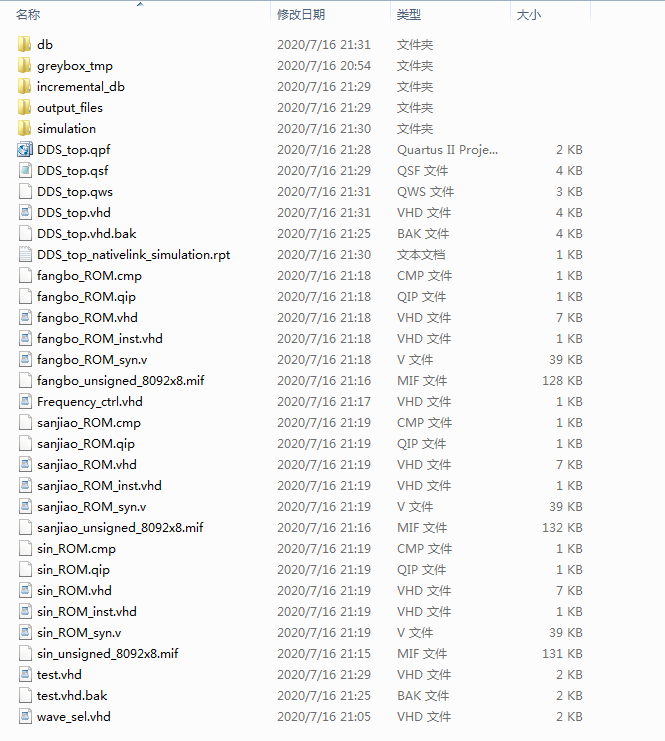

软件:Quartus

语言:VHDL

代码功能:

正弦波方波三角波信号发生器

1、可以通过开关控制输出正弦波、方波、三角波

2、输出波形的频率可以控制

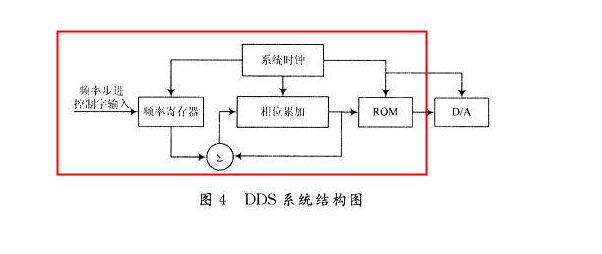

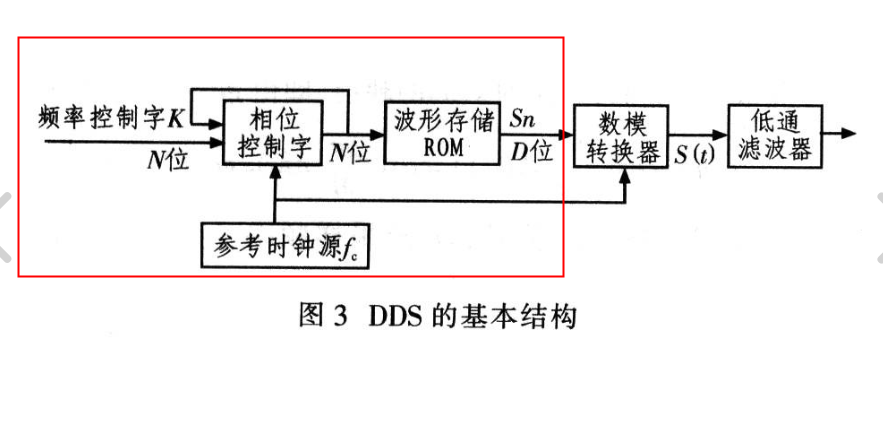

DDS原理

1. 工程文件

2. 程序文件

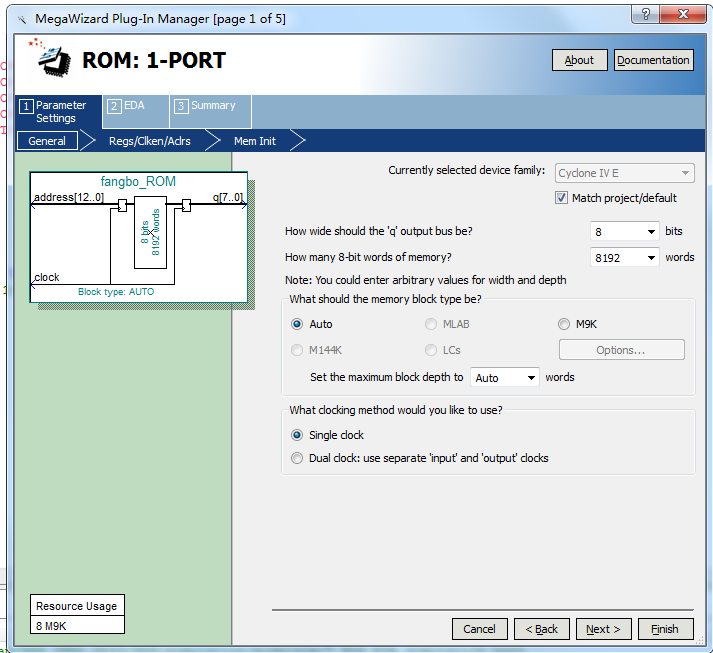

ROM IP核

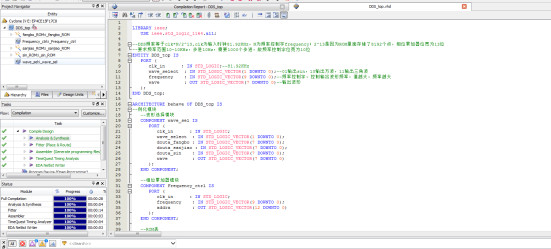

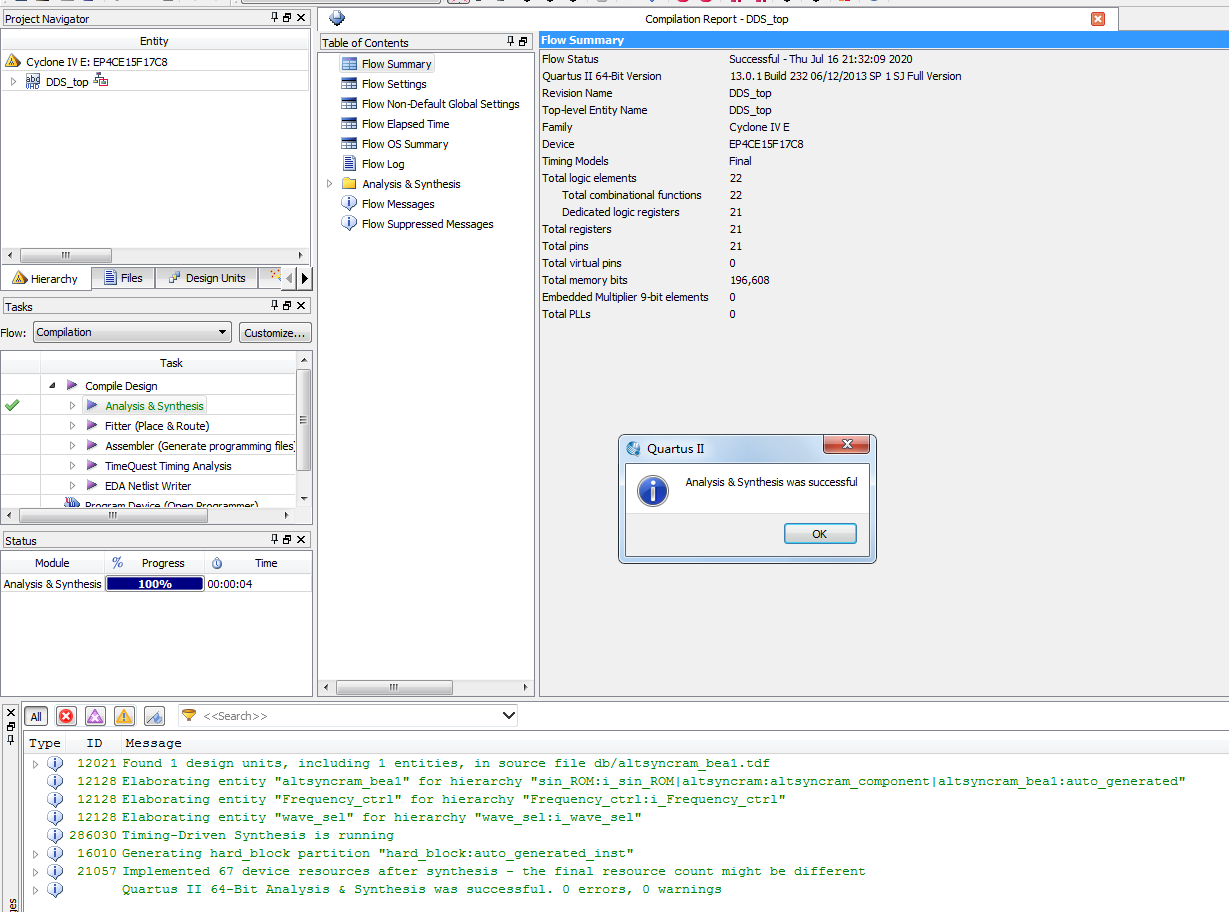

3. 程序编译

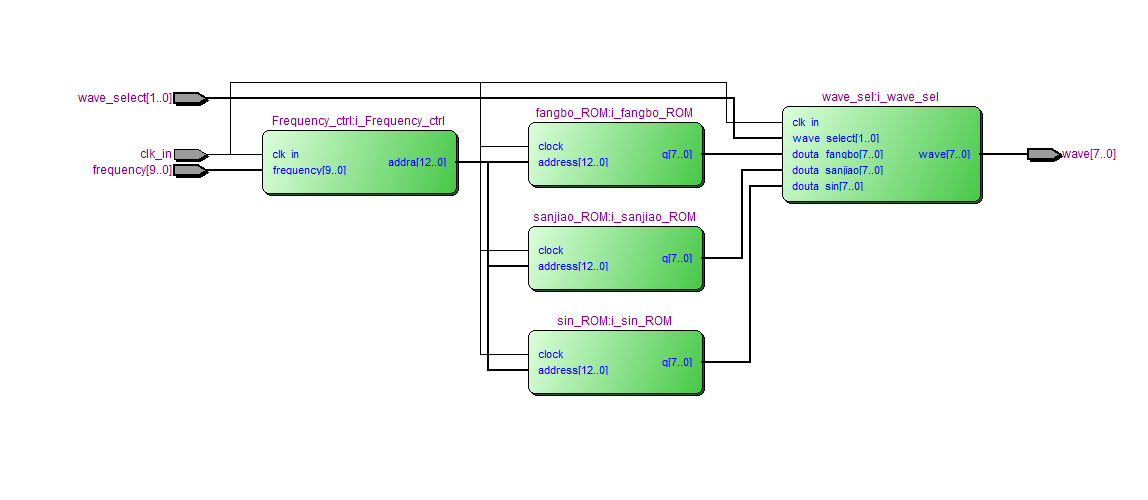

4. RTL图

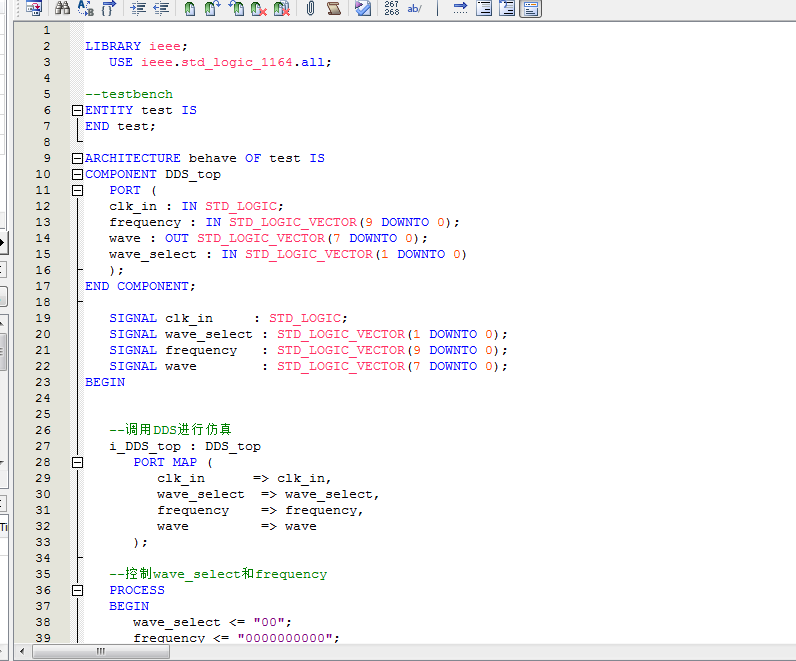

5. Testbench

6. 仿真图

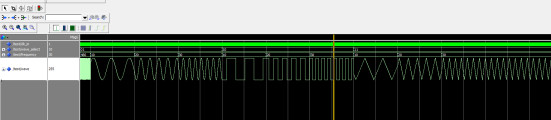

整体仿真图

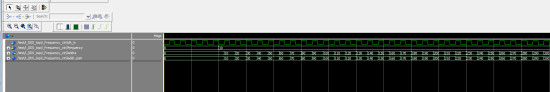

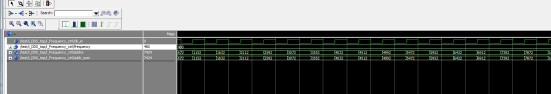

相位累加器模块

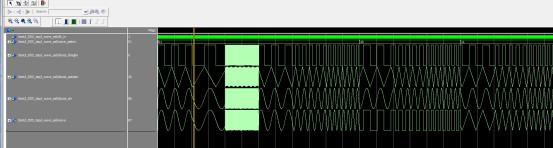

波形选择模块

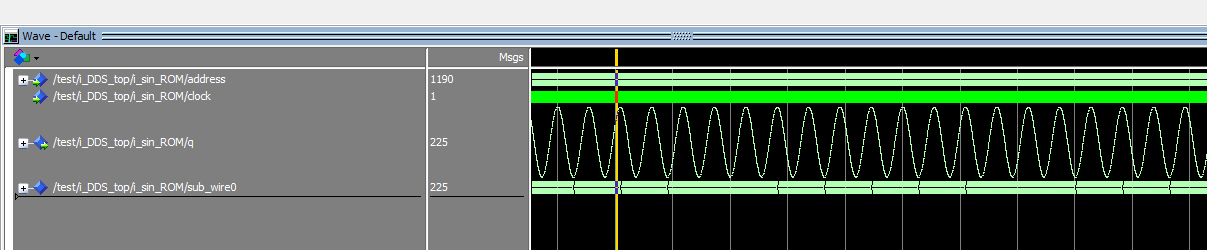

正弦波ROM

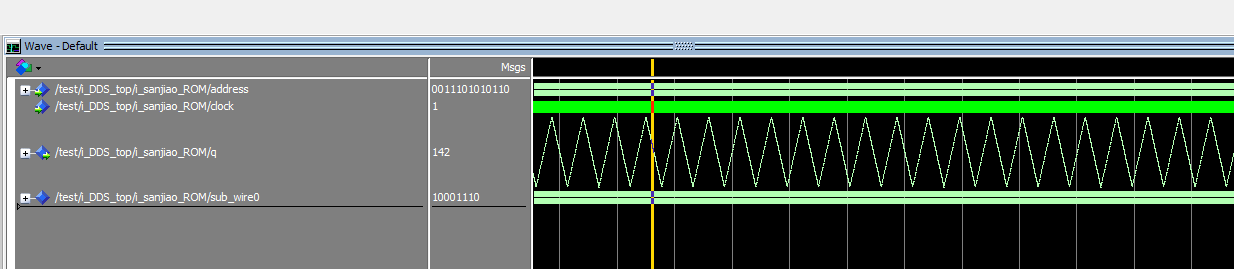

三角波ROM

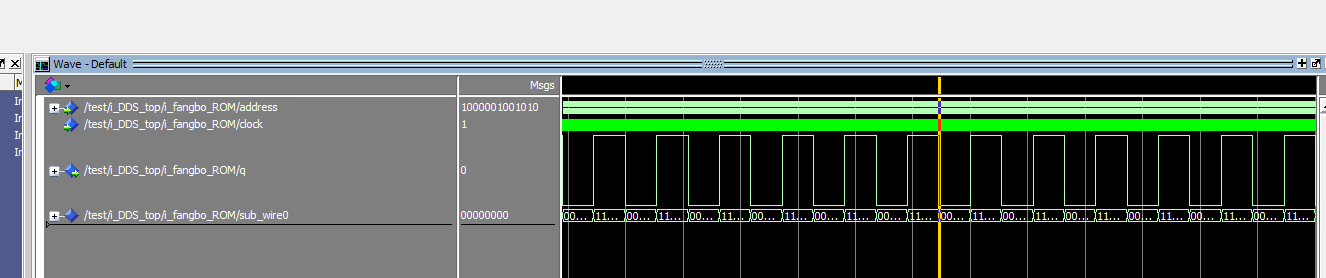

方波ROM

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; --DDS频率等于clk*N/2^13,clk为输入时钟81.92KHz,N为频率控制字frequency;2^13是因为ROM里面存储了8192个点,相位累加器位宽为13位 --要求频率范围10~10KHz,步进10Hz,需要1000个步进,故频率控制字位宽为10位 ENTITY DDS_top IS PORT ( clk_in : IN STD_LOGIC;--81.92KHz wave_select : IN STD_LOGIC_VECTOR(1 DOWNTO 0);--01输出sin,10输出方波,11输出三角波 frequency : IN STD_LOGIC_VECTOR(9 DOWNTO 0);--频率控制字,控制输出波形频率,值越大,频率越大 wave : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--输出波形 ); END DDS_top; ARCHITECTURE behave OF DDS_top IS --例化模块 --波形选择模块 COMPONENT wave_sel IS PORT ( clk_in : IN STD_LOGIC; wave_select : IN STD_LOGIC_VECTOR(1 DOWNTO 0); douta_fangbo : IN STD_LOGIC_VECTOR(7 DOWNTO 0); douta_sanjiao : IN STD_LOGIC_VECTOR(7 DOWNTO 0); douta_sin : IN STD_LOGIC_VECTOR(7 DOWNTO 0); wave : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END COMPONENT; --相位累加器模块 COMPONENT Frequency_ctrl IS PORT ( clk_in : IN STD_LOGIC; frequency : IN STD_LOGIC_VECTOR(9 DOWNTO 0); addra : OUT STD_LOGIC_VECTOR(12 DOWNTO 0) ); END COMPONENT;

源代码

点击下方的公众号卡片获取

1973

1973

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?