上篇中我们说了OCV和AOCV,需要的可以点击这里:数字IC后端知识扫盲——OCV(上)

简而言之,OCV是由于芯片上因为工艺(Process),电压(Voltage),温度(Temperature)而导致的各种误差而加入的裕量,而AOCV在考虑到实际误差并非统一值得情况下将裕量变成cell级数的函数,从而减少一定的设计悲观量(pessimism)

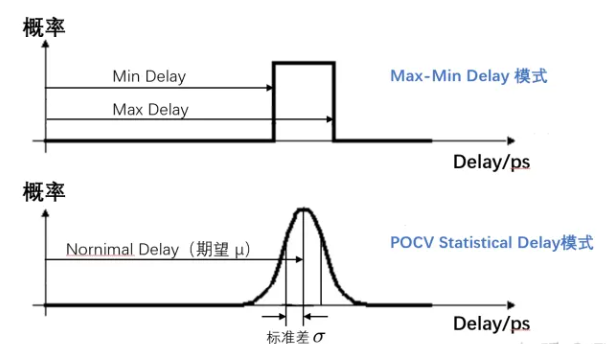

今天我们绩效探探他们的升级版:POCV和LVF,上次我们说过,实际中由于PVT(process Voltage,Temperature)导致的variation并不是一个或几个固定的值,而是服从类似高斯分布的形态,因此,反映在cell的delay上也是如此:

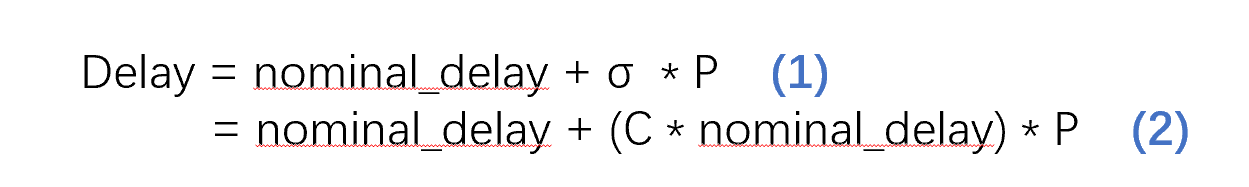

如上图所示,所谓POCV,也称SOCV(Statistical On Chip Variation),就是将cell的delay模拟成一个数学期望为 μ ,标准差为 σ 的高斯分布。简单地讲,每个cell的delay都有最高的概率出现在期望值上,有一定的概率出现在大于或者小于期望值一定范围内的区间上。整体上落在期望值 ±3σ 区间内的概率为99.7%,即所谓的3 sigma。那么实际中工具是如何算得cell的delay呢?基本公式如下:

如果在.lib中提供了sigma的数值,则可以通过公式(1)算出,如果通过read_aocvm读取的POCV的参数文件(包含参数C),则可以通过公式(2)算出,这种通过给定的参数计算cell的OCV delay的方式就是'Parametric'的含义。

那么这和LVF和上面这些东西有什么关系呢?下面我们详细说说。

LVF(Liberty Variation Format)

从它的名字Liberty Variation Format我们可以看出LVF是一种和liberty库文件(.lib)有关的数据格式。

我们知道一般情况下无论是AOCV或者POCV,都会有一个专门的文本文件通过特定的命令读取到工具中。以PrimeTime为例,读取AOCV和POCV的命令如下:

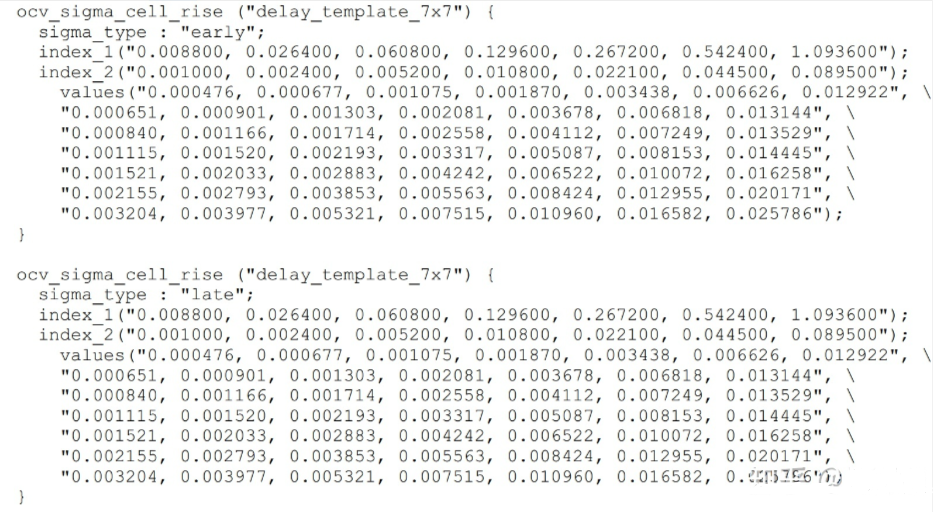

read_aocvm $file_name而除了这种方式之外,我们还有另外一种选择:将POCV的内容集成到类似于liberty文件中,如下图所示:

Slew-Load Based LVF

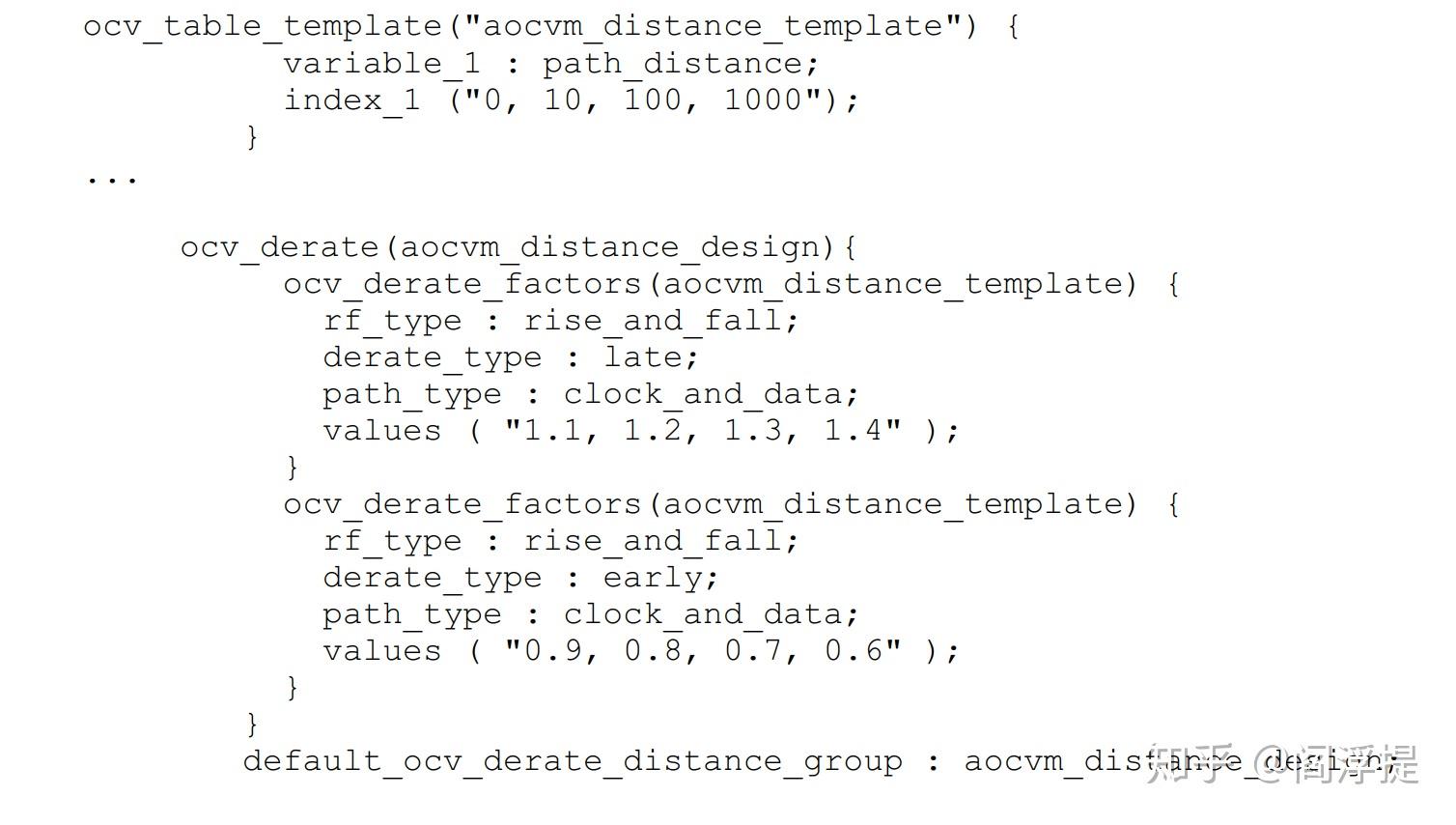

我们可以看出来,这种形式很像liberty文件中的delay查找表,在这里,POCV的coefficient同样是一个基于slew-load的表格。同时,LVF中也可以是基于distance的查表:

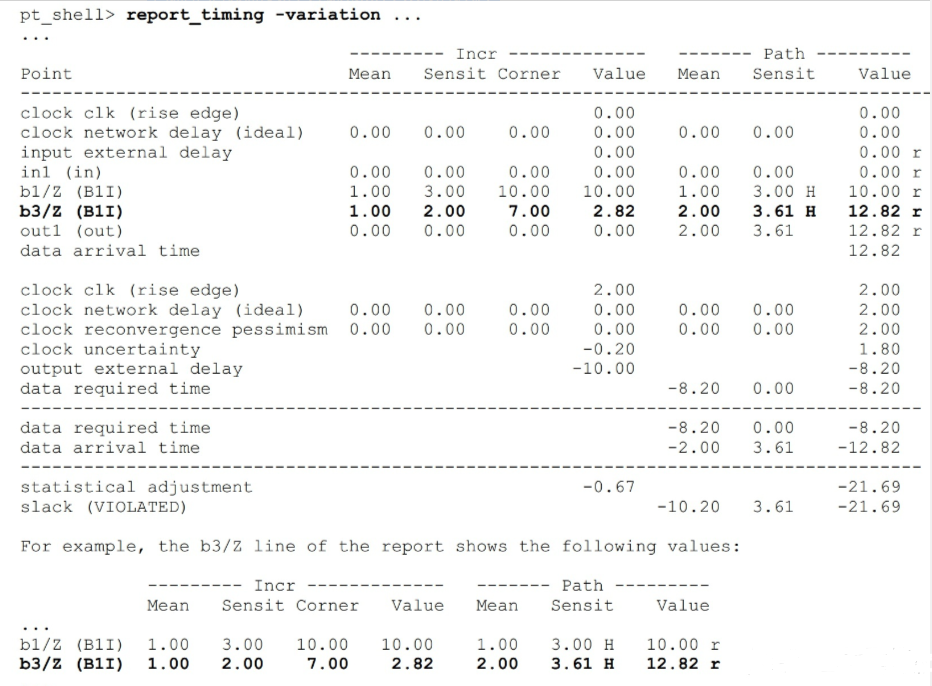

需要注意的是,在使用LVF的时候就不能通过read_aocvm读取专用的POCV文本。在PrimeTime中我们也可以通过如下方式report POCV的结果:

至此,关于OCV的话题我们就基本讲完了。在实际设计中虽然还有很多细节需要注意,但是就基本概念来讲,还是希望大家能够理解它们的差别。目前在尖端工艺中,POCV和LVF都在渐渐普及,如果有在做相关项目的童鞋,希望借此机会好好注意项目中是如何使用它们的,这将有助于我们深入理解它们的应用。

文章介绍了POCV(StatisticalOn-ChipVariation)和LVF(LibertyVariationFormat)在处理芯片因工艺、电压和温度变异导致的延迟问题上的应用。POCV将cell延迟模拟为高斯分布,而LVF是一种将POCV数据集成到liberty库文件中的格式,提供基于slew-load或distance的查表方式。在尖端工艺设计中,POCV和LVF逐渐普及,对于理解和优化设计至关重要。

文章介绍了POCV(StatisticalOn-ChipVariation)和LVF(LibertyVariationFormat)在处理芯片因工艺、电压和温度变异导致的延迟问题上的应用。POCV将cell延迟模拟为高斯分布,而LVF是一种将POCV数据集成到liberty库文件中的格式,提供基于slew-load或distance的查表方式。在尖端工艺设计中,POCV和LVF逐渐普及,对于理解和优化设计至关重要。

3887

3887

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?