DDR3 基本内容简介

DDR 简介

DDR=Double Data Rate双倍速率同步动态随机存储器。严格的说DDR应该叫DDR SDRAM,人们习惯称为DDR,其中,SDRAM 是Synchronous Dynamic Random Access Memory的缩写,即同步动态随机存取存储器。而DDR SDRAM是Double Data Rate SDRAM的缩写,是双倍速率同步动态随机存储器的意思。

SDRAM在一个时钟周期内只传输一次数据,它是在时钟的上升期进行数据传输;而DDR内存则是一个时钟周期内传输两次次数据,它能够在时钟的上升期和下降期各传输一次数据,因此称为双倍速率同步动态随机存储器。DDR内存可以在与SDRAM相同的总线频率下达到更高的数据传输率。

与 SDRAM 相比:DDR 运用了更先进的同步电路,使指定地址、数据的输送和输出主要步骤既独立执行,又保持与 CPU 完全同步;DDR 使用了 DLL(Delay Locked Loop,延时锁定回路提供一个数据滤波信号)技术,当数据有效时,存储控制器可使用这个数据滤波信号来精确定位数据,每 16 次输出一次,并重新同步来自不同存储器模块的数据。DDR 本质上不需要提高时钟频率就能加倍提高 SDRAM 的速度,它允许在时钟脉冲的上升沿和下降沿读出数据,因而其速度是标准 SDRAM 的两倍。从外形体积上 DDR 与 SDRAM 相比差别并不大,他们具有同样的尺寸和同样的针脚距离。但 DDR 为 184 针脚,比 SDRAM 多出了 16 个针脚,主要包含了新的控制、时钟、电源和接地等信号。DDR 内存采用的是支持 2.5V 电压的 SSTL2 标准,而不是 SDRAM 使用的 3.3V 电压的 LVTTL 标准。

DDR3 简介

DDR3全称double-data-rate 3 synchronous dynamic RAM,即第三代双倍速率同步动态随机存储器。所谓同步,是指DDR3数据的读取写入是按时钟同步的;所谓动态,是指 DDR3 中的数据掉电无法保存,且需要周期性的刷新,才能保持数据;所谓随机存取,即可以随机操作任一地址的数据;所谓 double-data-rate,即时钟的上升沿和下降沿都发生数据传输。

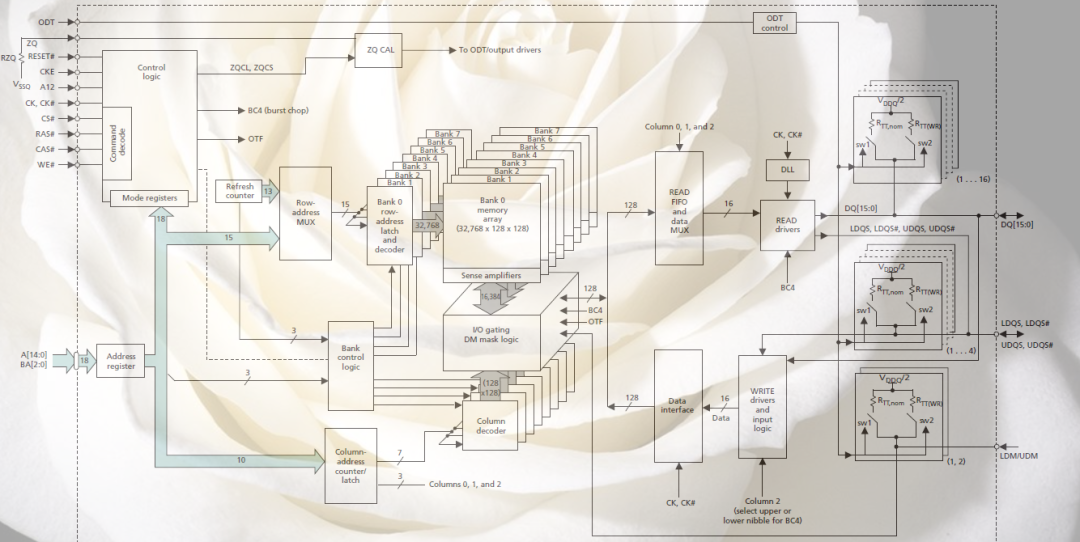

以 micron 的 MT41K256M16TW-107 为例,MT41K 为型号,256M16 表示大小为 256M*16 = 4Gb,TW为 96pin BGA 封装,-107 为速度等级(时钟1.07ns,933Mhz,速度 1866MT/s),平常说的 DDR3 1333 也就是指 1s 内传输 1333 次数据。该 DDR3 是 8Bank 配置,即 BA[2:0];数据位宽配置为16bit;行地址 A[14:0],列地址 A[9:0],那么算下来正好 4Gb。不过需要注意,由于 8n prefetch,列地址 A[2:0]实际上并不使用,因为存储矩阵中一个单元(CELL)为 128bit,即一个 Bank 内是按 32768*128*128 划分的,如下图所示。

顺便讲一下逻辑 Bank 和物理 Bank 的区别,逻辑 Bank 即一片 DDR3 颗粒的 Bank;物理 Bank 是在存储系统中才有的概念,计算机 CPU 为 64bit,故向存储设备取数据也为 64bit,那么就需要 4 片 DDR3 颗粒并联,那么总共的容量就位 4Gb;那么问题来了,如果需要 32Gb 的容量呢?那么就需要 32 片 DDR3 颗粒,该 DDR3 最小位宽可配置为 4bit,那么按照直接并联的方式就变成 128bit 位宽了,这时候就需要做成 2 个物理 Bank。

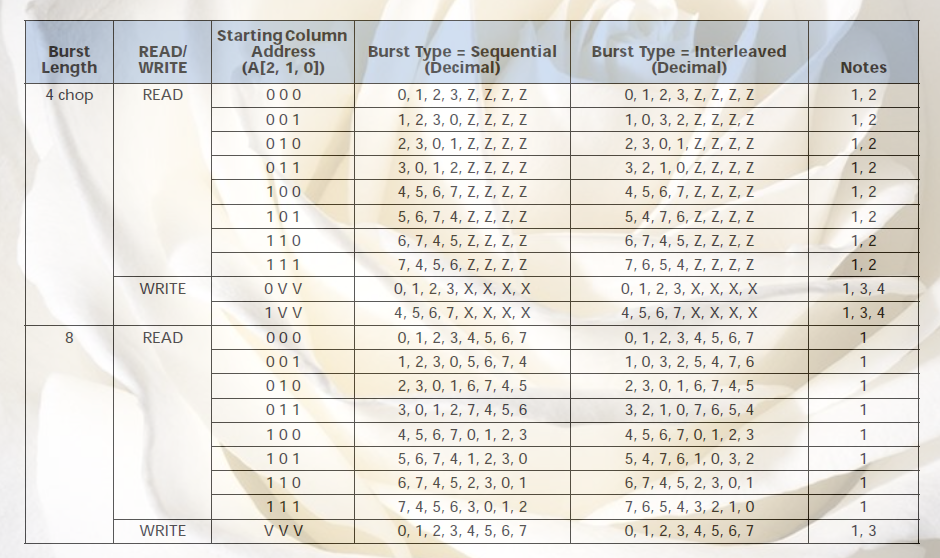

DDR3 的数据写入与读取都是按 burst 方式进行的,BC4 一次 burst 进行 4 长度数据位宽传输,BL8 一次 burst 进行 8 长度数据位宽传输,on-the-fly 由用户控制 8 还是 4。Burst 模式有两种,sequential 和 interleaved,具体如图所示。

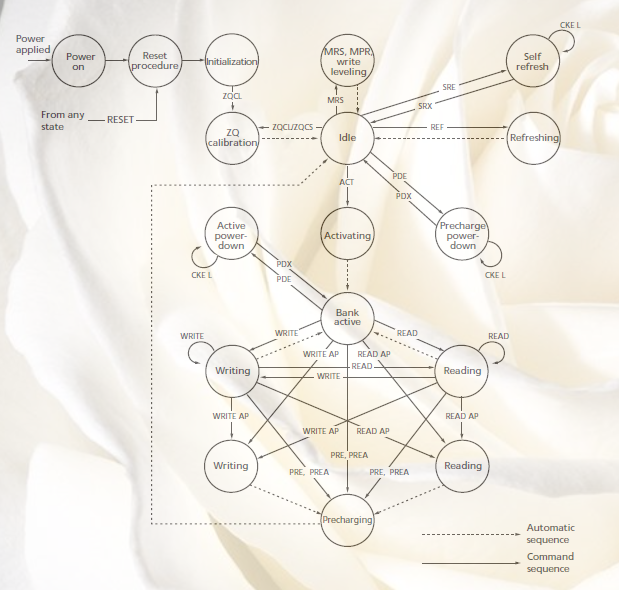

DDR3 的运行流程大体为:上电复位;然后进入初始化流程,进行 write leveling、ZQ 校准后进入空闲状态,此后用户可对其进行读写操作;we#,ras#,cas# 为控制信号;操作时,先激活某一 bank 某一行,然后再给列地址,写完后换另一行需要进行 precharge 操作;为了保持数据,DDR3 需要 refresh 操作,一般规定行刷新周期为 64ms,这里的行是针对所有 bank 的同一行,与 precharge 需要区分。具体如下图所示。

DDR3 中的一些关键信号与时间参数

-

关键信号

-

RAS#,行地址选通信号

-

CAS#,列地址选通信号

-

WE#,读写信号

-

DQS,差分信号,数据选通信号,与读数据边沿对齐,与写数据中心对齐

-

CK,差分信号,ddr3 输入时钟,所有的控制、地址信号都以 CK 交叉点为采样点,DQS 信号也是基于此信号得到

-

-

时间参数

-

tRCD,行选通指令到列选通指令的延迟,以 CK 为计量单位,指行激活指令到读写指令的最小间隔

-

CL,列选通指令潜伏期延迟,以 CK 为计量单位,指读指令到数据读出的最小间隔

-

tRP,行预充电时间,以 CK 为计量单位,指预充电指令到行激活指令的延迟

-

DDR3 常用指令

-

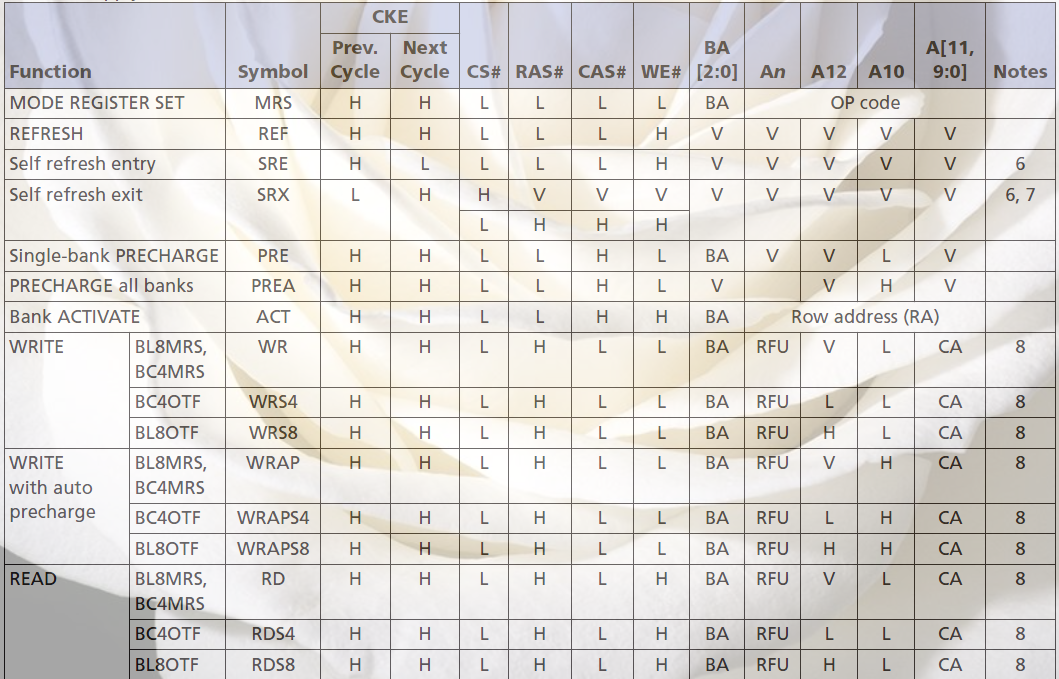

precharge

预充电指令,ddr3 换行操作时,需要先执行预充电指令,关闭当前工作行,然后再进行激活指令。地址线中的 A10 为 1,则对所有 bank 进行预充电;如果 A10 位 0,则选择 ba[2:0] 对应的bank进行预充电 -

refresh

刷新指令,ddr3 需要周期性刷新来维持存储单元中的数据,刷新指令针对所有 bank,刷新中的行指所有 bank 中地址相同的行 -

active

激活指令,用于激活某一 bank 的某一行 -

read / write

读写指令,用于对某一起始地址进行操作 -

指令表

ddr3 的指令表如下图所示。主要由 RAS#、CAS#、WE# 控制。比如刷新就是 001,写就是 100,读就是 101。表中,V 表示高电平或低电平,需要是一个确定的电平;CA 表示列地址;H 表示高电平;L 表示低电平;BA 表示 bank 地址

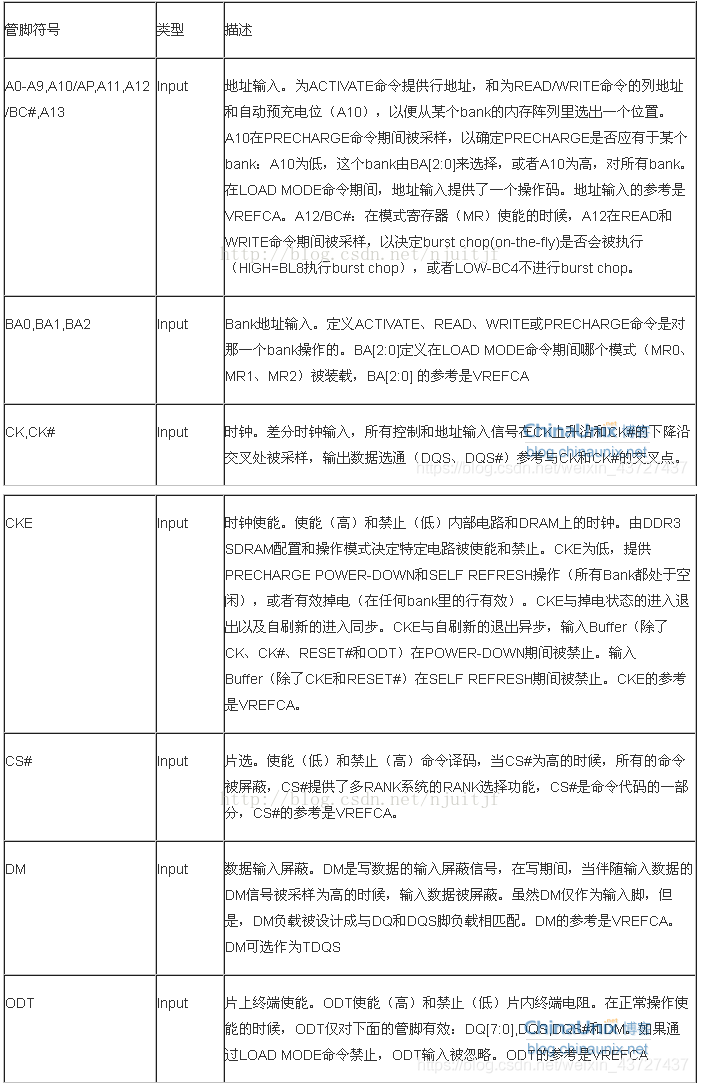

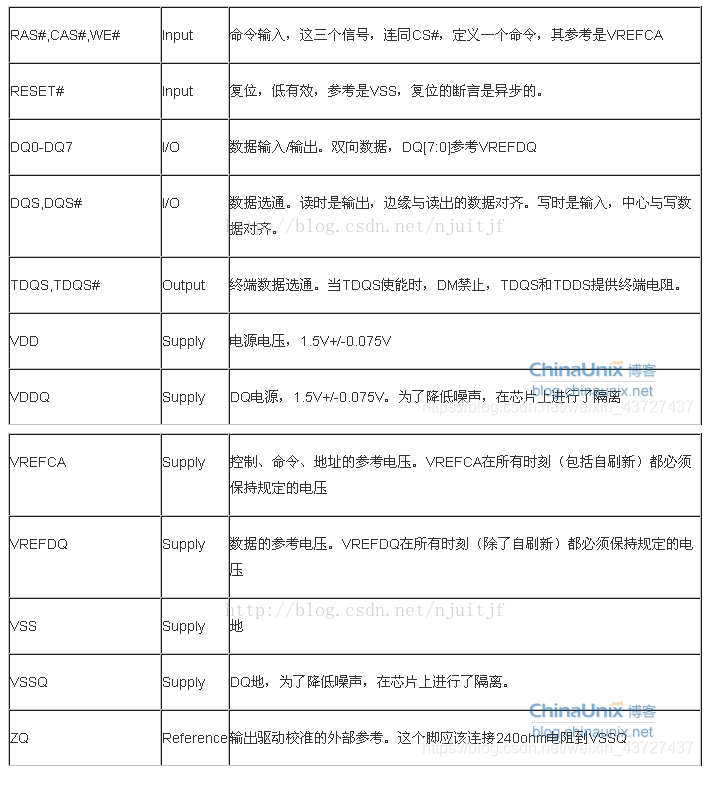

DDR3 信号说明

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?