亚稳态

说实话,这玩意我也是琢磨许久,不搞懂心里难受!!!这也让我觉得匪夷所思的地方!!!

这玩意不搞懂,我是睡不着觉的!!!!

为啥会出现亚稳态?组合逻辑有吗?组合逻辑是靠电平触发,每次会有确定的电平值0或1,但组合逻辑会有个竞争冒险现象,这个现象与亚稳态一样是个小祸害,阻碍整个系统变得优秀!!!(我这说的委婉,可能会导致系统奔溃)

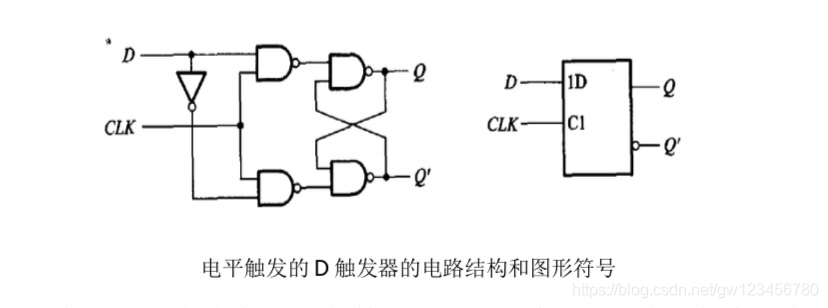

那么在时序逻辑中呢?这涉及到很重要的数字器件,那就是触发器,它具有记忆功能还可以储存一位二进制数据。为什么提到触发器呢,因为它是导火索,所有亚稳态都与它有着千丝万缕的联系。触发器工作是通过clk信号采一个值从触发器的输入D端进去,从它的输出Q端出去,并保留一个时钟周期,等待下一个周期clk采样的值从D端进来,再送到Q端,反复操作。所以说Q端的值是上一个周期采样的值。

下图是 D触发器

触发器说完,该时序逻辑了,由触发器以及其它时序器件组合成的具有一定逻辑功能的数字电路,这涉及到clk,触发器,那肯定少不了边沿触发,说了这么多,亚稳态的出现就是与边沿触发有关!!!!

一般是时钟的上升沿来对数据的采样,也就是说当时钟的上升沿采样到一个数据的渡劫区,这个是我起的名字,就是数据刚要发生变化时,时钟上升沿过来了,这时候采样就会出现迟疑,不知道是采数据之前的值还是变化后的值,这个时候就会出现不稳定的状态,不是0也不是1。不稳定最终会回到稳定,但是回到稳定的值却是随机的。

亚稳态专业定义是:当clk在采样时数据不满足建立时间和保持时间,就会产生亚稳态。

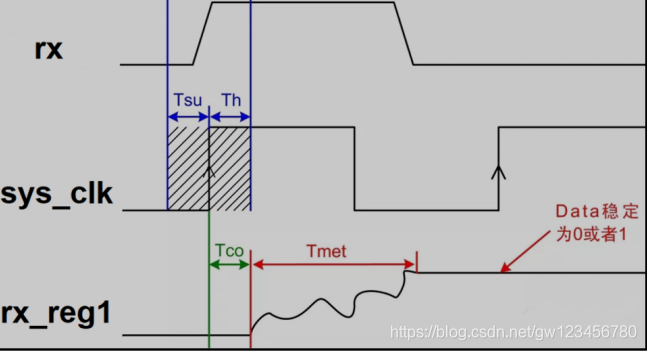

下面是关于时间参数概念:

- 建立时间(Tsu):上升沿到来之前,数据保持不变的时间

- 保持时间(Th):上升沿到来之后,数据保持不变的时间

- 寄存器内部传输延时(Tco):从D端到Q端的时间

- 亚稳态持续/振荡时间(决断)(Tmet)

下图很好的解释了亚稳态,以及解决方法:

下图取之《野火 FPGA verilog 开发指南》串口一章!

如上图,rx_reg1的值受到亚稳态的祸害,而且Tmet1的时间大于一个时钟周期,re_reg2的值取之rx_reg1的值,可以发现Tmet2的时间缩短了,小于一个时钟周期的值,所以说这是一个解决办法。

rx_reg1是对rx的值打了一拍(这是习惯讲法,实际就是延迟rx一个时钟周期),rx_reg2对rx打了两拍,可以发现,rx_reg2的值变稳态的时间缩短,到下一个时钟上升沿到来时采取的值是稳定的。

注意的是:达到稳定的值是随机的,是不可预知的,与之前输入的数据无关。

要怎么解决亚稳态呢?

其实亚稳态是解决不了的,就像误差是消除不了的一样,只能去降低误差,所以我们只能降低亚稳态发生的概率。

在FPGA中,使用一级寄存器对数据的打拍,数据稳定输出的概率为70%~80%,使用两级寄存器对输入数据的打拍,可以稳定输出99%,所以也没必要经过多级寄存器,这个方法只是针对单比特!!!

这里只是简单讲了亚稳态的部分,感兴趣同学可以自由上网查看丰富资料!!!!

1795

1795

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?