简介:

lec:等效逻辑检查logic equality check,用于检查网表在综合前后或布线前后的逻辑等价性。

S家执行LEC的工具为synopsys formality;C家执行LEC的工具为cadence conformal。

一、lec测试分类:

1、LEC:verifies systhesized and place and route netlist transformations.

2、XLEC:LEC + verifies complex datapath

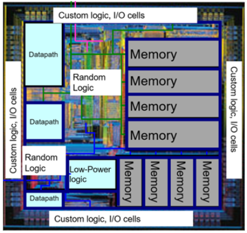

3、GXLEC:XL + verifies custom logic, I/O cells, custom memories, standard libraries + verifies final LVS netlist

target premask eco; synthesizes eco using RTL compiler.

4、low power:GXL + verifies low-power logic + verifies power domains

verifying design's power strategies and inserted power cells is Low-power validation. perform functional and structural checks on low-power logic, such as level shifters and isolation cells along with logical equivalence checking. (没看懂)

target pre- and post- mask eco; introduces physical dimension; synthesizes eco using RTL compiler physical; write physical mapping file.

5、constraint management:

SDC quality checks; formal validation of SDC exceptions; hierarchy SDC checks; Clock Domain Crossing structural and functional checks; SDC comparison

疑问记录:

datapath是什么?lec只检查core的部分?low-power logic是测什么? 为什么会需要测power domains?对应的公司flow是哪种形式?

二、lec的检查原理:

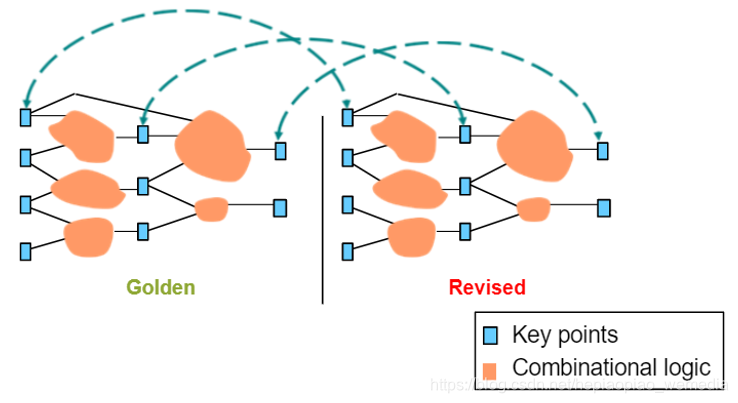

lec比较采用的是比较key point的方法。不对比combination logic。key point的比较方法包括name-base和function-base。[1]

function-base:

keypoint 包含:

primary inputs(PI), pimary outputs(PO), D flip-flops, D latches, Blackboxes, Tie-Z, Tie-E, and CUT gates. 将这些key point一一对应之后,相应的combination logic cone也会一一对应。因此通过对比每个key point获取的结果来对比combination logic的一致性。当所有的key point pair (golden key point and revised key point)所得结果都一致时,lec通过。

要说明的是,tool 是分开处理key point的input和output。即在进行lec检查的时候,key point的input不影响output。input为需要对比的值,output为需要向后传递的值。

name-base:

name-based mapping is based strictly on instance path names (or net names) of key points.

三、lec的检查流程:

(一)start mode:prepare for data

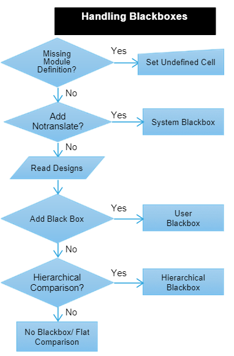

specifying blockboxes:

reading libraries and designs:

supported design formats: verilog designs; systemverilog esigns; VHDL designs; SPICE designs(XL and GXL); EDIF designs.

command: read design *.v -verilog -golden; read deisgn *.v -verilog -revised -map * -mapfile * -noelab *

supported library formats: verilog library format (standard simulation library); systemVerilog format; liberty library format. verilog library 分为有power和没有power两种,根据需要选择合适的库.

command: read library *.v -verilog -revised -append *

specifying design constraints:

design constraints are user inputs that control part of a design's logic. constraints could do these things: exclude sections of a design from verification; specify behavior; specify relationship; constrain internal nets; constrain instances; constrain feedback.

specifying modeling directives:

针对design中的一些特殊设计进行约束

(二)lec mode:run compare

mapping process

SET MApping Method [-name first | -name only | -name guide | -noname] #mapping method

write mapped points <map_file>

read mapped points <map_file>resolving unmapped key points

compare process

add compare points -all

compare

report verification -verbosedebugging nonequivalent key points

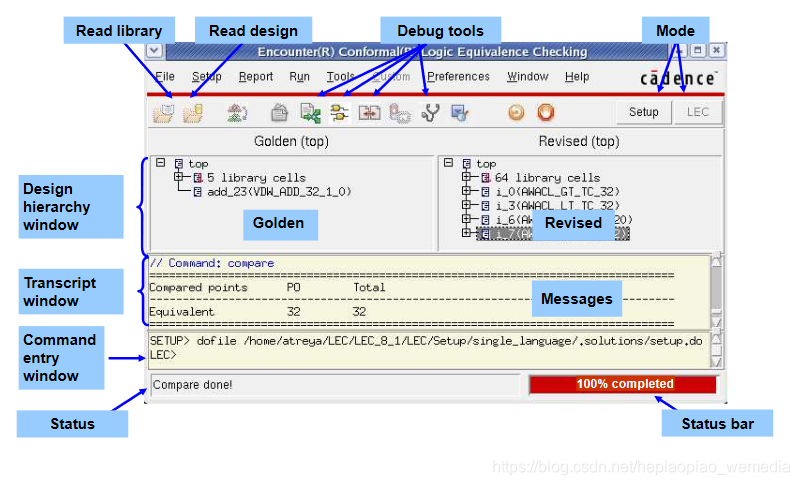

gui界面:

some command will help to use lec:

checkpoint: save all the dat from a session as a checkpoint, and is can be restarted at a later time.

checkpoint LEC.ckpt -replace

exit -f

lec -restart_checkpoint LEC.ckptswith mode:

set system mode [setup | lec]generate command template:

write template -Outfile ...

2757

2757

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?