RFSOC XCZU47DR 高速ADC DAC模块卡

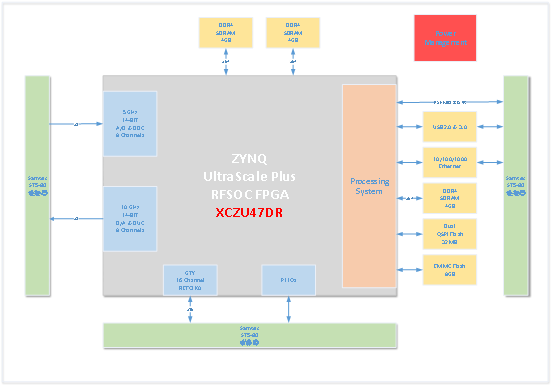

RFSOC核心模块使用Xilinx最新的第三代RFSOC系列XCZU47DR,1517封装,单颗芯片包含8路ADC和DAC,64-bit Cortex A53系列4核CPU,Cortex-R5F实时处理核,以及大容量FPGA。

北京太速科技核心板采用SAMTEC高速连接器,支持高速ADC和DAC,也可以支持GTY,GTR等高速信号的连接需求。

特性:

- Zynq RFSoC系列FPGA,支持8路最高5G 14-bit ADC和8路最高9.85G 14-bit DAC

- PL 2组64bit 2400M DDR4,支持PL部分高速存储和处理。 单组4GB字节容量,PL部分8GB字节容量。

- PS部分1组64bit位宽DDR4,单组4GB字节

- 单独5V-14电源供电

- 可配置的Dual QSPI 加载

- 支持MicroSD卡加载

- 1000Base-T以太网

- USB接口支持

- 支持外部时钟输入

设计规格:

- 平台规格

- 处理器:ZynqUltraScale+ RFSOC Gen3

- 存储

- PS,64bit DDR4 2400M

- PL,2组 64bit DDR4 2400M

- PS,2片QSPI Flash,并行x8结构

- PS,MicroSD(连接器)

- PS,EMMC 8GB,板内文件存储

- PS,SATA 6G(连接器)

- PS,NVMe PCIe(连接器)

- 高速接口

- 8 ADC,14bit 5GSPS

- 8 DAC,14bit 9.85GSPS

- x2 QSFP28(100G,底板)

- PCIe x8 Gen4

- 其他接口

- x1 10/100/1000以太网

- x1 USB 3.0

- x1 USB-JTAG

- 灵活时钟输入输出

- 核心板提供PS常用时钟,GTR时钟

- 核心板内提供GTY refclk0常用时钟

- 核心板提供ADC和DAC常用PLL

- GTY refclk1连接至连接器

- GTR 2路参考时钟至连接器

- PL参考时钟到连接器

2578

2578

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?