FPGA和clk相关的BUFG、BUFIO、BUFR

1)BUFR是区域时钟缓冲器,要进入区域时钟网络,必须例化BUFR。

2)bufg和bufr都要ccio驱动包括bufg。(clock capable io)。普通io无法驱动bufg和bufr。

3)一个design,如果不例化bufg,或者bufr,直接定义一个input clk,则会在综合阶段自动插入bufg。

4)一个design的时钟,不仅可以由bufg驱动,也能由bufr和bufio驱动。

5)ccio = MRCC + SRCC.

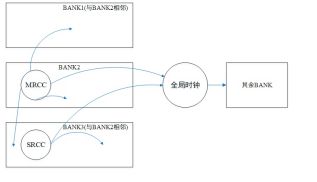

看下面这个图,首先MRCC和SRCC都是可以连接到全局时钟的,但是全局时钟的资源有限。如果程序较大都使用全局时钟的话,那时钟资源就不够用了。SRCC可用于本区域时钟这个比较好了解,MRCC用于相邻的区域该这么理解,MRCC通过不同于全局时钟的渠道可以到达相邻的区域。虽然通过手册可以看到芯片的各个区域分布,但是这个还是最好交给EDA自己优化。如下图BANK1和BANK3可以使用BANK2的MRCC分上来的时钟,没必要先将BANK2的MRCC连接到全局时钟再连接到BANK1和BANK3,这样不但节省了全局时钟资源,而且路径更短。

另,文章引用:

Xilinx 7 Series FPGA时钟网络的区别(BUFG,BUFGR,BU

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4374

4374

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?