原文链接:https://hackmd.io/@kaY0TZGmReqh1uwlnjZV8w/BJHBqY0oL

RISC-V 有一個機制叫 Physical Memory Protection(PMP), 他是用來保護實體記憶體的一種機制,原文中描述:

留言

An optional physical memory protection (PMP) unit provides per-hart

machine-mode control registers to allow physical memory access

privileges (read, write, execute) to be specified for each physical

memory region.

這說明他是一種 optional mechanism 透過 program Machine Mode(M-mode) CSR 來達成的記憶體的保護(read, write, execute)。

原文中分為幾個部份來介紹:

- PMP CSRs

- Address Matching

- Locking and Privilege Mode

- Priority and Matching Logic

- Physical Memory Protection and Paging

這裡只針對 Physical Memory 解釋,暫時忽略 virtual memory and paging 也就是第五點暫時不探討。

PMP CSRs

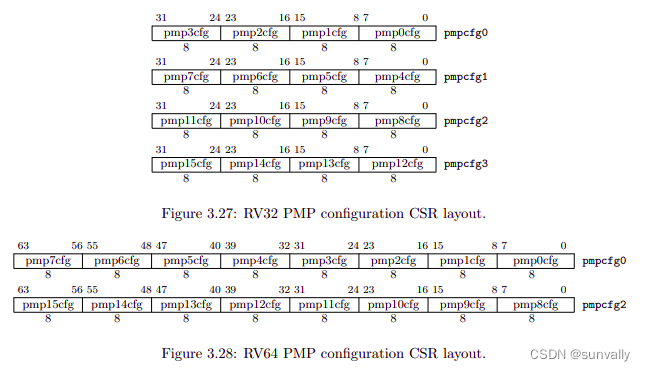

PMP entries are described by an 8-bit configuration register and one MXLEN-bit address register.

PMP entry 是由 pmpcfg# 和相對應的 pmpaddr# 所組成

如圖,RV32 的 pmpcfg# 是有 4 組 8 bits 的 fields 所組成的,每一個 pmpcfg 都有其相對應的 pmpaddr。然而在 RV64 中,則是將 pmpcfg[0-7] 視為 pmpcfg0,pmpcfg[8-15] 為 pmpcfg2(在 RV64 中 pmpcfg[1/3] 是違規的)。

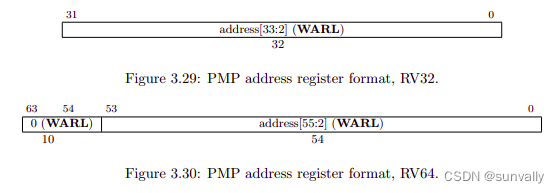

RV32 中的 pmpaddr 以 32 表示 2-34 bint 的位址,RV64 則是 54 bits 來表示 2-55 bit 的位址,這是為了 virtual memory implementation。

所以表示在 32 bits 的實體位址中 program 時常常需要將 address >> 2 在放入 pmpaddr 中。

Address Matching

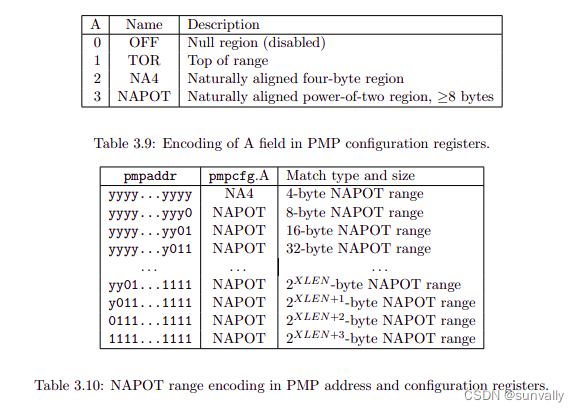

pmpcfg 和 pmpaddr 可以規範地址範圍,pmpaddr 設定位址,pmpcfg 中的 A 用來設定範圍:

- NA4 表示 yyyy…yyyy 開始的 4 bytes

- NAPOT 表示連續幾個 1 的 power of 2 且要大於等於 8 bytes,所以它其實就是2^3 * 2 ^ 連續 1 的個數次方,而 base 是從將連續的 1 都轉為 0 的地方

- e.g. yyyy … y011 => base = yyyy … yy000。

- TOR 如果 pmpcfg[i] 的 A 設成 TOR => 表示規範 pmpaddr[i - 1] <= addr < pmpaddr[i], 如果 i == 0 則規範 addr < pmpaddr0 的範圍。

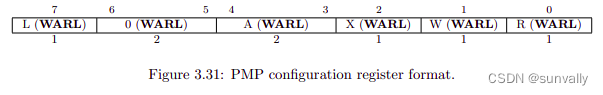

Locking and Privilege Mode

The L bit indicates that the PMP entry is locked, i.e., writes to the

configuration register and associated address registers are ignored.

Locked PMP entries remain locked until the hart is reset.

接下來就是 L bit

When the L bit is set, these permissions are enforced for all

privilege modes. When the L bit is clear, any M-mode access matching

the PMP entry will succeed; the R/W/X permissions apply only to S and

U modes.

L 可以視為用來規範符合 Range 的 (R/W/X) 操作,L bit 被設起來後,這個 pmpcfg 就被鎖住,任何對這個 entry(pmpcfg + pmpaddr) 的寫入都會被忽略,直到下一次 reset。另外如果 L 被設起來連在 M-mode 下都要遵守 pmpcfg 的 (R/W/X) 權限,如果 L 為 0, 則 M-mode 可以自由寫入但 S/U mode 依然要遵行 (R/W/X) 的設定。

Priority and Matching Logic

PMP entries are statically prioritized. The lowest-numbered PMP entry

that matches any byte of an access determines whether that access

succeeds or fails. The matching PMP entry must match all bytes of an

access, or the access fails, irrespective of the L, R, W, and X bits.

pmp entries 有優先權的,number 越小的優先權越高,如果 access 符合 entry0 (pmpcfg0 + pmpaddr0) 的範圍,則該 entry 的設定可以決定 access 的成功與否,而每一次 access 都要符合 pmp entry 的範圍,如果不符合直接 access fail 不管(L/R/W/X)。

If no PMP entry matches an M-mode access, the access succeeds. If no

PMP entry matches an S-mode or U-mode access, but at least one PMP

entry is implemented, the access fails.

如果所 access 的位址沒有被任何 pmp entry 規範到,只有在 M mode 下 access 會成功,S/U mode 下都會失敗。

這裡要注意到:只要有一個 pmp entry 被 programed,所有 entry 都會被視為有效(A 預設為 OFF)。

Reference

https://content.riscv.org/wp-content/uploads/2017/05/riscv-privileged-v1.10.pdf

tags: risc-v pmp physical memory protection

本文详细介绍了RISC-V架构中的物理内存保护(PMP)机制,包括PMPCSR的使用、地址匹配规则、锁定与权限模式、优先级逻辑以及PMP在不同模式下的行为。特别关注了RV32和RV64架构中的PMP配置差异。

本文详细介绍了RISC-V架构中的物理内存保护(PMP)机制,包括PMPCSR的使用、地址匹配规则、锁定与权限模式、优先级逻辑以及PMP在不同模式下的行为。特别关注了RV32和RV64架构中的PMP配置差异。

817

817

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?