SOC架构篇

开始之前,我们首先来看一下什么是时钟门控(clock gating)技术,顾名思义就是利用逻辑门技术控制时钟的通断。

那么为什么需要控制时钟的通断呢?主要基于以下几个原因。

首先,随着工艺的发展和设计规模的增大,时钟树上产生的功耗占整个SoC功耗的比例越来越高,有时几乎能占到50%左右。

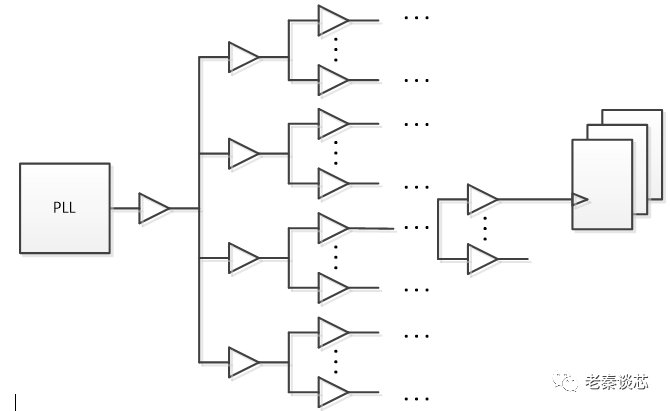

关于时钟树,可能前端的同学不熟悉,简单说几句,SoC的时钟一般是参考时钟经过PLL和数字分频器输出的,后面可能要连接驱动成千上万的寄存器clock端。

这时候任何一个单一的cell都不可能有这么大的驱动能力,因此要插入大量的buffer,而且为了保证到每个寄存器的延时一样,clock tree还要做balance。整个的时钟树大概长成下图这样,

- 第一级buffer叫root,

- 中间的buffer叫branch,

- 最后一级的buffer叫leaf(做技术的起名字就是这么简单,粗暴,易懂图片):

如果我们的芯片在不工作时,PLL依然有clock输出的话,那整个时钟树依然产生很大的功耗。

接下来我们再看一下边沿触发器的结构图。从图上我们能看出即使D端保持不动,clock端变化也会消耗一些能量。想深入研究的同学可自行推导(可以忽略两个复位信号&#

订阅专栏 解锁全文

订阅专栏 解锁全文

2849

2849

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?