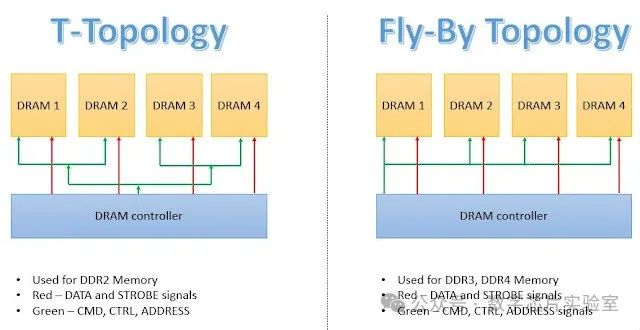

内存条DIMM的容量和速度一直在提升。从DDR3到DDR4再到DDR5,工程师们面临的最大挑战是:如何防止高频信号干扰。今天我们来详细了解DDR4开始采用的Fly-by布线技术,看看它解决了哪些实际问题。

一、传统T-topology布线的高频问题

早期DDR3内存普遍使用T-topology布线。这种方式像树枝一样,把信号同时分发到多个内存颗粒。在低频环境下还能正常工作,但当频率升高就会出现严重问题:

-

时序不一致:电信号在PCB上传播速度约为光速的60%(18cm/ns)。DDR4-3200的时钟周期只有0.625ns,如果两条分支线路长度相差1cm,信号到达时间就会差0.05ns,占整个时钟周期的8%。这导致数据采样错位。

-

信号反射:每个分叉点都会产生信号反射,就像声波在墙壁间反弹。当频率超过2000MHz,这些反射波会与原始信号叠加,造成严重的signal integrity问题,具体表现为波形畸变、眼图闭合等。

-

布线复杂:设计师必须确保每条分支长度完全相同,这在多层PCB设计中非常困难,特别是对于8颗粒以上的高密度内存条。

二、Fly-by布线的工作原理

5951

5951

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?